运算方法和运算器

2020-03-06 14:10

1711 查看

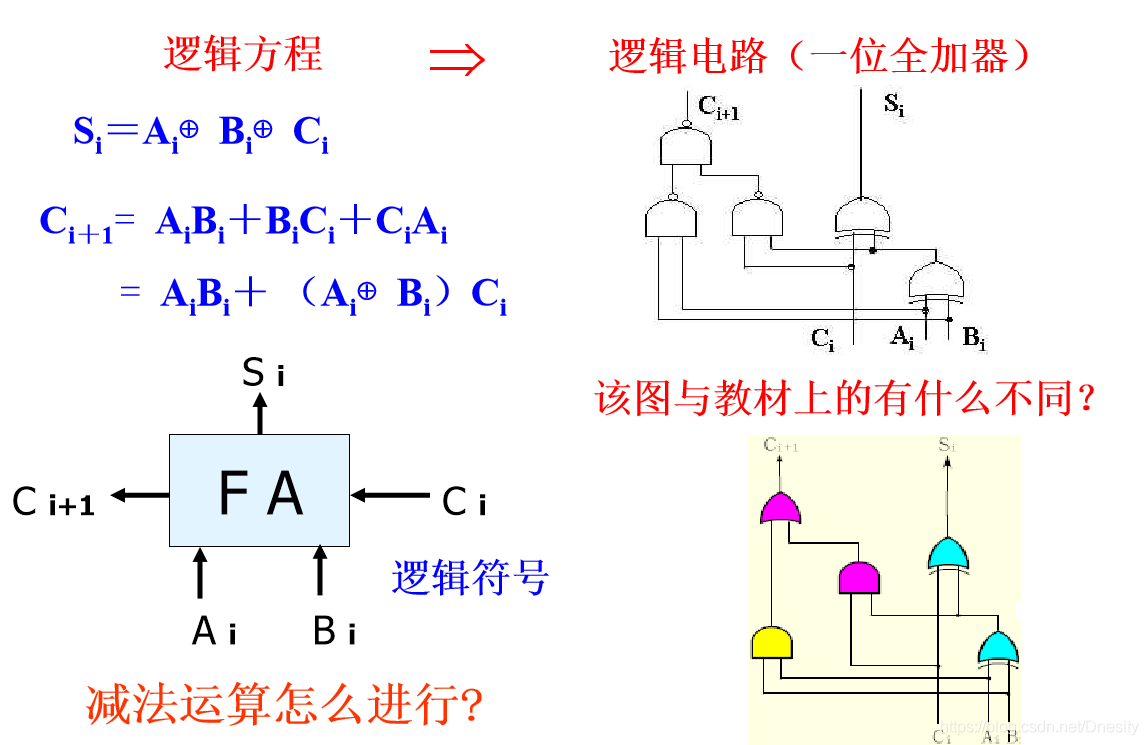

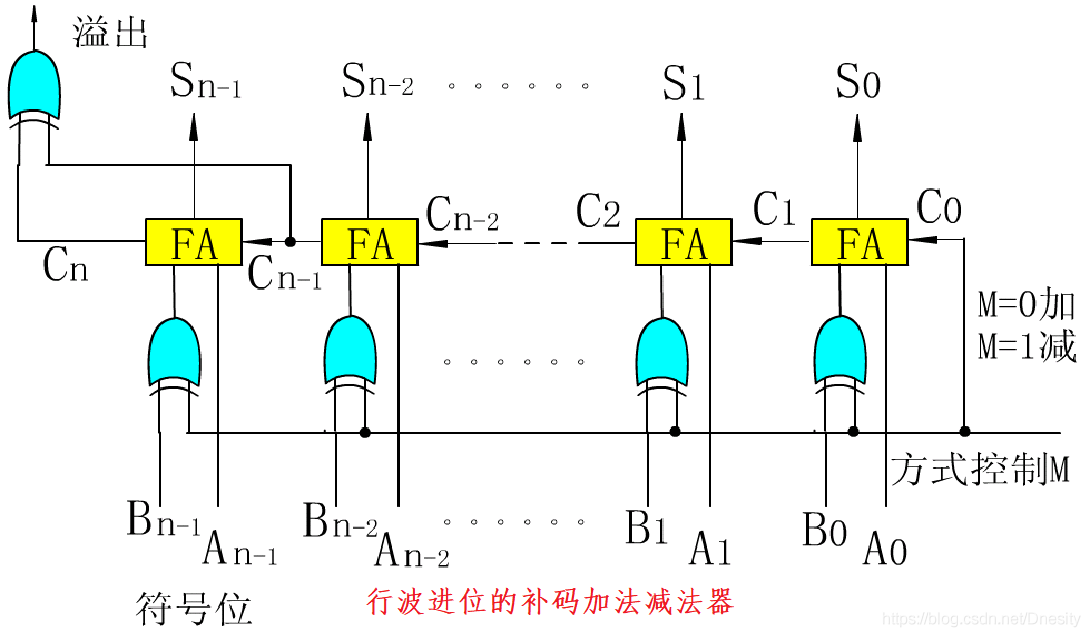

一、基本的二进制加法/减法器

半加器

不考虑进位

不考虑进位

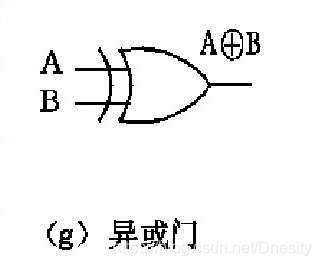

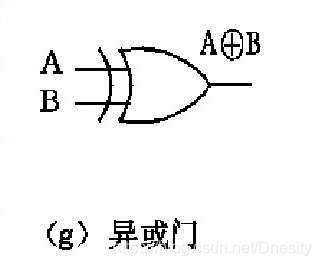

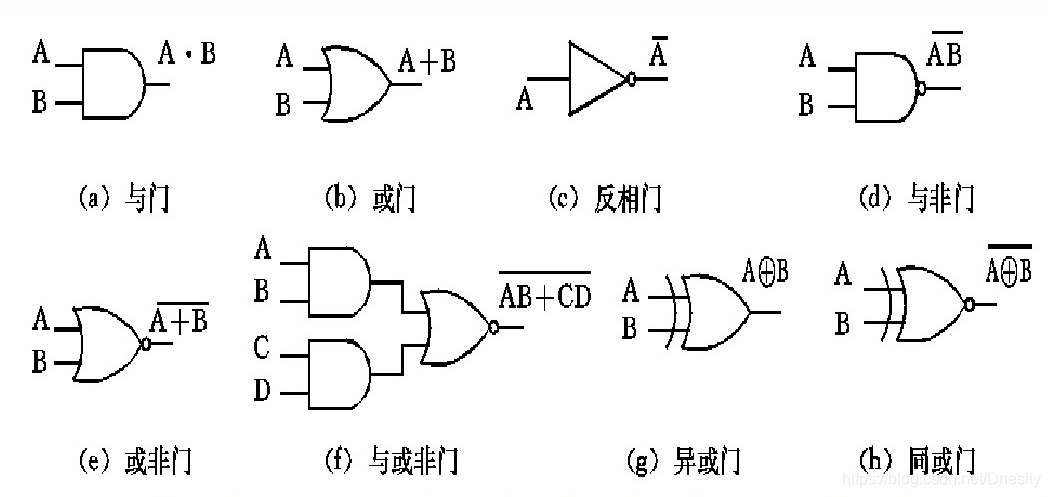

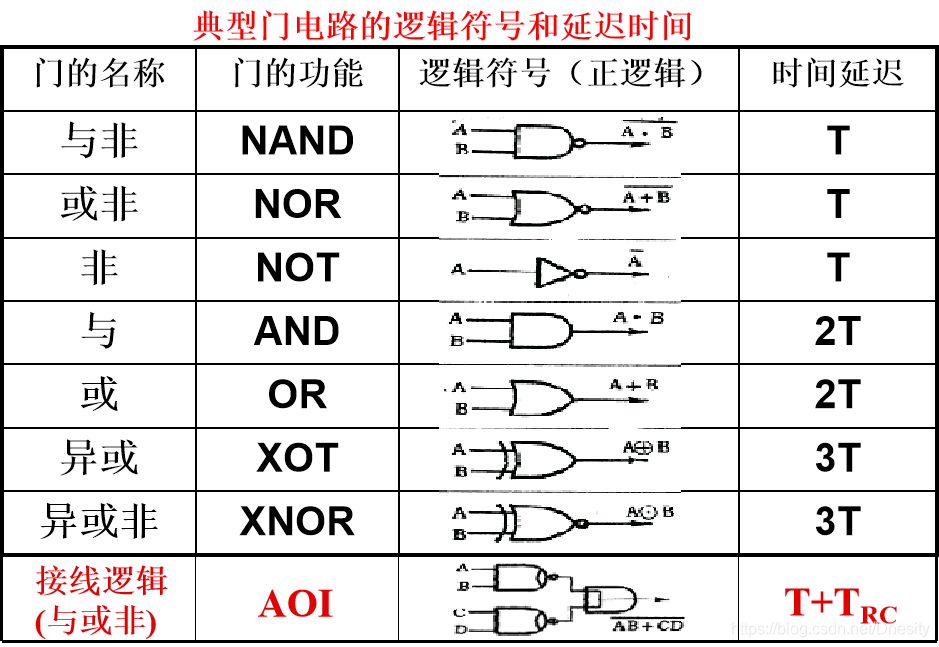

各种逻辑门的图形符号

各种逻辑门的图形符号

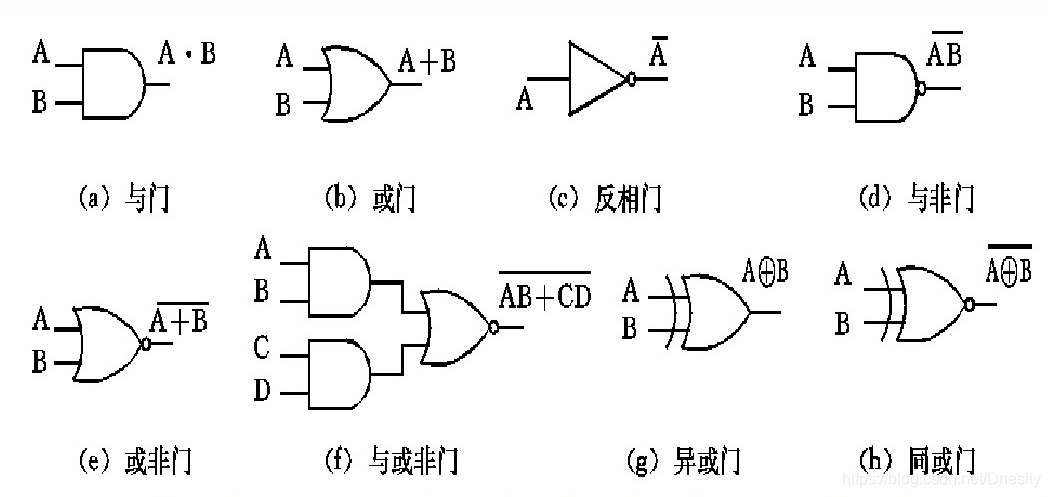

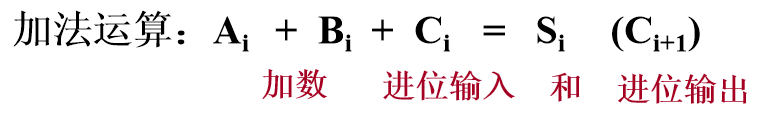

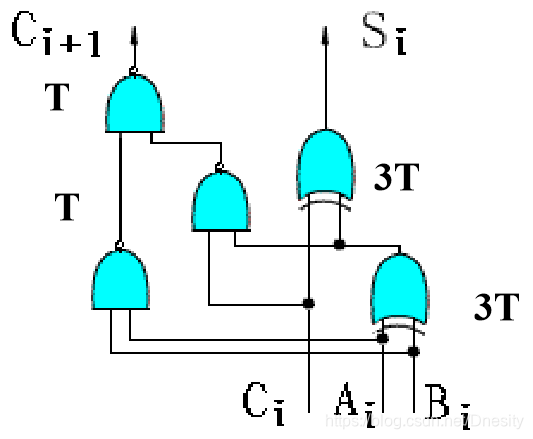

1.一位全加器

1.一位全加器

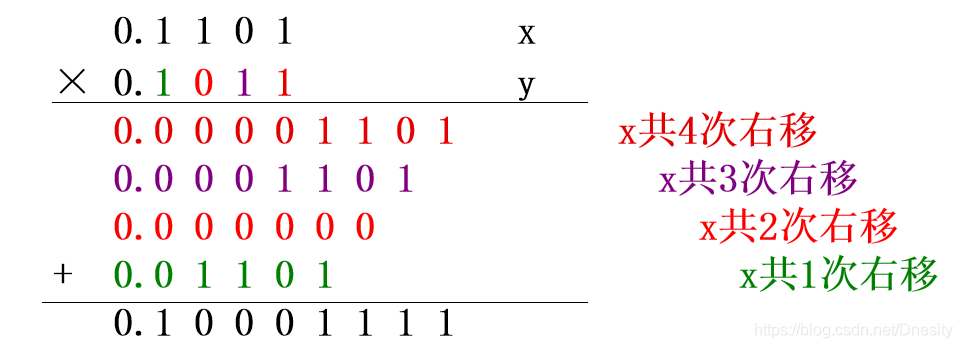

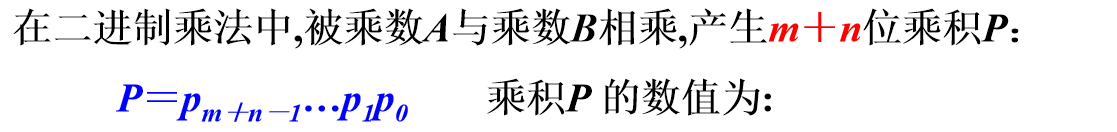

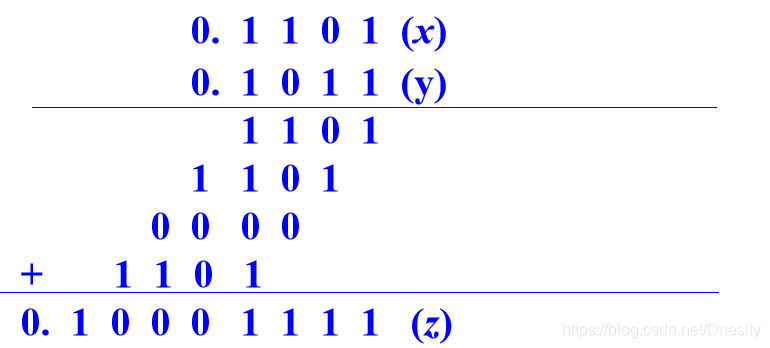

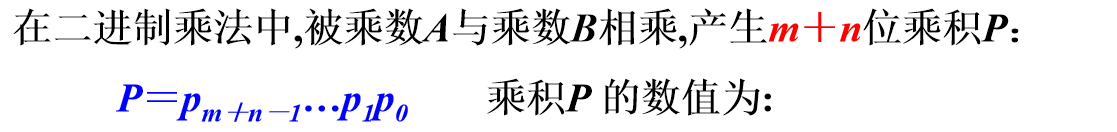

机器与人们习惯的算法不同之处:

(1) 机器通常只有n位长, 两个n位数相乘, 乘积可能为2n位。

(2) 只有两个操作数相加的加法器难以胜任将n位积 一次相加起来的运算。

2.适合定点机的形式

机器与人们习惯的算法不同之处:

(1) 机器通常只有n位长, 两个n位数相乘, 乘积可能为2n位。

(2) 只有两个操作数相加的加法器难以胜任将n位积 一次相加起来的运算。

2.适合定点机的形式

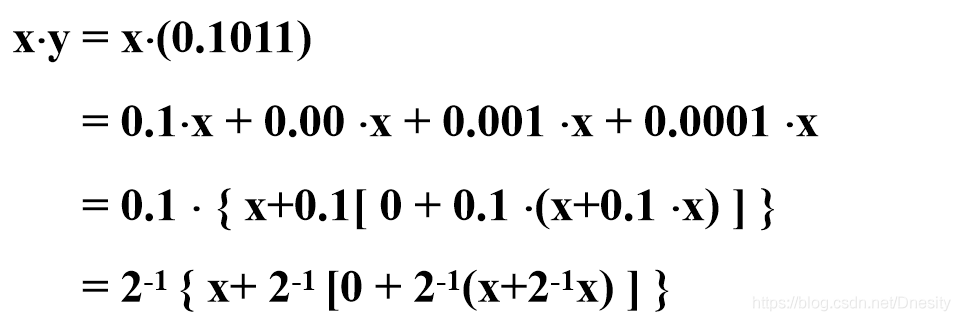

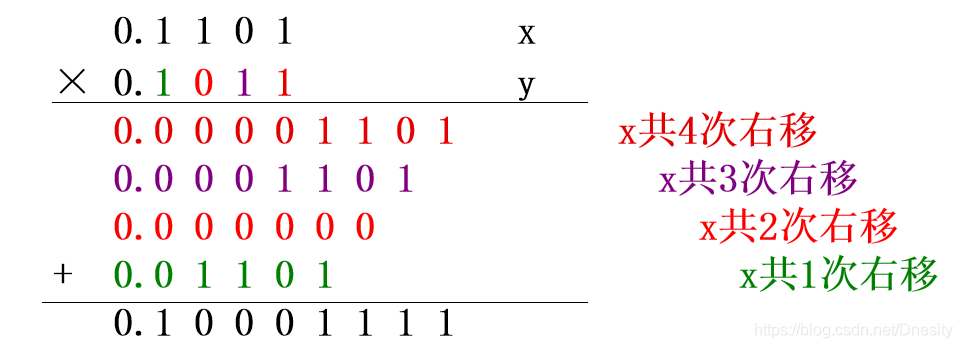

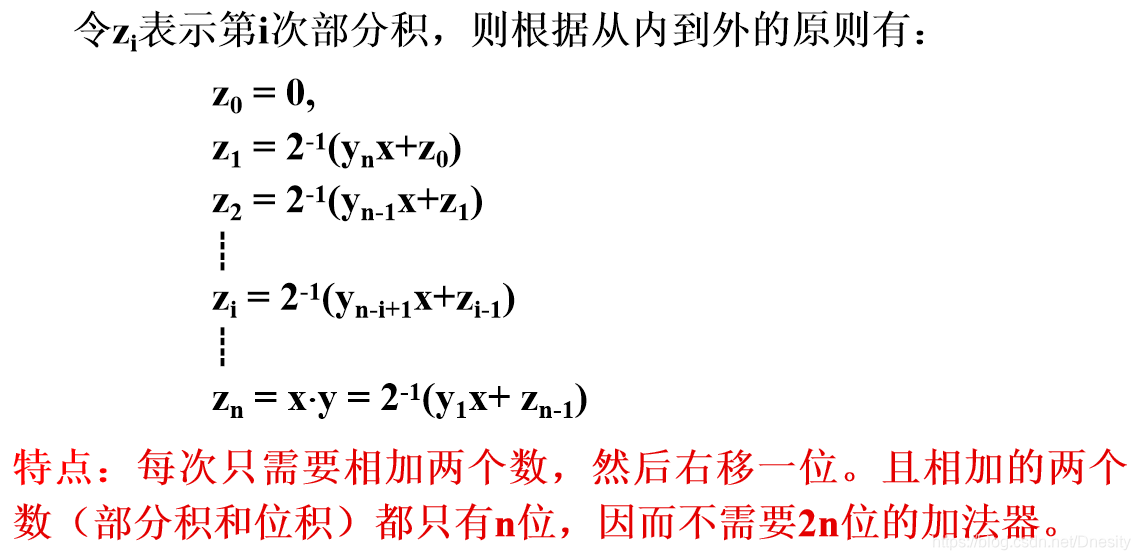

为了适合两个操作数相加的加法器,将 x·y 改写成下面形式:

为了适合两个操作数相加的加法器,将 x·y 改写成下面形式:

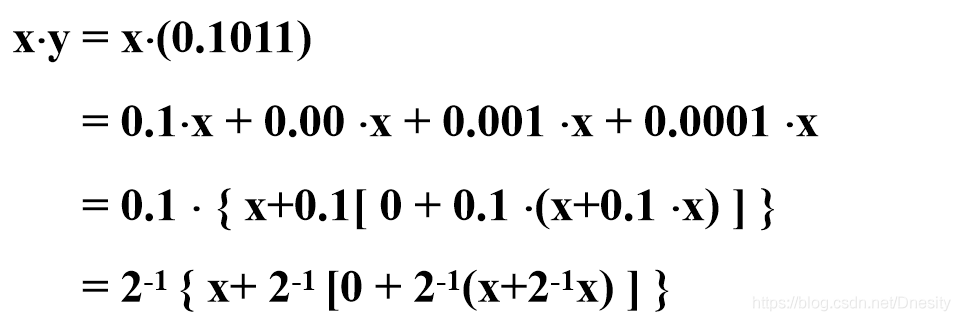

根据此式,按式中括号可表达的层次,从内向外逐次进行移位累加。

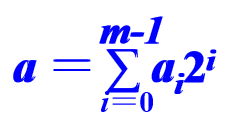

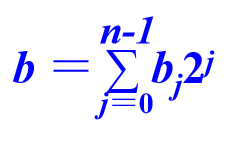

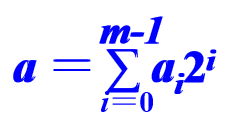

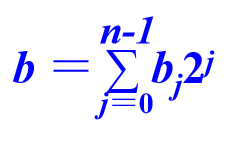

一般而言,设被乘数x,乘数y都是小于1的n位定点正数:

x=0.x1x2......xn <1

y=0.y1y2......yn <1

根据此式,按式中括号可表达的层次,从内向外逐次进行移位累加。

一般而言,设被乘数x,乘数y都是小于1的n位定点正数:

x=0.x1x2......xn <1

y=0.y1y2......yn <1

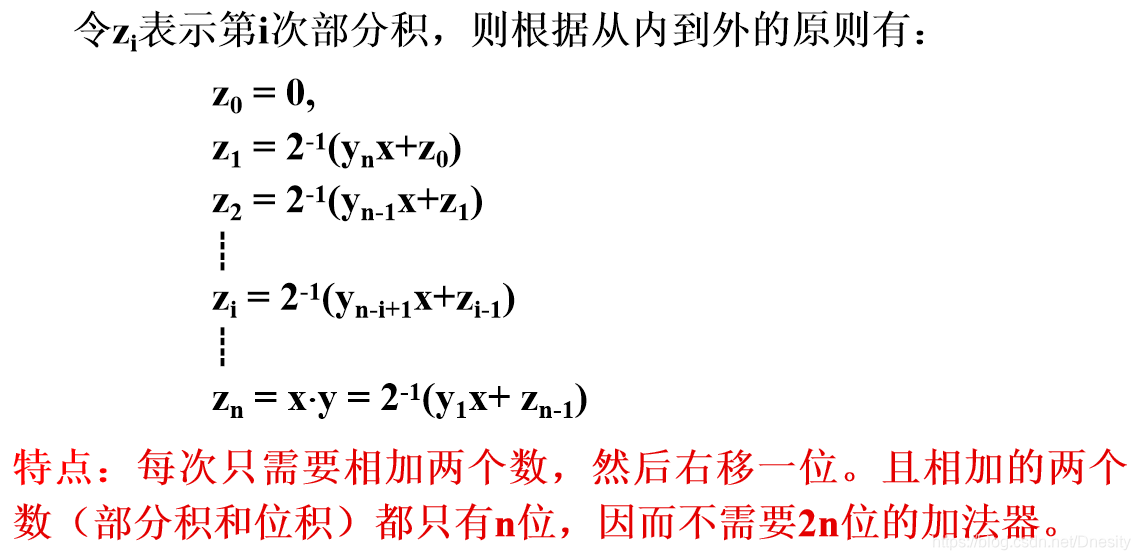

形成递推公式

形成递推公式

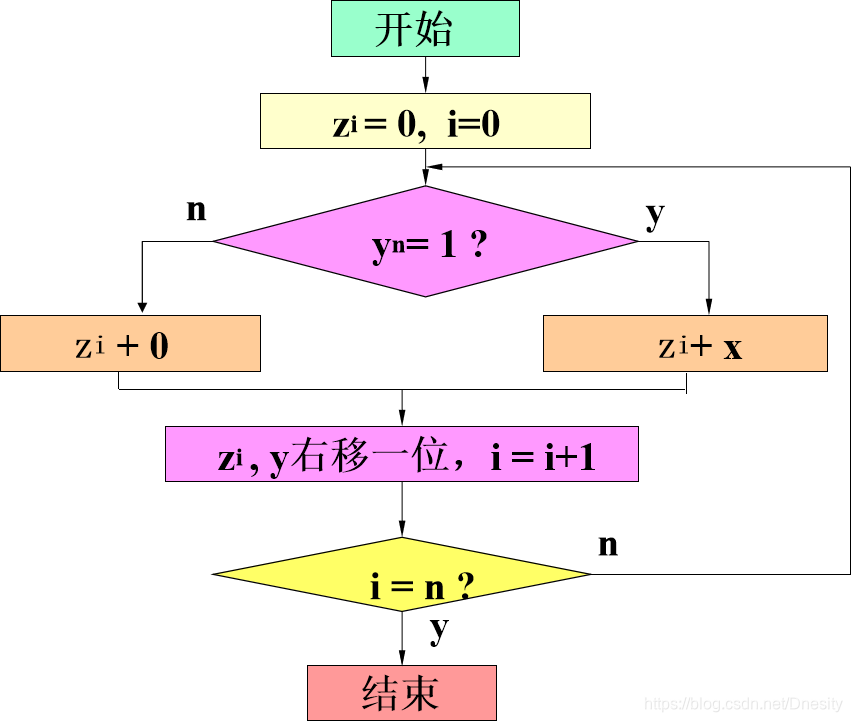

3.原码一位乘法流程图

3.原码一位乘法流程图

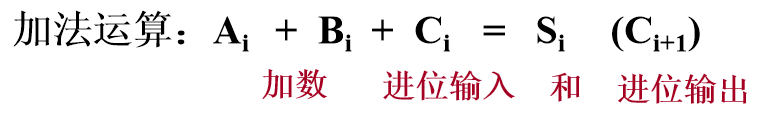

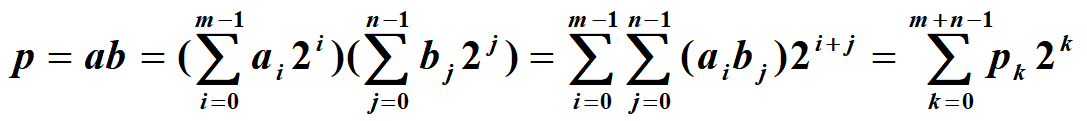

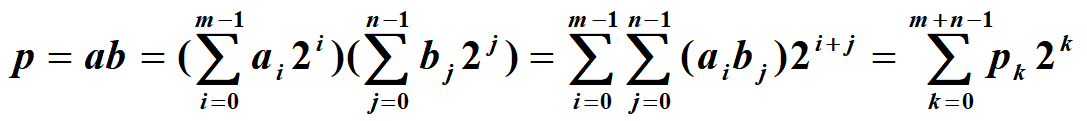

(1) 习惯方法运算过程:

(1) 习惯方法运算过程:

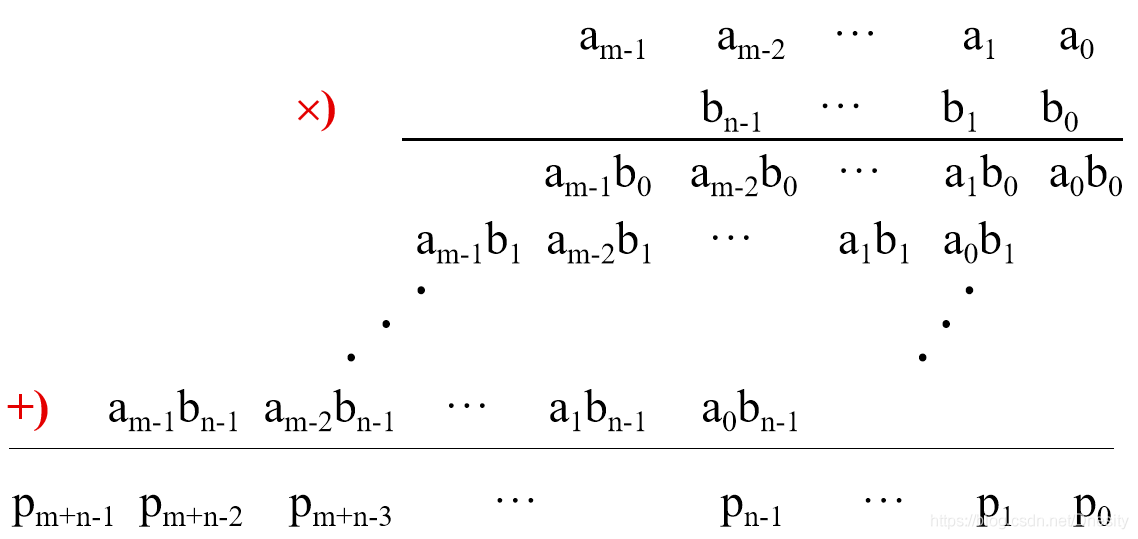

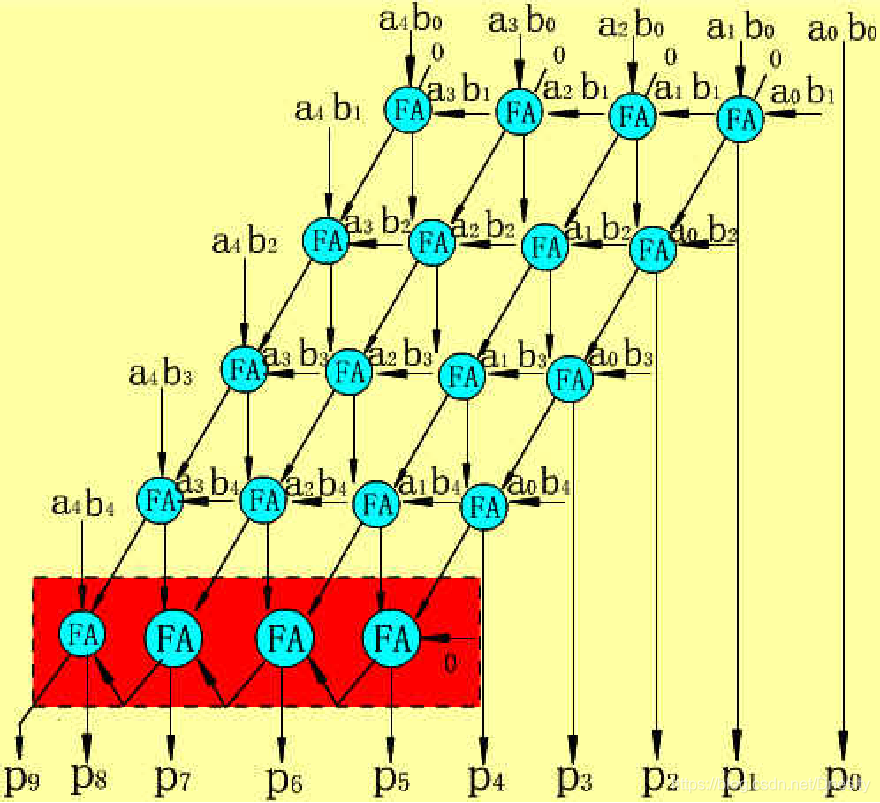

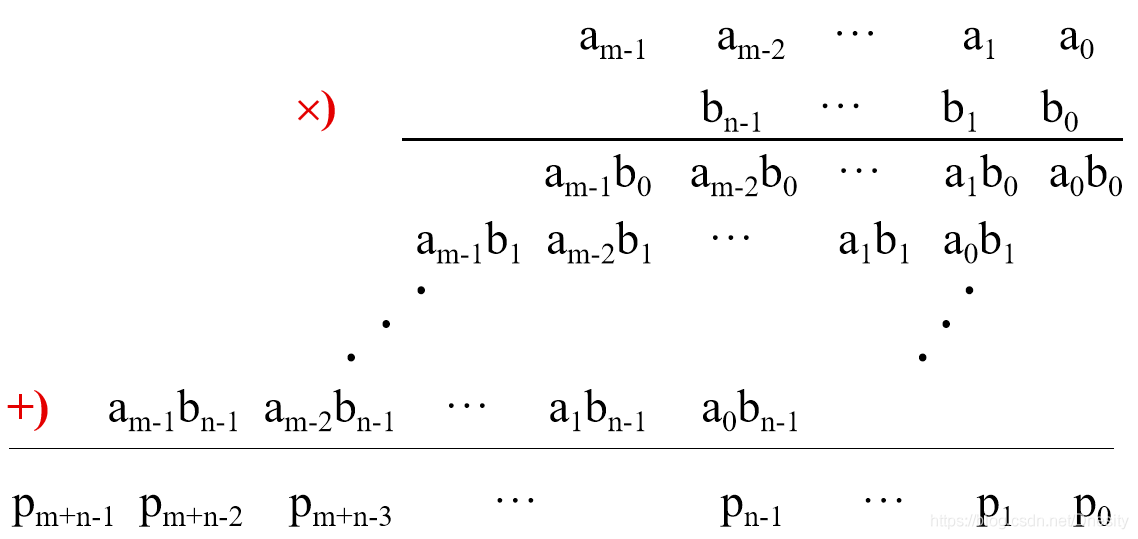

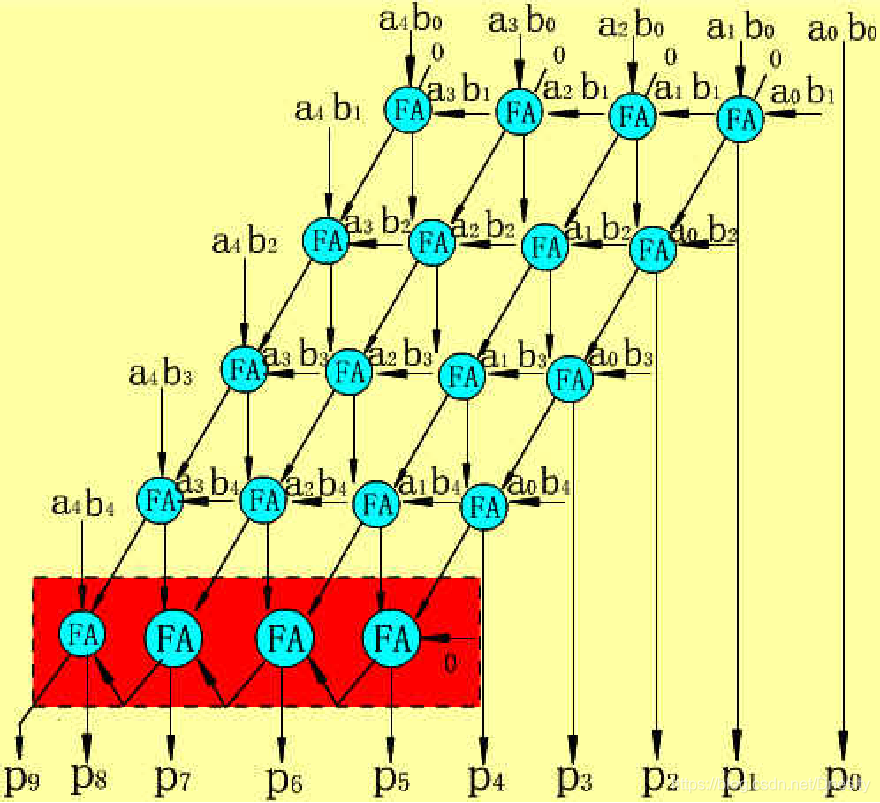

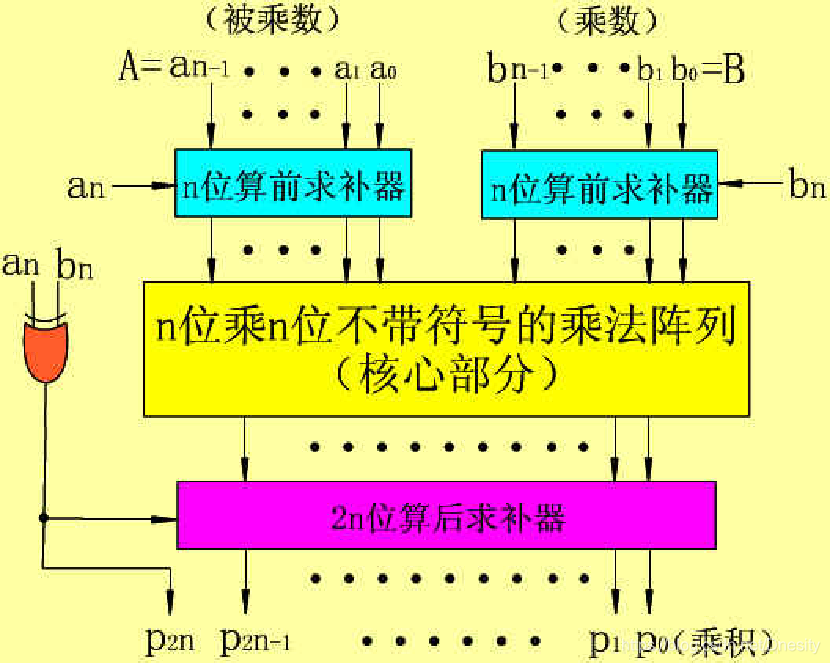

(2) 不带符号阵列乘法器逻辑框图

(2) 不带符号阵列乘法器逻辑框图

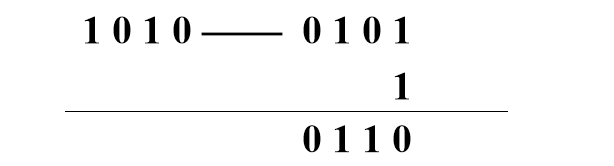

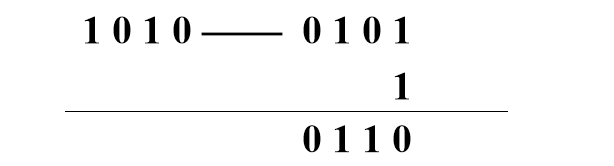

例2: 对1011求补。

例2: 对1011求补。

方法:从数的最右端a0开始,由右向左, 直到找出第一个“1”,例如ai=1, 0≤i≤n。这样, ai以左的每一个输入位都求反, 即1变0, 0变1。

方法:从数的最右端a0开始,由右向左, 直到找出第一个“1”,例如ai=1, 0≤i≤n。这样, ai以左的每一个输入位都求反, 即1变0, 0变1。

2.机器运算与手算的不同

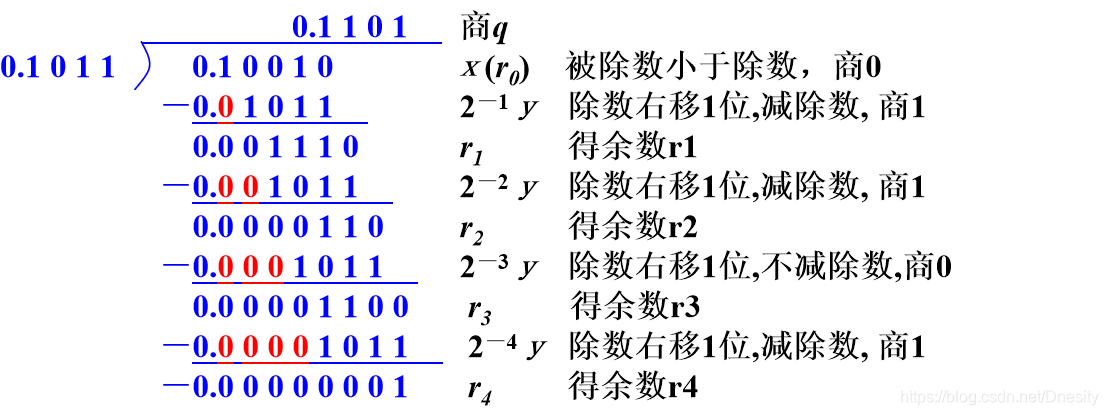

原码一位除法

2.机器运算与手算的不同

原码一位除法

结果与手算相同,但余数不是真正的余数,多乘了2n,故正确的余数应为2-n×rn,即:0.00000001

(1) 在计算机中,小数点是固定的,不能简单地采用手算的办法。为便于机器操作, 除数Y固定不变, 被除数和余数进行左移 (相当于乘2)。

(2) 机器不会心算,必须先作减法,若余数为正, 才知道够减;若余数为负, 才知道不够减。不够减时必须恢复原来的余数, 以便再继续往下运算。这种方法称为恢复余数法。

(3) 要恢复原来的余数, 只要当前的余数加上除数即可。但由于要恢复余数, 使除法进行过程的步数不固定, 因此控制比较复杂。

实际中常用不恢复余数法,又称加减交替法。其特点是运算过程中如出现不够减,则不必恢复余数,根据余数符号, 可以继续往下运算,因此步数固定,控制简单。

3.恢复余数法

被除数减除数,够减时,商1;不够减时商0。

由于商0时若不够减,即不能作减法,但现在在判断是否商0时,已经减了除数,为了下次能正确运算,必须把已减掉的除数加回去恢复余数。这就是“恢复余数法”。

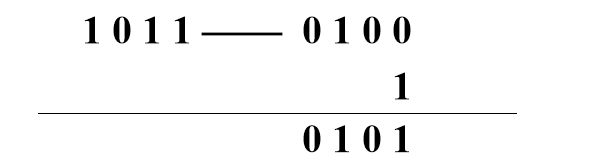

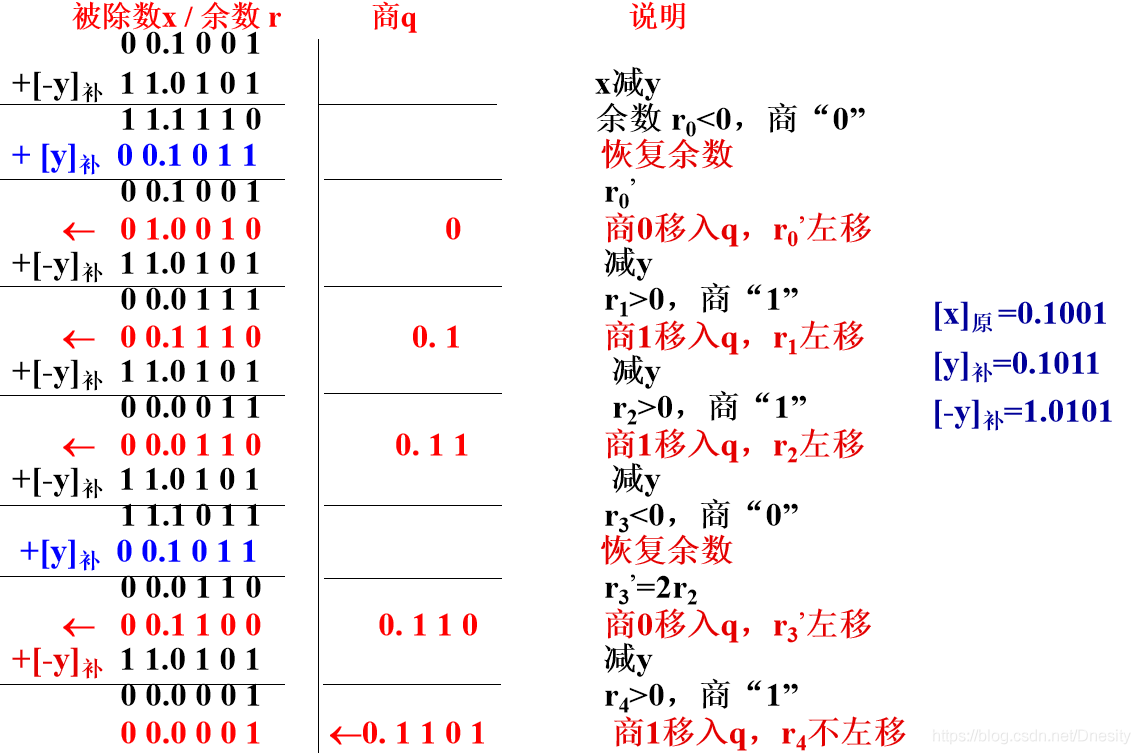

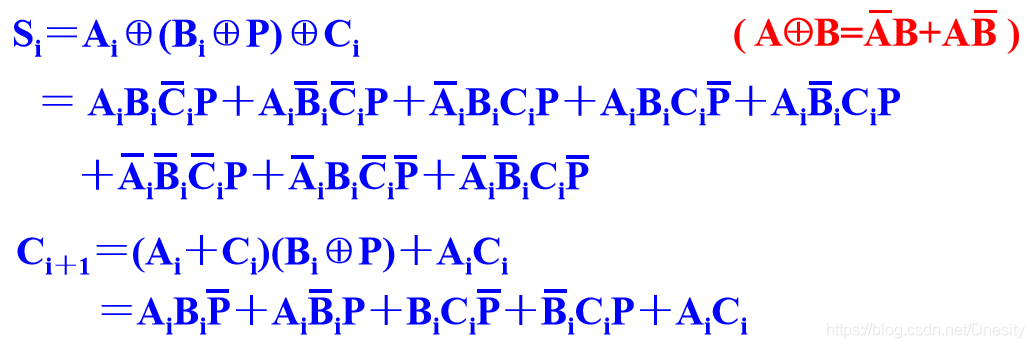

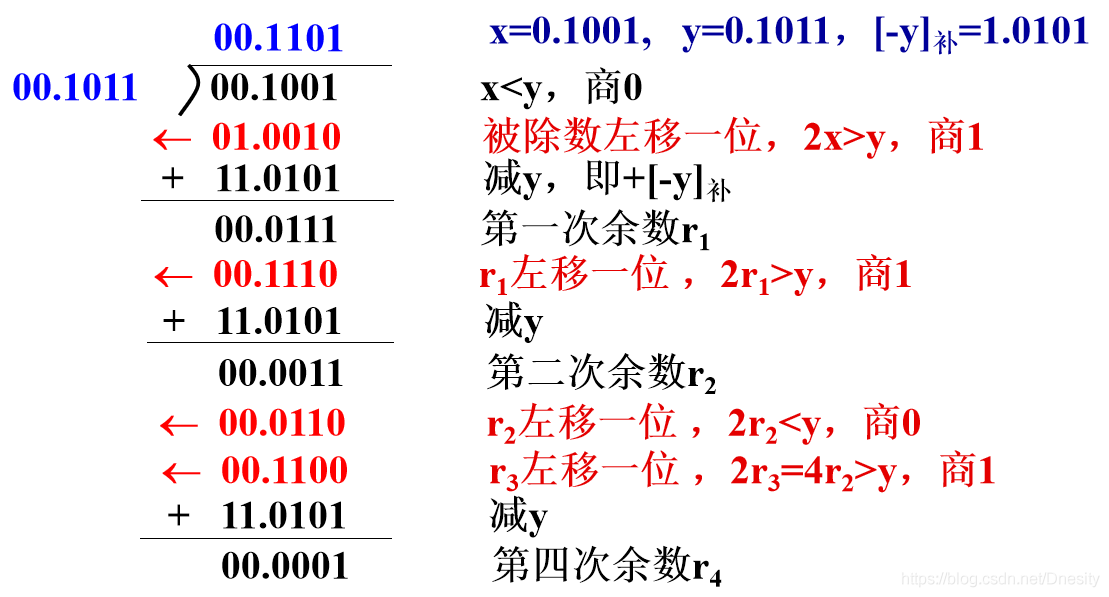

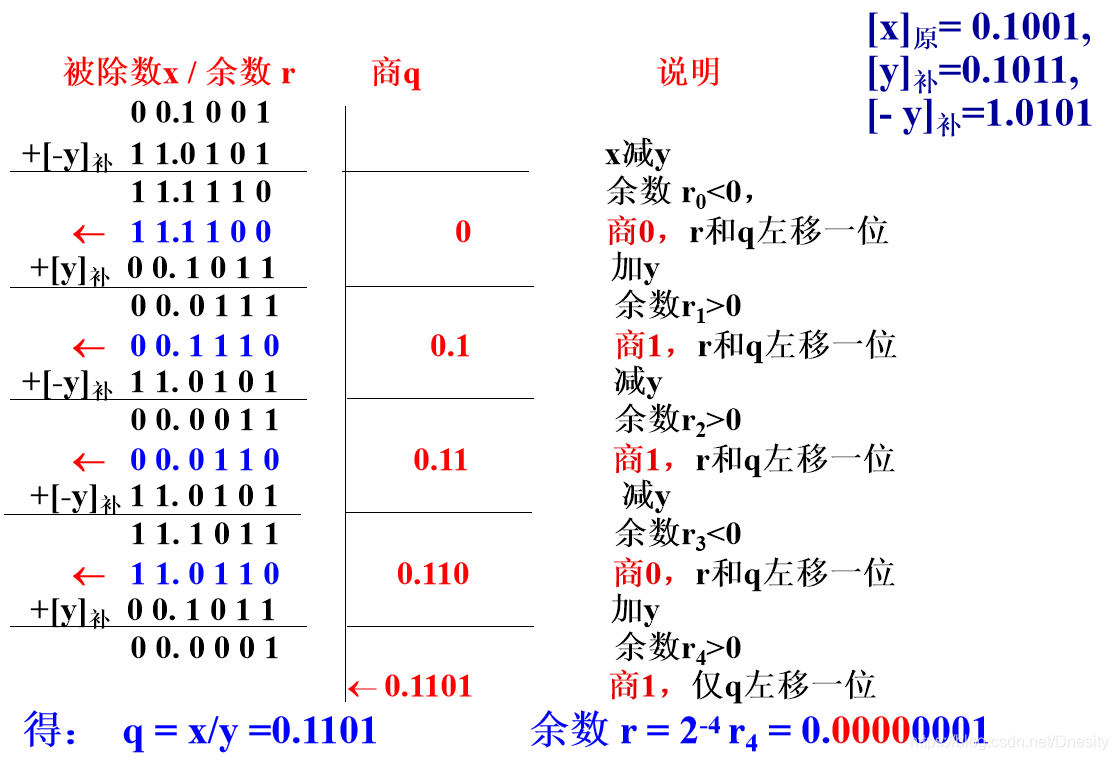

【例1】x=0.1001, y=0.1011, 用恢复余数法求 x/y。

解:[x]原 =[x]补= x=0.1001, [y]补=0.1011, [-y]补=1.0101

结果与手算相同,但余数不是真正的余数,多乘了2n,故正确的余数应为2-n×rn,即:0.00000001

(1) 在计算机中,小数点是固定的,不能简单地采用手算的办法。为便于机器操作, 除数Y固定不变, 被除数和余数进行左移 (相当于乘2)。

(2) 机器不会心算,必须先作减法,若余数为正, 才知道够减;若余数为负, 才知道不够减。不够减时必须恢复原来的余数, 以便再继续往下运算。这种方法称为恢复余数法。

(3) 要恢复原来的余数, 只要当前的余数加上除数即可。但由于要恢复余数, 使除法进行过程的步数不固定, 因此控制比较复杂。

实际中常用不恢复余数法,又称加减交替法。其特点是运算过程中如出现不够减,则不必恢复余数,根据余数符号, 可以继续往下运算,因此步数固定,控制简单。

3.恢复余数法

被除数减除数,够减时,商1;不够减时商0。

由于商0时若不够减,即不能作减法,但现在在判断是否商0时,已经减了除数,为了下次能正确运算,必须把已减掉的除数加回去恢复余数。这就是“恢复余数法”。

【例1】x=0.1001, y=0.1011, 用恢复余数法求 x/y。

解:[x]原 =[x]补= x=0.1001, [y]补=0.1011, [-y]补=1.0101

余数每次左移相当于乘以2,在求得n位商后,相当于多乘了2^n,所以最后余数应乘以2^(-n)才是正确的值。

故:[q]原=0. 1 1 0 1 余数 [r4]原=0.00000001

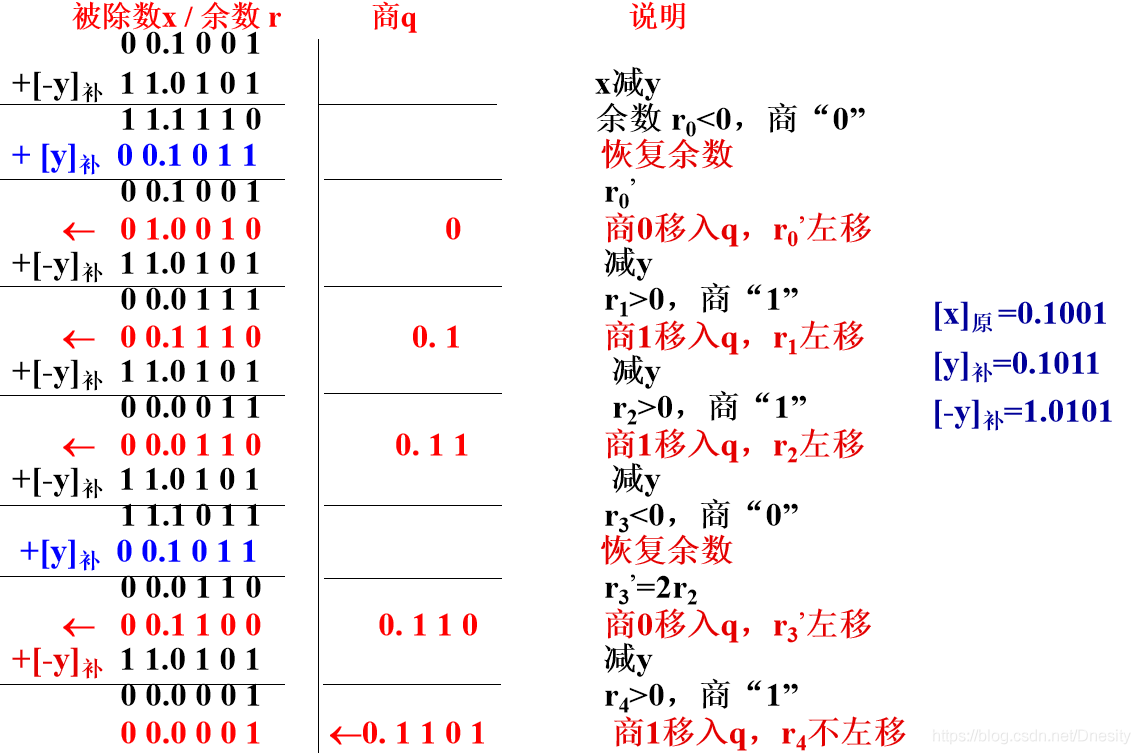

4.加减交替法(不恢复余数法)

上述恢复余数法由于要恢复余数,使得除法的步数不固定,控制比较复杂。实际上常用的是加减交替法。

特点:当运算过程中出现不够减的情况,不必恢复余数,而是 根据余数的符号,继续往下运算,因此步数固定,控制简单。

运算规则:

当余数为正时,商1,余数左移一位,减除数;

当余数为负时,商0,余数左移一位,加除数。

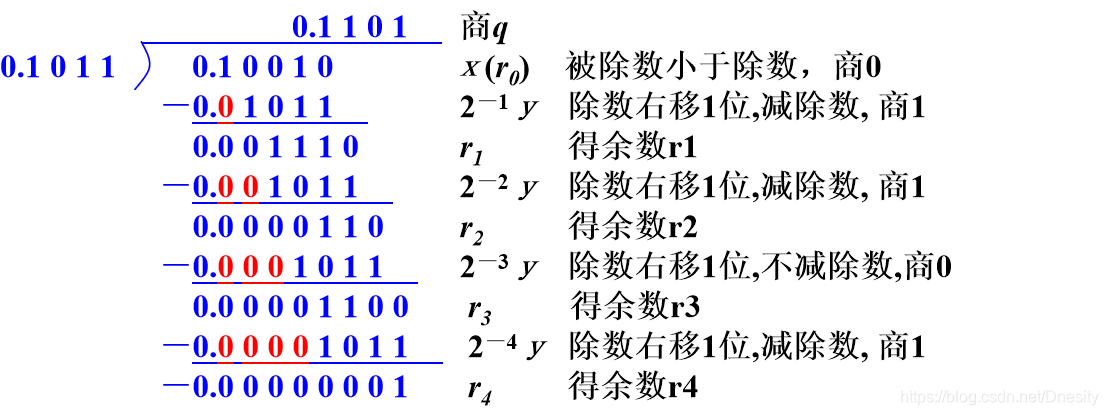

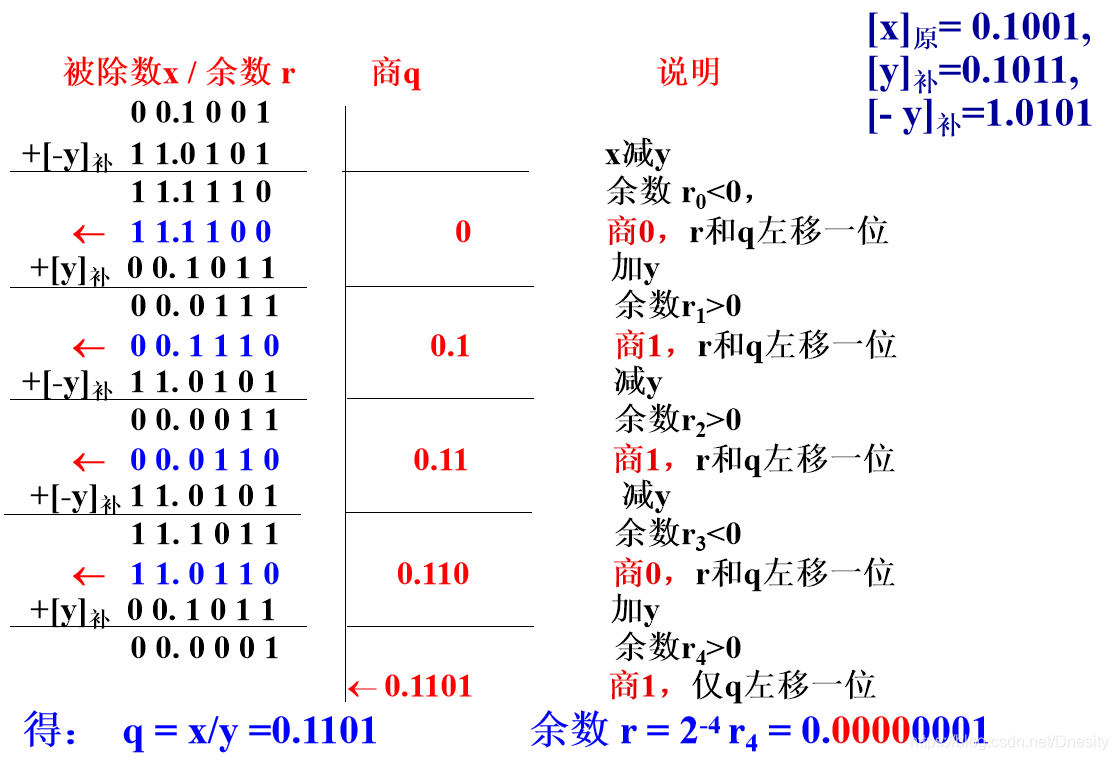

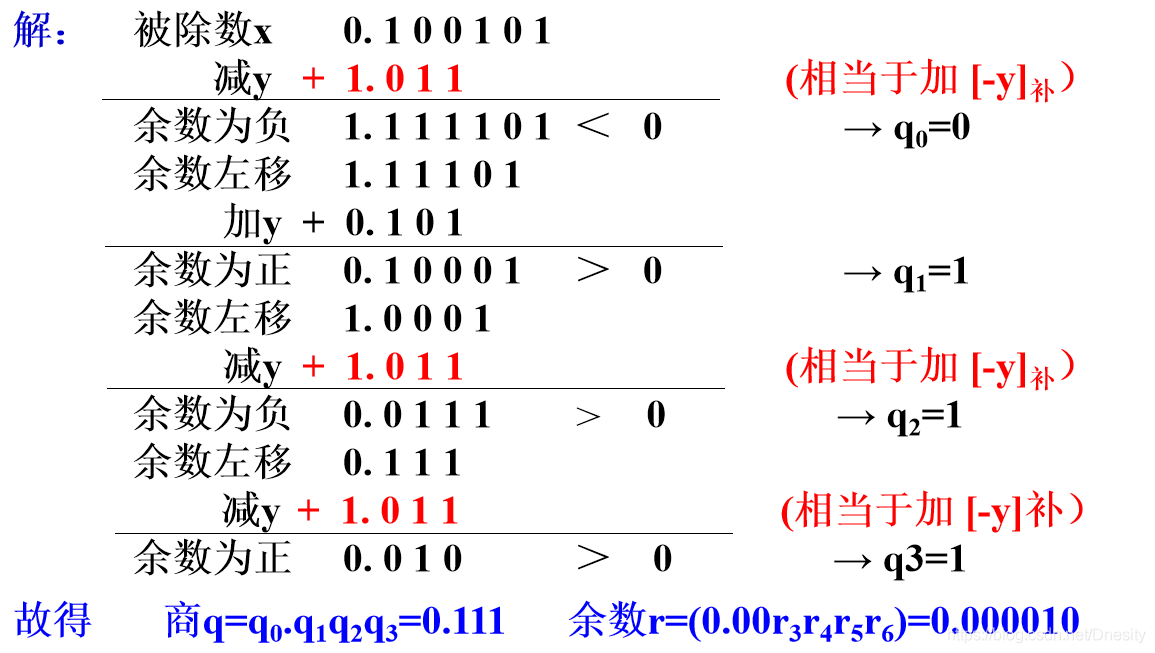

【例2】x=0.1001, y=0.1011, 用加减交替法求 x/y. 解:[x]原=[x]补= x =0.1001, [y]补=0.1011, [- y]补=1.0101

余数每次左移相当于乘以2,在求得n位商后,相当于多乘了2^n,所以最后余数应乘以2^(-n)才是正确的值。

故:[q]原=0. 1 1 0 1 余数 [r4]原=0.00000001

4.加减交替法(不恢复余数法)

上述恢复余数法由于要恢复余数,使得除法的步数不固定,控制比较复杂。实际上常用的是加减交替法。

特点:当运算过程中出现不够减的情况,不必恢复余数,而是 根据余数的符号,继续往下运算,因此步数固定,控制简单。

运算规则:

当余数为正时,商1,余数左移一位,减除数;

当余数为负时,商0,余数左移一位,加除数。

【例2】x=0.1001, y=0.1011, 用加减交替法求 x/y. 解:[x]原=[x]补= x =0.1001, [y]补=0.1011, [- y]补=1.0101

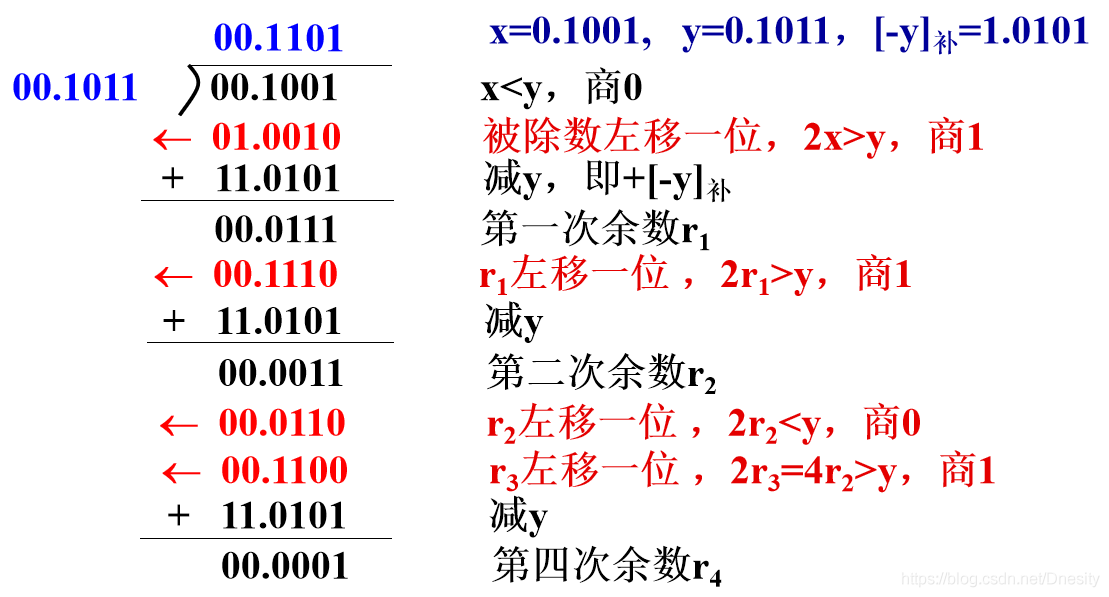

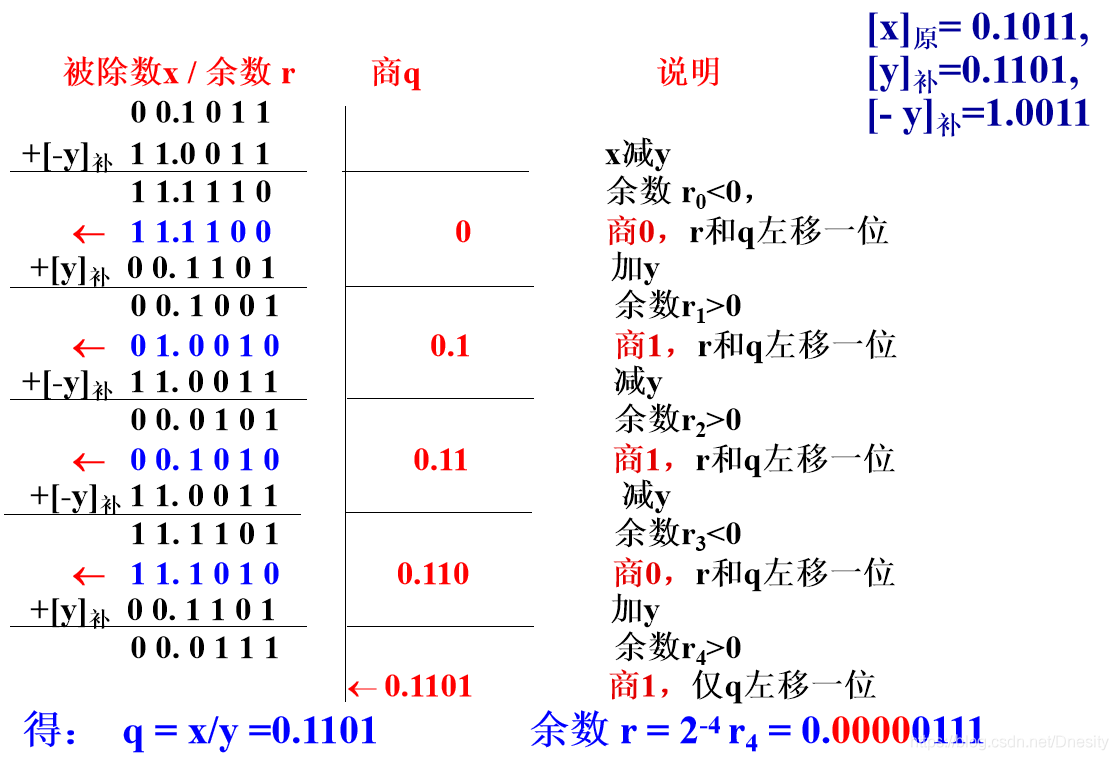

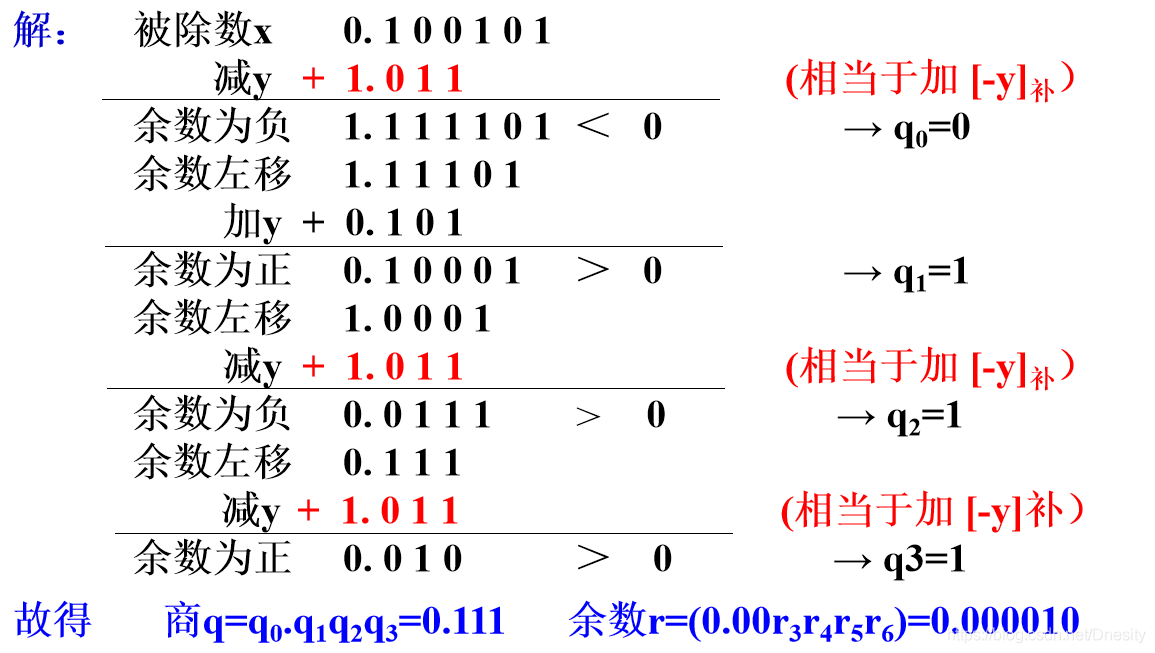

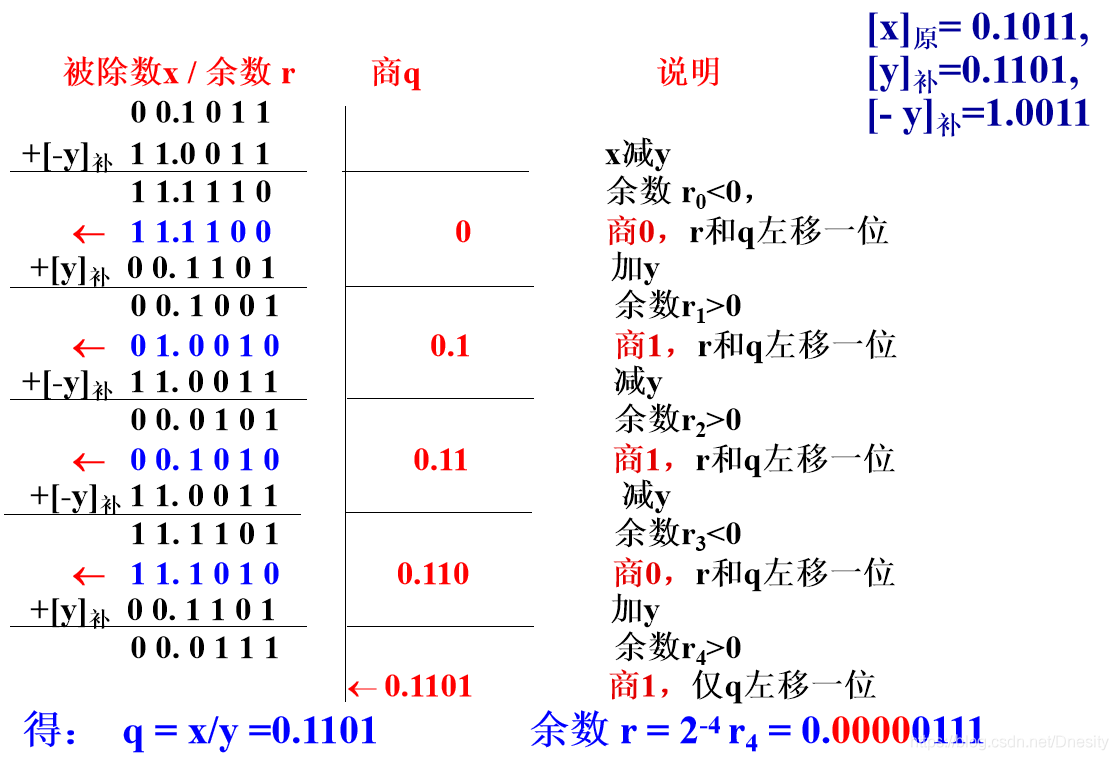

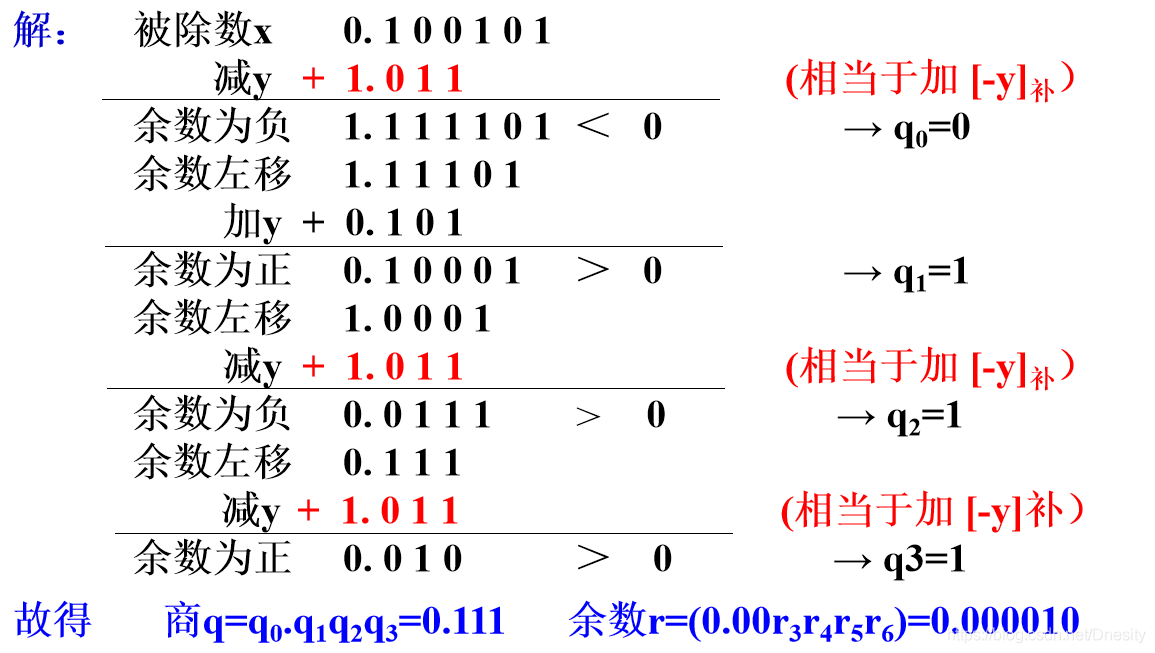

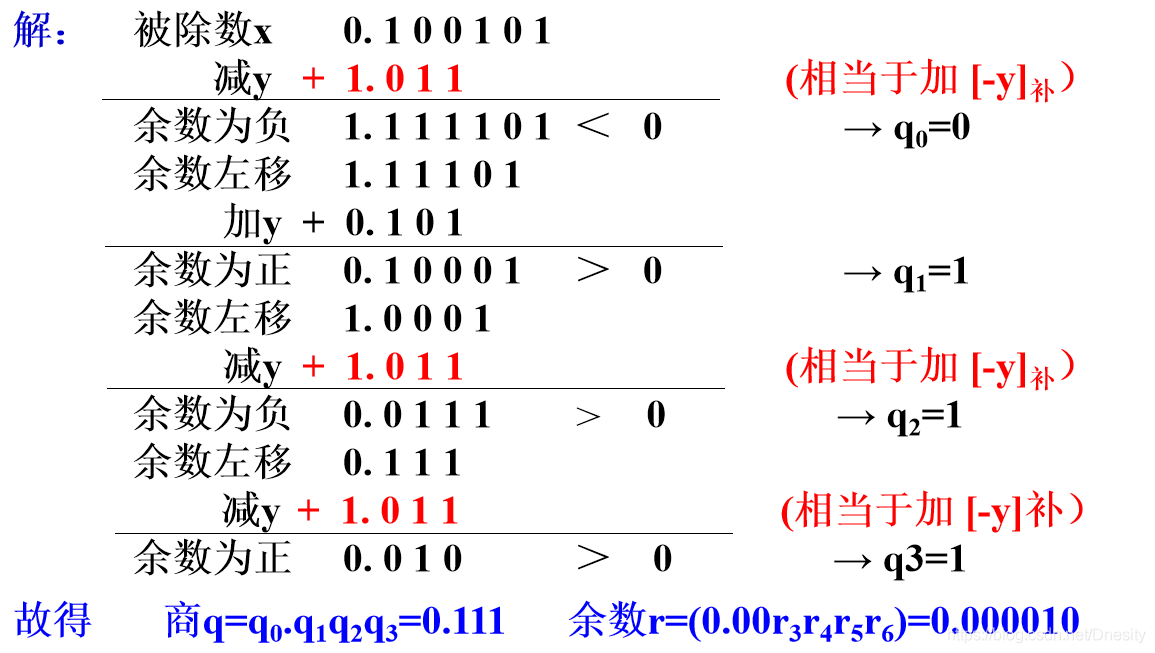

【例3】x=0.1011, y=0.1101, 用加减交替法求 x/y. 解:[x]原=[x]补= x =0.1011, [y]补=0.1101, [- y]补=1.0011

【例3】x=0.1011, y=0.1101, 用加减交替法求 x/y. 解:[x]原=[x]补= x =0.1011, [y]补=0.1101, [- y]补=1.0011

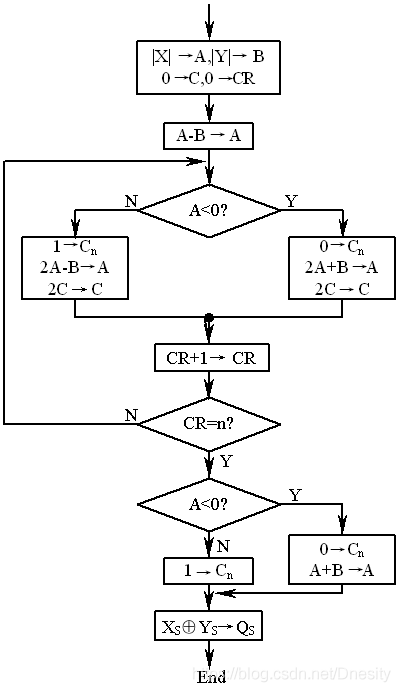

原码加减交替除法流程图

原码加减交替除法流程图

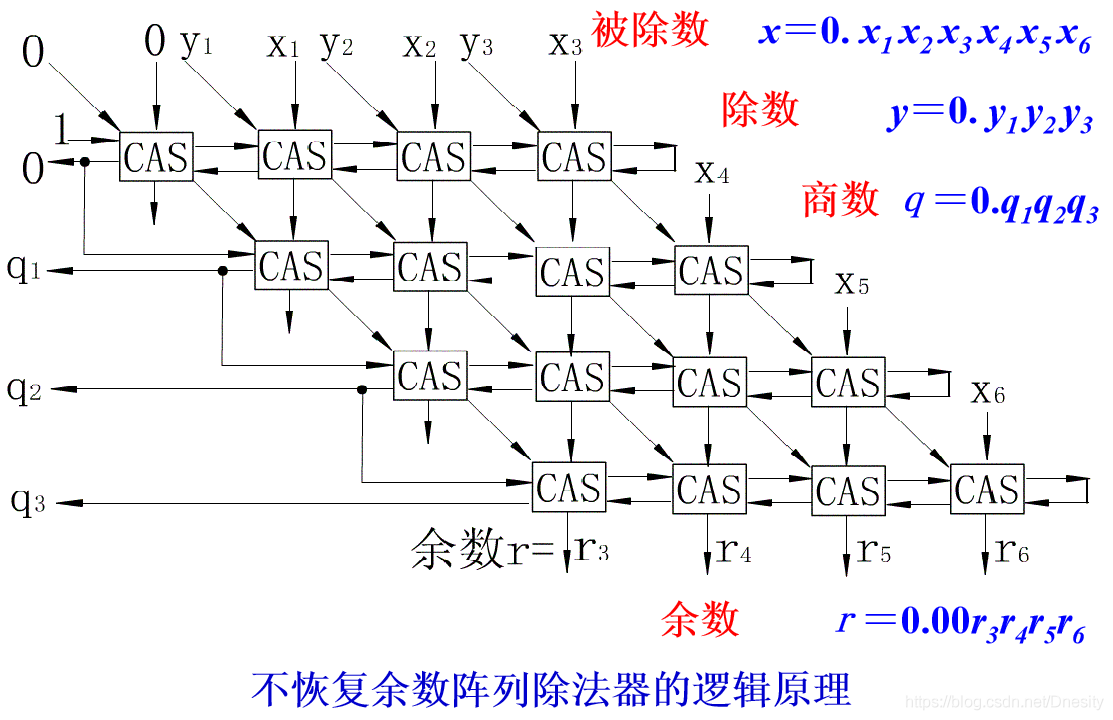

阵列除法器

阵列式除法器是一种并行运算部件, 采用大规模集成电路制造。与早期的串行除法器相比, 阵列除法器不仅所需的控制线路少, 而且能提供令人满意的高速运算速度。

阵列除法器有多种多样形式:

不恢复余数阵列除法器;

补码阵列除法器等等。

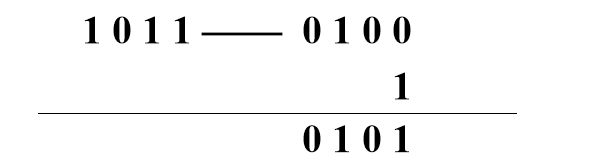

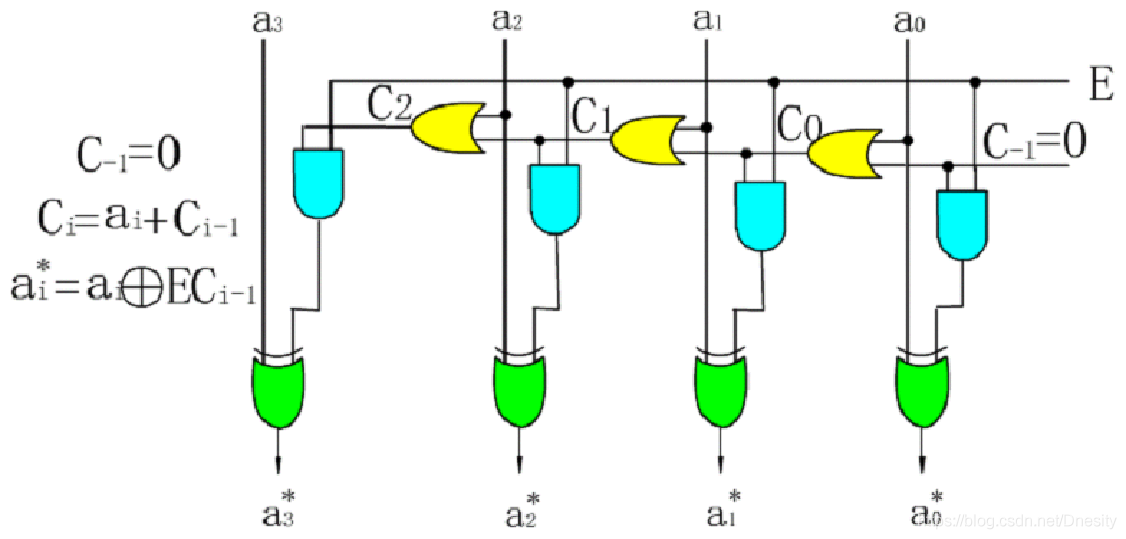

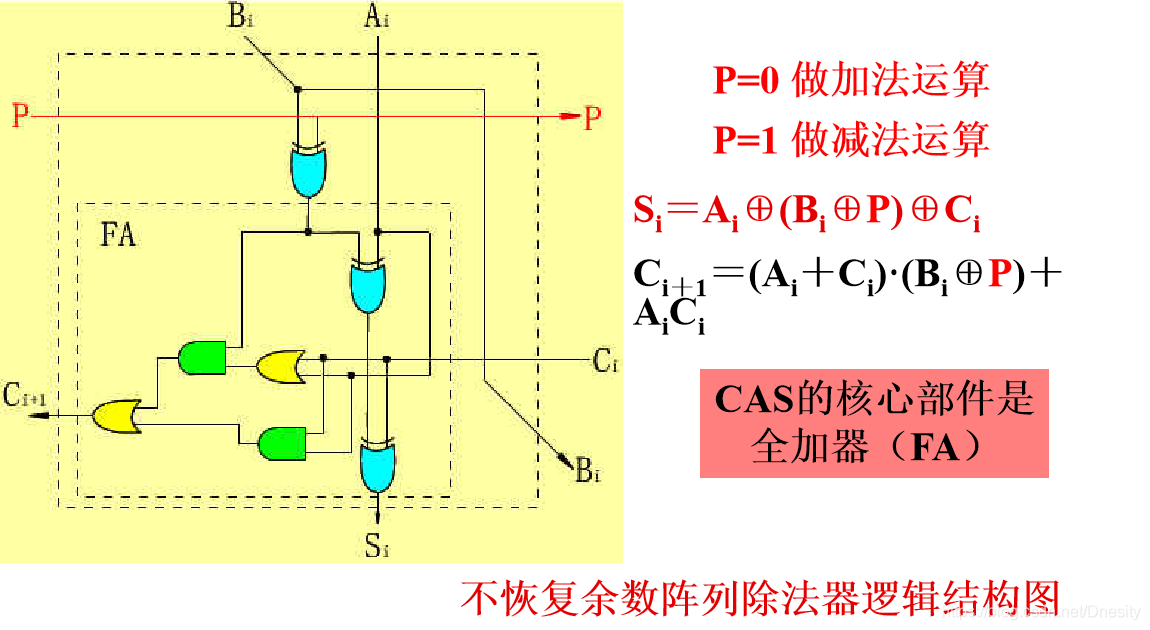

1.可控加法/减法(CAS)单元

用于并行除法流水逻辑阵列中。

阵列除法器

阵列式除法器是一种并行运算部件, 采用大规模集成电路制造。与早期的串行除法器相比, 阵列除法器不仅所需的控制线路少, 而且能提供令人满意的高速运算速度。

阵列除法器有多种多样形式:

不恢复余数阵列除法器;

补码阵列除法器等等。

1.可控加法/减法(CAS)单元

用于并行除法流水逻辑阵列中。

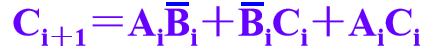

在减法情况下:输入Ci称为借位输入,而Ci+1称为借位输出。

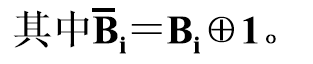

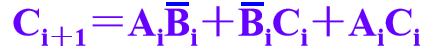

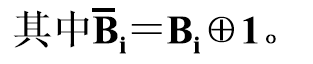

为说明CAS单元的实际内部电路实现,将方程式

Si=Ai⊕(Bi⊕P)⊕Ci

Ci+1=(Ai+Ci)·(Bi⊕P)+AiCi

加以变换,可得如下形式:

在减法情况下:输入Ci称为借位输入,而Ci+1称为借位输出。

为说明CAS单元的实际内部电路实现,将方程式

Si=Ai⊕(Bi⊕P)⊕Ci

Ci+1=(Ai+Ci)·(Bi⊕P)+AiCi

加以变换,可得如下形式:

在这两个表达式中,每一个都能用一个三级组合逻辑电路(包括反向器)来实现。因此每一个基本的CAS单元的延迟时间为3T单元。

2.不恢复余数的阵列除法器(不恢复余数阵列除法,也叫加减交替法。)

在不恢复余数的除法阵列中: • 当余数为正时(ri ≥ 0) ,商“1”,下次做减法运算,减法是用2的补码运算来实现的,此时

[x-y]补= [x ]补+ [-y]补;

• 当余数为负时(ri< 0) ,商“0”,下次做加法运算;

• 每次运算完成后要将余数左移一位,再与除数做加或减运算; • 商的符号由两数的符号按位相加求得。

例: x=0.101001, y=0.111, 求x÷y。 [-y]补=1.001

在这两个表达式中,每一个都能用一个三级组合逻辑电路(包括反向器)来实现。因此每一个基本的CAS单元的延迟时间为3T单元。

2.不恢复余数的阵列除法器(不恢复余数阵列除法,也叫加减交替法。)

在不恢复余数的除法阵列中: • 当余数为正时(ri ≥ 0) ,商“1”,下次做减法运算,减法是用2的补码运算来实现的,此时

[x-y]补= [x ]补+ [-y]补;

• 当余数为负时(ri< 0) ,商“0”,下次做加法运算;

• 每次运算完成后要将余数左移一位,再与除数做加或减运算; • 商的符号由两数的符号按位相加求得。

例: x=0.101001, y=0.111, 求x÷y。 [-y]补=1.001

例: x=0.100101, y=0.101, 求x÷y。 [-y]补=1.011

例: x=0.100101, y=0.101, 求x÷y。 [-y]补=1.011

Cactus仙人掌

发布了29 篇原创文章 · 获赞 1 · 访问量 3833

私信

关注

Cactus仙人掌

发布了29 篇原创文章 · 获赞 1 · 访问量 3833

私信

关注

不考虑进位

不考虑进位

各种逻辑门的图形符号

各种逻辑门的图形符号

1.一位全加器

1.一位全加器

机器与人们习惯的算法不同之处:

(1) 机器通常只有n位长, 两个n位数相乘, 乘积可能为2n位。

(2) 只有两个操作数相加的加法器难以胜任将n位积 一次相加起来的运算。

2.适合定点机的形式

机器与人们习惯的算法不同之处:

(1) 机器通常只有n位长, 两个n位数相乘, 乘积可能为2n位。

(2) 只有两个操作数相加的加法器难以胜任将n位积 一次相加起来的运算。

2.适合定点机的形式

为了适合两个操作数相加的加法器,将 x·y 改写成下面形式:

为了适合两个操作数相加的加法器,将 x·y 改写成下面形式:

根据此式,按式中括号可表达的层次,从内向外逐次进行移位累加。

一般而言,设被乘数x,乘数y都是小于1的n位定点正数:

x=0.x1x2......xn <1

y=0.y1y2......yn <1

根据此式,按式中括号可表达的层次,从内向外逐次进行移位累加。

一般而言,设被乘数x,乘数y都是小于1的n位定点正数:

x=0.x1x2......xn <1

y=0.y1y2......yn <1

形成递推公式

形成递推公式

3.原码一位乘法流程图

3.原码一位乘法流程图

(1) 习惯方法运算过程:

(1) 习惯方法运算过程:

(2) 不带符号阵列乘法器逻辑框图

(2) 不带符号阵列乘法器逻辑框图

例2: 对1011求补。

例2: 对1011求补。

方法:从数的最右端a0开始,由右向左, 直到找出第一个“1”,例如ai=1, 0≤i≤n。这样, ai以左的每一个输入位都求反, 即1变0, 0变1。

方法:从数的最右端a0开始,由右向左, 直到找出第一个“1”,例如ai=1, 0≤i≤n。这样, ai以左的每一个输入位都求反, 即1变0, 0变1。

2.机器运算与手算的不同

原码一位除法

2.机器运算与手算的不同

原码一位除法

结果与手算相同,但余数不是真正的余数,多乘了2n,故正确的余数应为2-n×rn,即:0.00000001

(1) 在计算机中,小数点是固定的,不能简单地采用手算的办法。为便于机器操作, 除数Y固定不变, 被除数和余数进行左移 (相当于乘2)。

(2) 机器不会心算,必须先作减法,若余数为正, 才知道够减;若余数为负, 才知道不够减。不够减时必须恢复原来的余数, 以便再继续往下运算。这种方法称为恢复余数法。

(3) 要恢复原来的余数, 只要当前的余数加上除数即可。但由于要恢复余数, 使除法进行过程的步数不固定, 因此控制比较复杂。

实际中常用不恢复余数法,又称加减交替法。其特点是运算过程中如出现不够减,则不必恢复余数,根据余数符号, 可以继续往下运算,因此步数固定,控制简单。

3.恢复余数法

被除数减除数,够减时,商1;不够减时商0。

由于商0时若不够减,即不能作减法,但现在在判断是否商0时,已经减了除数,为了下次能正确运算,必须把已减掉的除数加回去恢复余数。这就是“恢复余数法”。

【例1】x=0.1001, y=0.1011, 用恢复余数法求 x/y。

解:[x]原 =[x]补= x=0.1001, [y]补=0.1011, [-y]补=1.0101

结果与手算相同,但余数不是真正的余数,多乘了2n,故正确的余数应为2-n×rn,即:0.00000001

(1) 在计算机中,小数点是固定的,不能简单地采用手算的办法。为便于机器操作, 除数Y固定不变, 被除数和余数进行左移 (相当于乘2)。

(2) 机器不会心算,必须先作减法,若余数为正, 才知道够减;若余数为负, 才知道不够减。不够减时必须恢复原来的余数, 以便再继续往下运算。这种方法称为恢复余数法。

(3) 要恢复原来的余数, 只要当前的余数加上除数即可。但由于要恢复余数, 使除法进行过程的步数不固定, 因此控制比较复杂。

实际中常用不恢复余数法,又称加减交替法。其特点是运算过程中如出现不够减,则不必恢复余数,根据余数符号, 可以继续往下运算,因此步数固定,控制简单。

3.恢复余数法

被除数减除数,够减时,商1;不够减时商0。

由于商0时若不够减,即不能作减法,但现在在判断是否商0时,已经减了除数,为了下次能正确运算,必须把已减掉的除数加回去恢复余数。这就是“恢复余数法”。

【例1】x=0.1001, y=0.1011, 用恢复余数法求 x/y。

解:[x]原 =[x]补= x=0.1001, [y]补=0.1011, [-y]补=1.0101

余数每次左移相当于乘以2,在求得n位商后,相当于多乘了2^n,所以最后余数应乘以2^(-n)才是正确的值。

故:[q]原=0. 1 1 0 1 余数 [r4]原=0.00000001

4.加减交替法(不恢复余数法)

上述恢复余数法由于要恢复余数,使得除法的步数不固定,控制比较复杂。实际上常用的是加减交替法。

特点:当运算过程中出现不够减的情况,不必恢复余数,而是 根据余数的符号,继续往下运算,因此步数固定,控制简单。

运算规则:

当余数为正时,商1,余数左移一位,减除数;

当余数为负时,商0,余数左移一位,加除数。

【例2】x=0.1001, y=0.1011, 用加减交替法求 x/y. 解:[x]原=[x]补= x =0.1001, [y]补=0.1011, [- y]补=1.0101

余数每次左移相当于乘以2,在求得n位商后,相当于多乘了2^n,所以最后余数应乘以2^(-n)才是正确的值。

故:[q]原=0. 1 1 0 1 余数 [r4]原=0.00000001

4.加减交替法(不恢复余数法)

上述恢复余数法由于要恢复余数,使得除法的步数不固定,控制比较复杂。实际上常用的是加减交替法。

特点:当运算过程中出现不够减的情况,不必恢复余数,而是 根据余数的符号,继续往下运算,因此步数固定,控制简单。

运算规则:

当余数为正时,商1,余数左移一位,减除数;

当余数为负时,商0,余数左移一位,加除数。

【例2】x=0.1001, y=0.1011, 用加减交替法求 x/y. 解:[x]原=[x]补= x =0.1001, [y]补=0.1011, [- y]补=1.0101

【例3】x=0.1011, y=0.1101, 用加减交替法求 x/y. 解:[x]原=[x]补= x =0.1011, [y]补=0.1101, [- y]补=1.0011

【例3】x=0.1011, y=0.1101, 用加减交替法求 x/y. 解:[x]原=[x]补= x =0.1011, [y]补=0.1101, [- y]补=1.0011

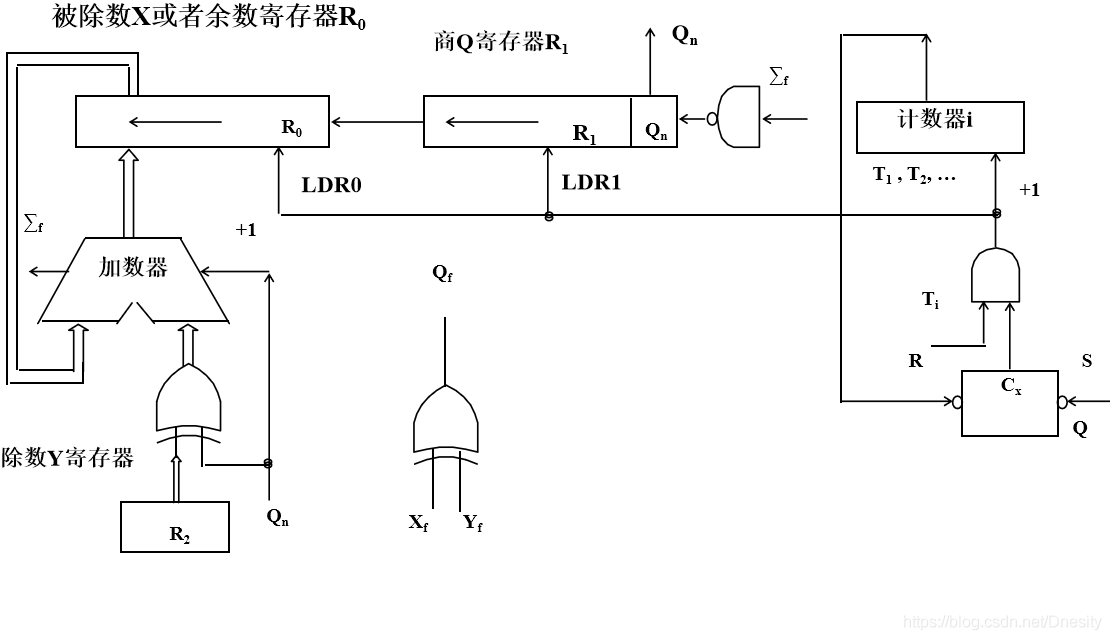

原码加减交替除法流程图

原码加减交替除法流程图

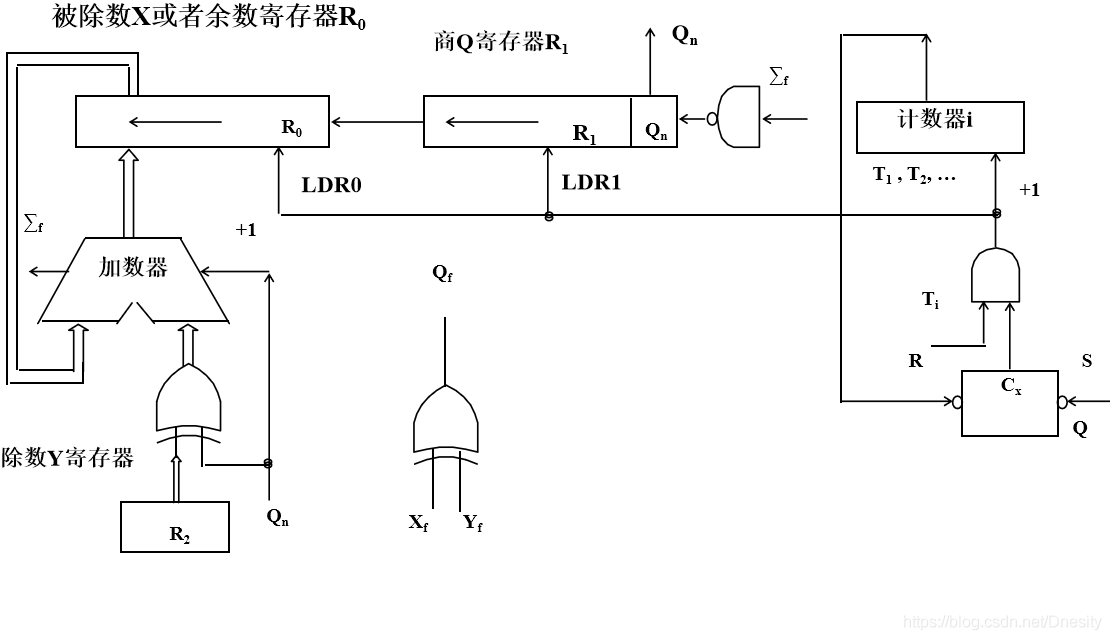

原码加减交替法原理逻辑框图

阵列除法器

阵列式除法器是一种并行运算部件, 采用大规模集成电路制造。与早期的串行除法器相比, 阵列除法器不仅所需的控制线路少, 而且能提供令人满意的高速运算速度。

阵列除法器有多种多样形式:

不恢复余数阵列除法器;

补码阵列除法器等等。

1.可控加法/减法(CAS)单元

用于并行除法流水逻辑阵列中。

阵列除法器

阵列式除法器是一种并行运算部件, 采用大规模集成电路制造。与早期的串行除法器相比, 阵列除法器不仅所需的控制线路少, 而且能提供令人满意的高速运算速度。

阵列除法器有多种多样形式:

不恢复余数阵列除法器;

补码阵列除法器等等。

1.可控加法/减法(CAS)单元

用于并行除法流水逻辑阵列中。

在减法情况下:输入Ci称为借位输入,而Ci+1称为借位输出。

为说明CAS单元的实际内部电路实现,将方程式

Si=Ai⊕(Bi⊕P)⊕Ci

Ci+1=(Ai+Ci)·(Bi⊕P)+AiCi

加以变换,可得如下形式:

在减法情况下:输入Ci称为借位输入,而Ci+1称为借位输出。

为说明CAS单元的实际内部电路实现,将方程式

Si=Ai⊕(Bi⊕P)⊕Ci

Ci+1=(Ai+Ci)·(Bi⊕P)+AiCi

加以变换,可得如下形式:

在这两个表达式中,每一个都能用一个三级组合逻辑电路(包括反向器)来实现。因此每一个基本的CAS单元的延迟时间为3T单元。

2.不恢复余数的阵列除法器(不恢复余数阵列除法,也叫加减交替法。)

在不恢复余数的除法阵列中: • 当余数为正时(ri ≥ 0) ,商“1”,下次做减法运算,减法是用2的补码运算来实现的,此时

[x-y]补= [x ]补+ [-y]补;

• 当余数为负时(ri< 0) ,商“0”,下次做加法运算;

• 每次运算完成后要将余数左移一位,再与除数做加或减运算; • 商的符号由两数的符号按位相加求得。

例: x=0.101001, y=0.111, 求x÷y。 [-y]补=1.001

在这两个表达式中,每一个都能用一个三级组合逻辑电路(包括反向器)来实现。因此每一个基本的CAS单元的延迟时间为3T单元。

2.不恢复余数的阵列除法器(不恢复余数阵列除法,也叫加减交替法。)

在不恢复余数的除法阵列中: • 当余数为正时(ri ≥ 0) ,商“1”,下次做减法运算,减法是用2的补码运算来实现的,此时

[x-y]补= [x ]补+ [-y]补;

• 当余数为负时(ri< 0) ,商“0”,下次做加法运算;

• 每次运算完成后要将余数左移一位,再与除数做加或减运算; • 商的符号由两数的符号按位相加求得。

例: x=0.101001, y=0.111, 求x÷y。 [-y]补=1.001

例: x=0.100101, y=0.101, 求x÷y。 [-y]补=1.011

例: x=0.100101, y=0.101, 求x÷y。 [-y]补=1.011

- 点赞

- 收藏

- 分享

- 文章举报

Cactus仙人掌

发布了29 篇原创文章 · 获赞 1 · 访问量 3833

私信

关注

Cactus仙人掌

发布了29 篇原创文章 · 获赞 1 · 访问量 3833

私信

关注

相关文章推荐

- 运算方法和运算器

- 运算方法和运算器

- 【计算机组成原理】第2章 运算方法和运算器

- 计算机组成复习——运算方法与运算器

- 运算方法与运算器

- Chapter2 运算方法与运算器

- 计算机组成原理:运算方法和运算器

- 第二章 运算方法和运算器

- 第二章 运算方法和运算器笔记简记

- matlab控制运算精度函数digits(A)和vpa(B)的使用方法

- JS浮点数相乘运算解决误差的方法 转载

- java实现跨数据库关联运算的简便方法

- 按位与、或、异或等运算方法

- 计算机的运算方法

- JSP第四篇【EL表达式介绍、获取各类数据、11个内置对象、执行运算、回显数据、自定义函数、fn方法库】

- 第6章 计算机的运算方法

- inux shell 实现 四则运算(整数及浮点) 简单方法

- linux shell 时间运算以及时间差计算方法

- (高精度运算4.7.26)POJ 1220 NUMBER BASE CONVERSION(高精度数的任意进制的转换——方法:ba1----->10进制----->ba2)

- java中&AND |OR !NOT^XOR && ||逻辑运算符的运算方法