关于利用D触发器实现2/4分频的思路与VERILOG代码

2018-03-15 22:52

363 查看

首先要理解的是利用D触发器实现2分频的思路:verilog代码如下:

module div_2 (

input clk_in,input rst ,output clk_out);reg clk;always @( posedge clk or negedge rst )begin

if( !rst )clk<= 1'h0;else

clk<=~clk;

endendmodule

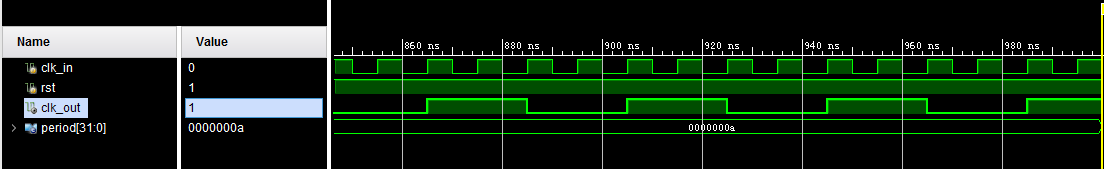

4分频的设计是基于2分频再2分频实现的代码如下:module div_2( input clk_in,input rst,//output clk_out_1output clk_out ); regclk ; wireclk_out_1; regclk_2; // wire clk_m; always @(posedge clk_in or negedge rst ) if(!rst) begin clk<= 1'h0; clk_2 <= 1'b0; end else begin clk<= ~clk; end assign clk_out_1 = clk; always @ (posedge clk_out_1) if(!rst) begin clk_2 <= 1'b0; end else begin clk_2 <= ~clk_2; end assign clk_out = clk_2;endmodule下面附上仿真图:

module div_2 (

input clk_in,input rst ,output clk_out);reg clk;always @( posedge clk or negedge rst )begin

if( !rst )clk<= 1'h0;else

clk<=~clk;

endendmodule

4分频的设计是基于2分频再2分频实现的代码如下:module div_2( input clk_in,input rst,//output clk_out_1output clk_out ); regclk ; wireclk_out_1; regclk_2; // wire clk_m; always @(posedge clk_in or negedge rst ) if(!rst) begin clk<= 1'h0; clk_2 <= 1'b0; end else begin clk<= ~clk; end assign clk_out_1 = clk; always @ (posedge clk_out_1) if(!rst) begin clk_2 <= 1'b0; end else begin clk_2 <= ~clk_2; end assign clk_out = clk_2;endmodule下面附上仿真图:

相关文章推荐

- iOS实战演练之关于数据交互的问题(利用XAMPP搭建本地服务器, 编写PHP代码实现iOS端注册登录功能)

- 关于dtree树代码实现带checkox修改的最新思路

- 利用iframe技巧获取访问者qq实现思路及示例代码

- 3/5分频的实现思路与Verilog代码

- 关于pgrouting 的 最短路径 思路解析 以及C++代码实现

- 关于MapXtreme for Java鹰眼实现思路及代码

- PHP利用MySQL保存session的实现思路及示例代码

- 关于 如何实践kernel/driver/u-boot ,怎么样按照作者的思路实现自己的代码

- 关于MapXtreme for Java鹰眼实现思路及代码

- Asp.net利用JQuery AJAX实现无刷新评论思路与代码

- PHP利用MySQL保存session的实现思路及示例代码

- PHP中利用mysql进行访问统计的思路和实现代码

- Asp.net利用JQuery AJAX实现无刷新评论思路与代码

- 关于实现代码语法标亮 dp.SyntaxHighlighter

- 关于在Windows环境下,利用Visual C++ 6 实现并行计算

- 如何利用JS实现对后台CS代码的调用

- asp.net下利用JS实现对后台CS代码的调用方法

- 利用newxy(新坐标),不写一行java代码实现多项查询

- 关于利用SMTP和POP协议来实现分布式查询【暂放首页】