IMX6Q调试之 —– DDR3 32位移植

2018-03-12 10:03

951 查看

IMX6Q调试之 —– DDR3 32位移植

自己的板子是参考[fleescale][6]官方开发板[imx6qsabresd][6]的开发套件做的设计的,无奈修改的地方太多了本章主要来说ddr3 的移植,首先需要的工具和软件:一 、飞思卡尔IMX6 平台DRAM 接口高阶应用指南 -DDR3 篇

二 、MX6Q_SabreSD_DDR3_register_programming_aid_v2.0.xlsx

三 、ddr_stress_tester_v2.52

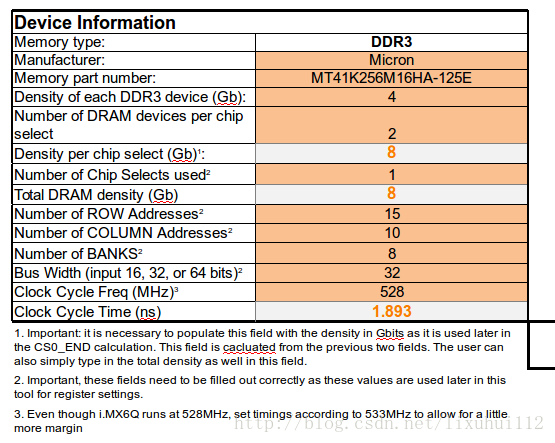

先详细阅读《飞思卡尔IMX6 平台DRAM 接口高阶应用指南 -DDR3 篇》,然后再根据自己具体使用的ddr3芯片,以及对比原理图(原理图主要看多少根地址线和数据线),然后再填写表格《MX6Q_SabreSD_DDR3_register_programming_aid_v0.10.xlsx》,如图:

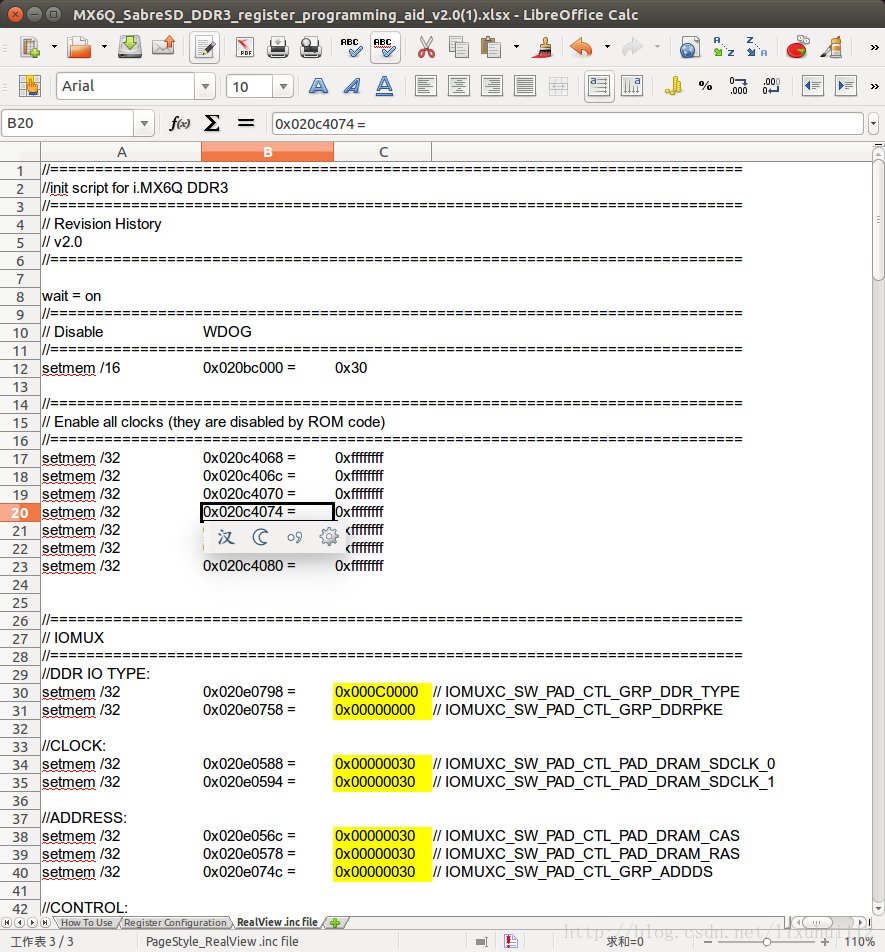

填写好后会生成 [.inc][6]文件:

根据这个文件修改

mx6q-ddr.h

例如我根据生成的 inc文件

MX6Q_SabreSD_DDR3_32bit.inc

//============================================================================= //init script for i.Mx6Q DDR3 //============================================================================= // Revision History // v01 //============================================================================= wait = on //============================================================================= // Disable WDOG //============================================================================= //setmem /16 0x020bc000 = 0x30 //============================================================================= // Enable all clocks (they are disabled by ROM code) //============================================================================= setmem /32 0x020c4068 = 0xffffffff setmem /32 0x020c406c = 0xffffffff setmem /32 0x020c4070 = 0xffffffff setmem /32 0x020c4074 = 0xffffffff setmem /32 0x020c4078 = 0xffffffff setmem /32 0x020c407c = 0xffffffff setmem /32 0x020c4080 = 0xffffffff setmem /32 0x020c4084 = 0xffffffff //============================================================================= // IOMUX //============================================================================= //DDR IO TYPE: setmem /32 0x020e0798 = 0x000C0000 // IOMUXC_SW_PAD_CTL_GRP_DDR_TYPE setmem /32 0x020e0758 = 0x00000000 // IOMUXC_SW_PAD_CTL_GRP_DDRPKE //CLOCK: setmem /32 0x020e0588 = 0x00000030 // IOMUXC_SW_PAD_CTL_PAD_DRAM_SDCLK_0 setmem /32 0x020e0594 = 0x00000030 // IOMUXC_SW_PAD_CTL_PAD_DRAM_SDCLK_1 //ADDRESS: setmem /32 0x020e056c = 0x00000030 // IOMUXC_SW_PAD_CTL_PAD_DRAM_CAS setmem /32 0x020e0578 = 0x00000030 // IOMUXC_SW_PAD_CTL_PAD_DRAM_RAS setmem /32 0x020e074c = 0x00000030 // IOMUXC_SW_PAD_CTL_GRP_ADDDS //Control: setmem /32 0x020e057c = 0x00000030 // IOMUXC_SW_PAD_CTL_PAD_DRAM_RESET setmem /32 0x020e058c = 0x00000000 // IOMUXC_SW_PAD_CTL_PAD_DRAM_SDBA2 - DSE can be configured using Group Control Register: IOMUXC_SW_PAD_CTL_GRP_CTLDS setmem /32 0x020e059c = 0x00000030 // IOMUXC_SW_PAD_CTL_PAD_DRAM_SDODT0 setmem /32 0x020e05a0 = 0x00000030 // IOMUXC_SW_PAD_CTL_PAD_DRAM_SDODT1 setmem /32 0x020e078c = 0x00000030 // IOMUXC_SW_PAD_CTL_GRP_CTLDS //Data Strobes: setmem /32 0x020e0750 = 0x00020000 // IOMUXC_SW_PAD_CTL_GRP_DDRMODE_CTL setmem /32 0x020e05a8 = 0x00000030 // IOMUXC_SW_PAD_CTL_PAD_DRAM_SDQS0 setmem /32 0x020e05b0 = 0x00000030 // IOMUXC_SW_PAD_CTL_PAD_DRAM_SDQS1 setmem /32 0x020e0524 = 0x00000030 // IOMUXC_SW_PAD_CTL_PAD_DRAM_SDQS2 setmem /32 0x020e051c = 0x00000030 // IOMUXC_SW_PAD_CTL_PAD_DRAM_SDQS3 //setmem /32 0x020e0518 = 0x00000030 // IOMUXC_SW_PAD_CTL_PAD_DRAM_SDQS4 //setmem /32 0x020e050c = 0x00000030 // IOMUXC_SW_PAD_CTL_PAD_DRAM_SDQS5 //setmem /32 0x020e05b8 = 0x00000030 // IOMUXC_SW_PAD_CTL_PAD_DRAM_SDQS6 //setmem /32 0x020e05c0 = 0x00000030 // IOMUXC_SW_PAD_CTL_PAD_DRAM_SDQS7 //Data: setmem /32 0x020e0774 = 0x00020000 // IOMUXC_SW_PAD_CTL_GRP_DDRMODE setmem /32 0x020e0784 = 0x00000030 // IOMUXC_SW_PAD_CTL_GRP_B0DS setmem /32 0x020e0788 = 0x00000030 // IOMUXC_SW_PAD_CTL_GRP_B1DS setmem /32 0x020e0794 = 0x00000030 // IOMUXC_SW_PAD_CTL_GRP_B2DS setmem /32 0x020e079c = 0x00000030 // IOMUXC_SW_PAD_CTL_GRP_B3DS //setmem /32 0x020e07a0 = 0x00000030 // IOMUXC_SW_PAD_CTL_GRP_B4DS //setmem /32 0x020e07a4 = 0x00000030 // IOMUXC_SW_PAD_CTL_GRP_B5DS //setmem /32 0x020e07a8 = 0x00000030 // IOMUXC_SW_PAD_CTL_GRP_B6DS //setmem /32 0x020e0748 = 0x00000030 // IOMUXC_SW_PAD_CTL_GRP_B7DS setmem /32 0x020e05ac = 0x00000030 // IOMUXC_SW_PAD_CTL_PAD_DRAM_DQM0 setmem /32 0x020e05b4 = 0x00000030 // IOMUXC_SW_PAD_CTL_PAD_DRAM_DQM1 setmem /32 0x020e0528 = 0x00000030 // IOMUXC_SW_PAD_CTL_PAD_DRAM_DQM2 setmem /32 0x020e0520 = 0x00000030 // IOMUXC_SW_PAD_CTL_PAD_DRAM_DQM3 //setmem /32 0x020e0514 = 0x00000030 // IOMUXC_SW_PAD_CTL_PAD_DRAM_DQM4 //setmem /32 0x020e0510 = 0x00000030 // IOMUXC_SW_PAD_CTL_PAD_DRAM_DQM5 //setmem /32 0x020e05bc = 0x00000030 // IOMUXC_SW_PAD_CTL_PAD_DRAM_DQM6 //setmem /32 0x020e05c4 = 0x00000030 // IOMUXC_SW_PAD_CTL_PAD_DRAM_DQM7 //============================================================================= // DDR Controller Registers //============================================================================= // Manufacturer: Micron // Device Part Number: MT41K128M16JT-125 // Clock Freq.: 528MHz // Density per CS in Gb: 4 // Chip Selects used: 1 // Number of Banks: 8 // Row address: 14 // Column address: 10 // Data bus width 32 //============================================================================= setmem /32 0x021b001c = 0x00008000 MMDC0_MDSCR, set the Configuration request bit during MMDC set up //============================================================================= // Calibration setup. //============================================================================= setmem /32 0x021b0800 = 0xA1390003 // DDR_PHY_P0_MPZQHWCTRL, enable both one-time & periodic HW ZQ calibration. // For target board, may need to run write leveling calibration to fine tune these settings. setmem /32 0x021b080c = 0x0029002D setmem /32 0x021b0810 = 0x00340028 //setmem /32 0x021b480c = 0x00000000 //setmem /32 0x021b4810 = 0x00000000 ////Read DQS Gating calibration setmem /32 0x021b083c = 0x0238023E // MPDGCTRL0 PHY0 setmem /32 0x021b0840 = 0x0238023C // MPDGCTRL1 PHY0 //setmem /32 0x021b483c = 0x00000000 // MPDGCTRL0 PHY1 //setmem /32 0x021b4840 = 0x00000000 // MPDGCTRL1 PHY1 //Read calibration setmem /32 0x021b0848 = 0x342C3634 // MPRDDLCTL PHY0 //setmem /32 0x021b4848 = 0x40404040 // MPRDDLCTL PHY1 //Write calibration setmem /32 0x021b0850 = 0x2A282A26 // MPWRDLCTL PHY0 //setmem /32 0x021b4850 = 0x40404040 // MPWRDLCTL PHY1 //read data bit delay: (3 is the reccommended default value, although out of reset value is 0) setmem /32 0x021b081c = 0x33333333 // DDR_PHY_P0_MPREDQBY0DL3 setmem /32 0x021b0820 = 0x33333333 // DDR_PHY_P0_MPREDQBY1DL3 setmem /32 0x021b0824 = 0x33333333 // DDR_PHY_P0_MPREDQBY2DL3 setmem /32 0x021b0828 = 0x33333333 // DDR_PHY_P0_MPREDQBY3DL3 //setmem /32 0x021b481c = 0x33333333 // DDR_PHY_P1_MPREDQBY0DL3 //setmem /32 0x021b4820 = 0x33333333 // DDR_PHY_P1_MPREDQBY1DL3 //setmem /32 0x021b4824 = 0x33333333 // DDR_PHY_P1_MPREDQBY2DL3 //setmem /32 0x021b4828 = 0x33333333 // DDR_PHY_P1_MPREDQBY3DL3 //For i.mx6qd parts of versions A & B (v1.0, v1.1), uncomment the following lines. For version C (v1.2), keep commented //setmem /32 0x021b08c0 = 0x24911492 // fine tune SDCLK duty cyc to low - seen to improve measured duty cycle of i.mx6 //setmem /32 0x021b48c0 = 0x24911492 // Complete calibration by forced measurement: setmem /32 0x021b08b8 = 0x00000800 // DDR_PHY_P0_MPMUR0, frc_msr //setmem /32 0x021b48b8 = 0x00000800 // DDR_PHY_P0_MPMUR0, frc_msr //============================================================================= // Calibration setup end //============================================================================= //MMDC init: setmem /32 0x021b0004 = 0x00020036 // MMDC0_MDPDC setmem /32 0x021b0008 = 0x09444040 // MMDC0_MDOTC setmem /32 0x021b000c = 0x54597955 // MMDC0_MDCFG0 setmem /32 0x021b0010 = 0xFF328F64 // MMDC0_MDCFG1 setmem /32 0x021b0014 = 0x01FF00DB // MMDC0_MDCFG2 //MDMISC: RALAT kept to the high level of 5. //MDMISC: consider reducing RALAT if your 528MHz board design allow that. Lower RALAT benefits: //a. better operation at low frequency, for LPDDR2 freq < 100MHz, change RALAT to 3 //b. Small performence improvment setmem /32 0x021b0018 = 0x00011740 // MMDC0_MDMISC setmem /32 0x021b001c = 0x00008000 // MMDC0_MDSCR, set the Configuration request bit during MMDC set up setmem /32 0x021b002c = 0x000026D2 // MMDC0_MDRWD setmem /32 0x021b0030 = 0x00591023 // MMDC0_MDOR setmem /32 0x021b0040 = 0x00000017 // Chan0 CS0_END setmem /32 0x021b0000 = 0x83190000 // MMDC0_MDCTL //Mode register writes setmem /32 0x021b001c = 0x02088032 // MMDC0_MDSCR, MR2 write, CS0 setmem /32 0x021b001c = 0x00008033 // MMDC0_MDSCR, MR3 write, CS0 setmem /32 0x021b001c = 0x00048031 // MMDC0_MDSCR, MR1 write, CS0 setmem /32 0x021b001c = 0x19408030 // MMDC0_MDSCR, MR0write, CS0 setmem /32 0x021b001c = 0x04008040 // MMDC0_MDSCR, ZQ calibration command sent to device on CS0 //setmem /32 0x021b001c = 0x0208803A // MMDC0_MDSCR, MR2 write, CS1 //setmem /32 0x021b001c = 0x0000803B // MMDC0_MDSCR, MR3 write, CS1 //setmem /32 0x021b001c = 0x00048039 // MMDC0_MDSCR, MR1 write, CS1 //setmem /32 0x021b001c = 0x19408038 // MMDC0_MDSCR, MR0write, CS1 //setmem /32 0x021b001c = 0x04008048 // MMDC0_MDSCR, ZQ calibration command sent to device on CS1 setmem /32 0x021b0020 = 0x00007800 // MMDC0_MDREF setmem /32 0x021b0818 = 0x00022227 // DDR_PHY_P0_MPODTCTRL //setmem /32 0x021b4818 = 0x00022227 // DDR_PHY_P1_MPODTCTRL setmem /32 0x021b0004 = 0x00025576 // MMDC0_MDPDC now SDCTL power down enabled setmem /32 0x021b0404 = 0x00011006 // MMDC0_MAPSR ADOPT power down enabled, MMDC will enter automatically to self-refresh while the number of idle cycle reached. setmem /32 0x021b001c = 0x00000000 // MMDC0_MDSCR, clear this register (especially the configuration bit as initialization is complete)1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

177

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

200

201

202

203

204

205

206

207

208

209

210

211

212

213

214

215

[/code]

修改uboot中 arch/arm/include/asm/arch-mx6/mx6q-ddr.h

/* * Copyright (C) 2013 Boundary Devices Inc. * * SPDX-License-Identifier: GPL-2.0+ */ #ifndef __ASM_ARCH_MX6Q_DDR_H__ #define __ASM_ARCH_MX6Q_DDR_H__ #ifndef CONFIG_MX6Q #error "wrong CPU" #endif #define MX6_IOM_DRAM_DQM0 0x020e05ac #define MX6_IOM_DRAM_DQM1 0x020e05b4 #define MX6_IOM_DRAM_DQM2 0x020e0528 #define MX6_IOM_DRAM_DQM3 0x020e0520 //#define MX6_IOM_DRAM_DQM4 0x020e0514 //#define MX6_IOM_DRAM_DQM5 0x020e0510 //#define MX6_IOM_DRAM_DQM6 0x020e05bc //#define MX6_IOM_DRAM_DQM7 0x020e05c4 #define MX6_IOM_DRAM_CAS 0x020e056c #define MX6_IOM_DRAM_RAS 0x020e0578 #define MX6_IOM_DRAM_RESET 0x020e057c #define MX6_IOM_DRAM_SDCLK_0 0x020e0588 #define MX6_IOM_DRAM_SDCLK_1 0x020e0594 #define MX6_IOM_DRAM_SDBA2 0x020e058c #define MX6_IOM_DRAM_SDCKE0 0x020e0590 #define MX6_IOM_DRAM_SDCKE1 0x020e0598 #define MX6_IOM_DRAM_SDODT0 0x020e059c #define MX6_IOM_DRAM_SDODT1 0x020e05a0 #define MX6_IOM_DRAM_SDQS0 0x020e05a8 #define MX6_IOM_DRAM_SDQS1 0x020e05b0 #define MX6_IOM_DRAM_SDQS2 0x020e0524 #define MX6_IOM_DRAM_SDQS3 0x020e051c //#define MX6_IOM_DRAM_SDQS4 0x020e0518 //#define MX6_IOM_DRAM_SDQS5 0x020e050c //#define MX6_IOM_DRAM_SDQS6 0x020e05b8 //#define MX6_IOM_DRAM_SDQS7 0x020e05c0 #define MX6_IOM_GRP_B0DS 0x020e0784 #define MX6_IOM_GRP_B1DS 0x020e0788 #define MX6_IOM_GRP_B2DS 0x020e0794 #define MX6_IOM_GRP_B3DS 0x020e079c //#define MX6_IOM_GRP_B4DS 0x020e07a0 //#define MX6_IOM_GRP_B5DS 0x020e07a4 //#define MX6_IOM_GRP_B6DS 0x020e07a8 //#define MX6_IOM_GRP_B7DS 0x020e0748 #define MX6_IOM_GRP_ADDDS 0x020e074c #define MX6_IOM_DDRMODE_CTL 0x020e0750 #define MX6_IOM_GRP_DDRPKE 0x020e0758 #define MX6_IOM_GRP_DDRMODE 0x020e0774 #define MX6_IOM_GRP_CTLDS 0x020e078c #define MX6_IOM_GRP_DDR_TYPE 0x020e0798 #endif /*__ASM_ARCH_MX6Q_DDR_H__ */1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

[/code]

接下来需要用到imx6 的板子来微调了

windows 下打开

ddr_stress_tester_v2.52 应用程序,选择上面生成的[.inc][6]文件,开发板进入串行下载模式,可在设备管理器中看待HID设备,点击下载 然后 微调,

============================================ DDR Stress Test (2.5.2) Build: Mar 31 2016, 23:07:26 Freescale Semiconductor, Inc. ============================================ ============================================ Chip ID CHIP ID = i.MX6 Dual/Quad (0x63) Internal Revision = TO1.5 ============================================ ============================================ Boot Configuration SRC_SBMR1(0x020d8004) = 0x40000040 SRC_SBMR2(0x020d801c) = 0x32000001 ============================================ ARM Clock set to 1GHz ============================================ DDR configuration BOOT_CFG3[5-4]: 0x00, Single DDR channel. DDR type is DDR3 Data width: 32, bank num: 8 Row size: 15, col size: 10 Chip select CSD0 is used Density per chip select: 1024MB ============================================ Current Temperature: 60 ============================================ DDR Freq: 528 MHz ddr_mr1=0x00000000 Start write leveling calibration... running Write level HW calibration Write leveling calibration completed, update the following registers in your initialization script MMDC_MPWLDECTRL0 ch0 (0x021b080c) = 0x00250027 MMDC_MPWLDECTRL1 ch0 (0x021b0810) = 0x00450034 Write DQS delay result: Write DQS0 delay: 39/256 CK Write DQS1 delay: 37/256 CK Write DQS2 delay: 52/256 CK Write DQS3 delay: 69/256 CK Starting DQS gating calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . BYTE 0: Start: HC=0x02 ABS=0x48 End: HC=0x04 ABS=0x20 Mean: HC=0x03 ABS=0x34 End-0.5*tCK: HC=0x03 ABS=0x20 Final: HC=0x03 ABS=0x34 BYTE 1: Start: HC=0x02 ABS=0x44 End: HC=0x04 ABS=0x18 Mean: HC=0x03 ABS=0x2E End-0.5*tCK: HC=0x03 ABS=0x18 Final: HC=0x03 ABS=0x2E BYTE 2: Start: HC=0x02 ABS=0x50 End: HC=0x04 ABS=0x1C Mean: HC=0x03 ABS=0x36 End-0.5*tCK: HC=0x03 ABS=0x1C Final: HC=0x03 ABS=0x36 BYTE 3: Start: HC=0x02 ABS=0x44 End: HC=0x04 ABS=0x20 Mean: HC=0x03 ABS=0x32 End-0.5*tCK: HC=0x03 ABS=0x20 Final: HC=0x03 ABS=0x32 DQS calibration MMDC0 MPDGCTRL0 = 0x032E0334, MPDGCTRL1 = 0x03320336 Note: Array result[] holds the DRAM test result of each byte. 0: test pass. 1: test fail 4 bits respresent the result of 1 byte. result 0001:byte 0 fail. result 0011:byte 0, 1 fail. Starting Read calibration... ABS_OFFSET=0x00000000 result[00]=0x1111 ABS_OFFSET=0x04040404 result[01]=0x1111 ABS_OFFSET=0x08080808 result[02]=0x1111 ABS_OFFSET=0x0C0C0C0C result[03]=0x1111 ABS_OFFSET=0x10101010 result[04]=0x1111 ABS_OFFSET=0x14141414 result[05]=0x1011 ABS_OFFSET=0x18181818 result[06]=0x1000 ABS_OFFSET=0x1C1C1C1C result[07]=0x1000 ABS_OFFSET=0x20202020 result[08]=0x1000 ABS_OFFSET=0x24242424 result[09]=0x0000 ABS_OFFSET=0x28282828 result[0A]=0x0000 ABS_OFFSET=0x2C2C2C2C result[0B]=0x0000 ABS_OFFSET=0x30303030 result[0C]=0x0000 ABS_OFFSET=0x34343434 result[0D]=0x0000 ABS_OFFSET=0x38383838 result[0E]=0x0000 ABS_OFFSET=0x3C3C3C3C result[0F]=0x0000 ABS_OFFSET=0x40404040 result[10]=0x0000 ABS_OFFSET=0x44444444 result[11]=0x0101 ABS_OFFSET=0x48484848 result[12]=0x0101 ABS_OFFSET=0x4C4C4C4C result[13]=0x0111 ABS_OFFSET=0x50505050 result[14]=0x0111 ABS_OFFSET=0x54545454 result[15]=0x1111 ABS_OFFSET=0x58585858 result[16]=0x1111 ABS_OFFSET=0x5C5C5C5C result[17]=0x1111 ABS_OFFSET=0x60606060 result[18]=0x1111 ABS_OFFSET=0x64646464 result[19]=0x1111 ABS_OFFSET=0x68686868 result[1A]=0x1111 ABS_OFFSET=0x6C6C6C6C result[1B]=0x1111 ABS_OFFSET=0x70707070 result[1C]=0x1111 ABS_OFFSET=0x74747474 result[1D]=0x1111 ABS_OFFSET=0x78787878 result[1E]=0x1111 ABS_OFFSET=0x7C7C7C7C result[1F]=0x1111 Byte 0: (0x18 - 0x40), middle value:0x2c Byte 1: (0x18 - 0x48), middle value:0x30 Byte 2: (0x14 - 0x40), middle value:0x2a Byte 3: (0x24 - 0x50), middle value:0x3a MMDC0 MPRDDLCTL = 0x3A2A302C Starting Write calibration... ABS_OFFSET=0x00000000 result[00]=0x1111 ABS_OFFSET=0x04040404 result[01]=0x1111 ABS_OFFSET=0x08080808 result[02]=0x1111 ABS_OFFSET=0x0C0C0C0C result[03]=0x0011 ABS_OFFSET=0x10101010 result[04]=0x0010 ABS_OFFSET=0x14141414 result[05]=0x0000 ABS_OFFSET=0x18181818 result[06]=0x0000 ABS_OFFSET=0x1C1C1C1C result[07]=0x0000 ABS_OFFSET=0x20202020 result[08]=0x0000 ABS_OFFSET=0x24242424 result[09]=0x0000 ABS_OFFSET=0x28282828 result[0A]=0x0000 ABS_OFFSET=0x2C2C2C2C result[0B]=0x0000 ABS_OFFSET=0x30303030 result[0C]=0x0000 ABS_OFFSET=0x34343434 result[0D]=0x0000 ABS_OFFSET=0x38383838 result[0E]=0x0000 ABS_OFFSET=0x3C3C3C3C result[0F]=0x0000 ABS_OFFSET=0x40404040 result[10]=0x0000 ABS_OFFSET=0x44444444 result[11]=0x0000 ABS_OFFSET=0x48484848 result[12]=0x0100 ABS_OFFSET=0x4C4C4C4C result[13]=0x1100 ABS_OFFSET=0x50505050 result[14]=0x1111 ABS_OFFSET=0x54545454 result[15]=0x1111 ABS_OFFSET=0x58585858 result[16]=0x1111 ABS_OFFSET=0x5C5C5C5C result[17]=0x1111 ABS_OFFSET=0x60606060 result[18]=0x1111 ABS_OFFSET=0x64646464 result[19]=0x1111 ABS_OFFSET=0x68686868 result[1A]=0x1111 ABS_OFFSET=0x6C6C6C6C result[1B]=0x1111 ABS_OFFSET=0x70707070 result[1C]=0x1111 ABS_OFFSET=0x74747474 result[1D]=0x1111 ABS_OFFSET=0x78787878 result[1E]=0x1111 ABS_OFFSET=0x7C7C7C7C result[1F]=0x1111 Byte 0: (0x10 - 0x4c), middle value:0x2e Byte 1: (0x14 - 0x4c), middle value:0x30 Byte 2: (0x0c - 0x44), middle value:0x28 Byte 3: (0x0c - 0x48), middle value:0x2a MMDC0 MPWRDLC 11f42 TL = 0x2A28302E MMDC registers updated from calibration Write leveling calibration MMDC_MPWLDECTRL0 ch0 (0x021b080c) = 0x00250027 MMDC_MPWLDECTRL1 ch0 (0x021b0810) = 0x00450034 Read DQS Gating calibration MPDGCTRL0 PHY0 (0x021b083c) = 0x032E0334 MPDGCTRL1 PHY0 (0x021b0840) = 0x03320336 Read calibration MPRDDLCTL PHY0 (0x021b0848) = 0x3A2A302C Write calibration MPWRDLCTL PHY0 (0x021b0850) = 0x2A28302E Success: DDR calibration completed!!!1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

177

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

200

201

202

203

204

205

206

207

208

209

210

211

212

213

214

215

216

217

218

219

220

221

222

223

224

225

226

227

228

229

230

231

232

233

234

235

236

237

238

239

240

241

242

243

244

245

246

247

248

249

250

251

252

253

254

255

256

257

258

259

260

261

262

263

264

265

266

267

268

269

270

271

272

273

274

275

276

277

278

279

280

281

282

283

284

285

286

287

288

289

290

291

292

293

294

295

296

297

298

299

300

301

302

303

304

305

306

307

308

309

310

311

312

313

314

315

316

317

318

319

320

321

322

323

324

325

326

327

328

329

330

331

332

333

334

335

336

337

338

339

340

341

342

343

344

345

346

347

348

349

350

351

352

353

354

355

356

357

358

359

360

361

362

363

364

365

366

367

368

369

370

371

372

373

374

375

376

377

378

379

380

381

382

383

384

385

386

387

388

389

390

391

392

393

394

395

396

397

398

399

400

401

402

403

404

405

406

407

408

409

410

411

412

413

414

415

416

417

418

419

420

421

422

423

424

425

426

427

428

429

430

431

432

433

434

435

436

437

438

439

440

441

442

443

444

445

446

447

448

449

450

451

452

453

454

455

456

457

458

459

460

461

462

463

464

465

466

467

468

469

470

471

472

473

474

475

476

477

478

479

480

481

482

483

484

485

486

487

488

489

490

491

492

493

494

495

496

497

498

499

500

501

502

503

504

505

506

507

508

509

510

511

512

513

514

515

516

517

518

519

520

521

522

523

524

525

526

527

528

529

530

531

532

533

534

535

536

537

538

539

540

541

542

543

544

545

546

547

548

549

550

551

552

553

554

555

556

557

558

559

[/code]

Write leveling calibration MMDC_MPWLDECTRL0 ch0 (0x021b080c) = 0x00250027 MMDC_MPWLDECTRL1 ch0 (0x021b0810) = 0x00450034 Read DQS Gating calibration MPDGCTRL0 PHY0 (0x021b083c) = 0x032E0334 MPDGCTRL1 PHY0 (0x021b0840) = 0x03320336 Read calibration MPRDDLCTL PHY0 (0x021b0848) = 0x3A2A302C Write calibration MPWRDLCTL PHY0 (0x021b0850) = 0x2A28302E1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

[/code]

这里得到的这几个寄存器的值就是我们需要的,根据这几个值修改:

uboot中[.cfg][6]文件,例如:

/board/freescale/mx6sabresd/xxxxx.cfg

/* * Copyright (C) 2015 FEDEVEL * * SPDX-License-Identifier: GPL-2.0+ * * Refer docs/README.imxmage for more details about how-to configure * and create imximage boot image * * The syntax is taken as close as possible with the kwbimage */ /* image version */ IMAGE_VERSION 2 /* * Boot Device : one of * spi, sd (the board has no nand neither onenand) */ BOOT_FROM sd /* //============================================================================= // DDR Controller Registers //============================================================================= // Manufacturer: Micron // Device Part Number: MT41K256M16HA-125 // Clock Freq.: 528MHz // Density per CS in Gb: 8 // Chip Selects used: 1 // Number of Banks: 8 // Row address: 15 // Column address: 10 // Data bus width 32 //============================================================================= */ /* * Device Configuration Data (DCD) * * Each entry must have the format: * Addr-type Address Value * * where: * Addr-type register length (1,2 or 4 bytes) * Address absolute address of the register * value value to be stored in the register */ DATA 4 0x020e0798 0x000C0000 DATA 4 0x020e0758 0x00000000 DATA 4 0x020e0588 0x00000028 DATA 4 0x020e0594 0x00000028 DATA 4 0x020e056c 0x00000028 DATA 4 0x020e0578 0x00000028 DATA 4 0x020e074c 0x00000028 DATA 4 0x020e057c 0x00000028 DATA 4 0x020e058c 0x00000000 DATA 4 0x020e059c 0x00000028 DATA 4 0x020e05a0 0x00000028 DATA 4 0x020e078c 0x00000028 DATA 4 0x020e0750 0x00020000 DATA 4 0x020e05a8 0x00000028 DATA 4 0x020e05b0 0x00000028 DATA 4 0x020e0524 0x00000028 DATA 4 0x020e051c 0x00000028 DATA 4 0x020e0774 0x00020000 /**/ DATA 4 0x020e0784 0x00000028 DATA 4 0x020e0788 0x00000028 DATA 4 0x020e0794 0x00000028 DATA 4 0x020e079c 0x00000028 DATA 4 0x020e05ac 0x00000028 /**/ DATA 4 0x020e05b4 0x00000028 DATA 4 0x020e0528 0x00000028 DATA 4 0x020e0520 0x00000028 DATA 4 0x021b001c 0x00008000 /**/ DATA 4 0x021b0800 0xA1390003 DATA 4 0x021b080c 0x00250027 DATA 4 0x021b0810 0x00450034 DATA 4 0x021b083c 0x032E0334 DATA 4 0x021b0840 0x03320336 DATA 4 0x021b0848 0x3A2A302C DATA 4 0x021b0850 0x2A28302E DATA 4 0x021b081c 0x33333333 DATA 4 0x021b0820 0x33333333 DATA 4 0x021b0824 0x33333333 DATA 4 0x021b0828 0x33333333 DATA 4 0x021b08b8 0x00000800 DATA 4 0x021b0004 0x00020036 DATA 4 0x021b0008 0x09444040 DATA 4 0x021b000c 0x898E7955 DATA 4 0x021b0010 0xFF328F64 DATA 4 0x021b0014 0x01FF00DB DATA 4 0x021b0018 0x00011740 DATA 4 0x021b001c 0x00008000 DATA 4 0x021b002c 0x000026D2 DATA 4 0x021b0030 0x008E1023 DATA 4 0x021b0040 0x00000027 DATA 4 0x021b0000 0x84190000 DATA 4 0x021b001c 0x02088032 DATA 4 0x021b001c 0x00008033 DATA 4 0x021b001c 0x00048031 DATA 4 0x021b001c 0x09408030 DATA 4 0x021b001c 0x04008040 DATA 4 0x021b0020 0x00007800 DATA 4 0x021b0818 0x00022227 DATA 4 0x021b0004 0x00025576 DATA 4 0x021b0404 0x00011006 DATA 4 0x021b001c 0x00000000 /* set the default clock gate to save power */ DATA 4 0x020c4068 0x00C03F3F DATA 4 0x020c406c 0x0030FC03 DATA 4 0x020c4070 0x0FFFC000 DATA 4 0x020c4074 0x3FF00000 DATA 4 0x020c4078 0x00FFF300 DATA 4 0x020c407c 0x0F0000C3 DATA 4 0x020c4080 0x000003FF /* enable AXI cache for VDOA/VPU/IPU */ DATA 4 0x020e0010 0xF00000CF /* set IPU AXI-id0 Qos=0xf(bypass) AXI-id1 Qos=0x7 */ DATA 4 0x020e0018 0x007F007F DATA 4 0x020e001c 0x007F007F1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

[/code]

当然最后还需要重新编译下uboot,然后烧到板子上,启动:

U-Boot 2015.04-14468-gd7d7c43-dirty (Jun 24 2016 - 09:55:12)

CPU: Freescale i.MX6Q rev1.5 at 792 MHz

CPU: Temperature 40 C

Reset cause: POR

Board: MX6Q-Sabreauto revA

I2C: ready

DRAM: 1 GiB

PMIC: PFUZE100 ID=0x10

MMC: FSL_SDHC: 0

SF: Detected M25P32 with page size 256 Bytes, erase size 64 KiB, total 4 MiB

In: serial

Out: serial

Err: serial

Net: FEC [PRIME]

Boot from USB for mfgtools

Use default environment for mfgtools

Run bootcmd_mfg: run mfgtool_args;bootz loadaddr” role=”presentation” style=”position: relative;”>loadaddrloadaddr{initrd_addr} ${fdt_addr};

Hit any key to stop autoboot: 0

=>

相关文章推荐

- IMX6Q调试之 —– DDR3 32位移植

- IMX6Q调试之 ----- DDR3 32位移植

- [IMX6Q][Android5.1]移植笔记 --- 调试串口只能输出不能输入

- U-Boot的移植之(四)调试篇:下载U-Boot到目标板进行调试

- 嵌入式Linux之Kernel(裁减移植)启动调试技术

- 移植MiniGUI的调试记录

- Qualcomm平台camera调试移植入门

- 充电IC驱动调试----移植充电IC bq25601

- Android系统移植与调试之------->如何修改开机动画的两种方式剖析

- [IMX6Q][Android5.1]移植笔记 --- uboot_v2015.04移植

- ijkplayer-android 移植与调试日志

- 32位程序移植到64位需要考虑的问题

- IMX6Q 触摸屏调试(TSC2007驱动)

- Qualcomm平台camera调试移植入门

- Android系统级深入开发——移植与调试

- Android系统移植与调试之------->build.prop生成过程分析

- 移植32位程序到64位时碰到精度问题

- Android系统移植与调试之------->如何修改Android的默认语言、默认时区

- [IMX6Q][Android5.1]移植笔记 --- LCD背光控制

- Mipi LCD 通用移植调试流程