I2S音频总线学习(四)I2S接口设计

2017-12-13 11:06

288 查看

I2S音频总线学习(四)I2S接口设计

一、数据发送端的设计

图1 发送端

随着WS信号的改变,导出一个WSP脉冲信号,进入并行移位寄存器装入DATA LEFT或DATA RIGHT,从而输出数据被激活。串行数据在时钟下降沿移出。串行数据的默认输入是0,因此所有位于最低位(LSB)后的数据将被设置为0。

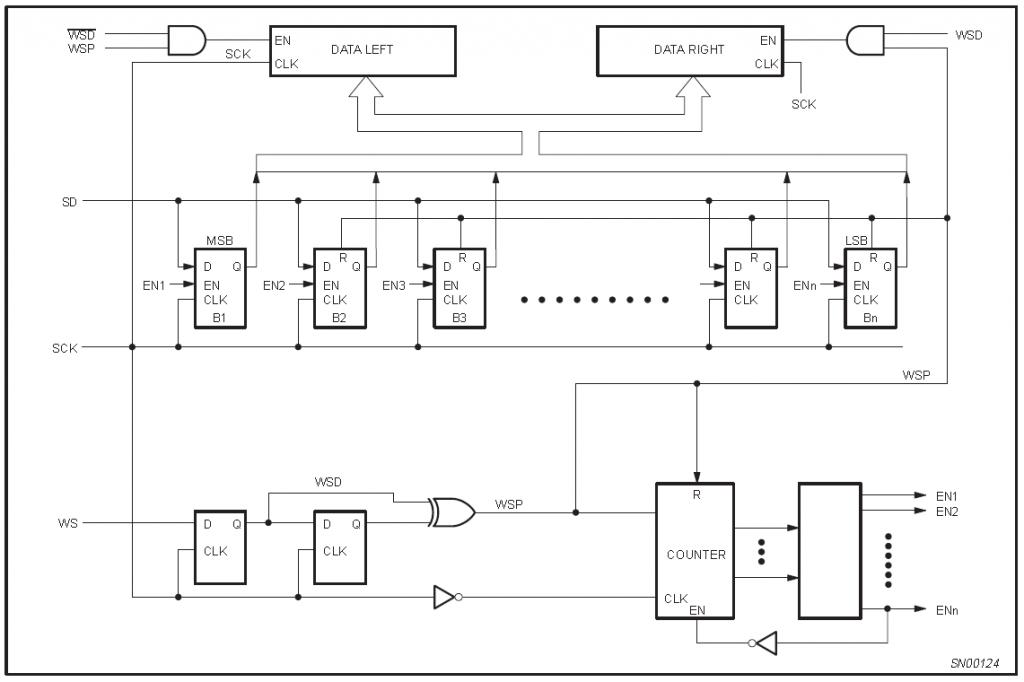

二、数据接收端的设计

图2 接收端

随着第一个WS信号的改变,WSP在SCK信号的下降沿重设计数器。在“1 out of n”译码器对计数器数值进行译码后,第一个串行的数据(MSB)在SCK时钟信号的上升沿被存放进入B1,随着计数器的增长,接下来的数据被依次存放进入B2到Bn中。在下一个WS信号改变的时候,数据根据WSP脉冲的变化被存放进入左(声道)锁存器或者右(声道)锁存器,并且将B2一Bn的数据清除以及计数器重设,如果有冗余的数据则最低位之后的数据将被忽略。注意:译码器和计数器(虚线内的部分)可以被一个n比特移位寄存器所代替,如图3所示。

当计数计满时,即ENn为高时,计算器EN信号变成低电平,使计数器停止计数,同时也使串并转换模块停止接收数据。

图3 接收端

相关文章推荐

- I2S音频总线学习(四)I2S接口设计

- I2S音频总线学习(四)I2S接口设计

- I2S音频总线学习(三)S3C2440的I2S控制器

- I2S音频总线学习(二)I2S总线协议

- I2S音频总线学习(二)I2S总线协议

- I2S音频总线学习(二)I2S总线协议

- I2S音频总线学习(一)数字音频技术

- I2S总线接口设计(Verilog)

- I2S音频总线学习(一)数字音频技术

- I2S音频总线学习(二)I2S总线协议

- I2S音频总线学习(三)S3C2440的I2S控制器

- [Craftor原创] I2S总线接口设计(Verilog)

- I2S音频总线学习(二)

- I2S音频总线学习(三)S3C2440的I2S控制器

- I2S音频总线学习(一)数字音频技术

- I2S音频总线学习(二)I2S总线协议

- I2S音频总线学习

- I2S音频总线学习(一)数字音频技术

- I2S音频总线学习(一)数字音频技术

- [Craftor原创] I2S总线接口设计(Verilog)