SylixOS在ZYNQ7000上划分CACHE

2017-11-29 09:58

302 查看

范围

本文档介绍了SylixOS在Xilinx Zynq-7000开发板上如何进行L2 Cache划分。

在AMP模式中,core 0与core 1共用512K L2 Cache,这势必会引起两个核的Cache竞争问题。

用处

通常情况下,L2 Cache被core 0,core 1共享。

core 0的内存访问操作可能会清除core 1所使用的L2缓存内容,从而使core 1的软件性能有不确定性。

有时,我们需要为core 0 或core 1提供更多的确定性行为。

尤其是架构为AMP时。

L2 Cache划分可以满足这种需求。

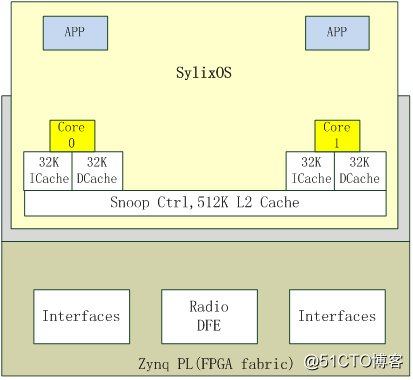

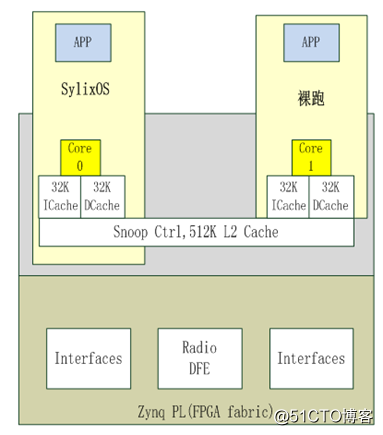

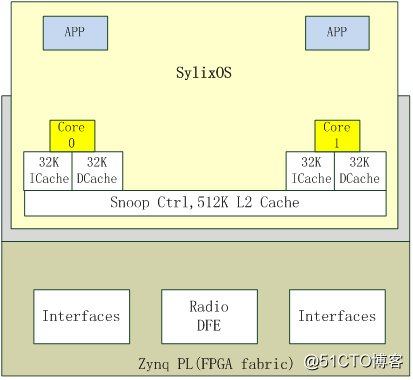

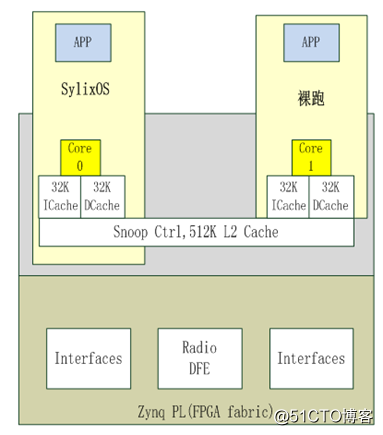

如图 2.1、图 2.2为SMP与AMP架构图。

图 2.1 SMP架构图

图 2.2 AMP架构图

原理

通过寄存器的控制可以将L2 Cache锁定在不同core上。

这让用户可以将L2 Cache的功能保留在特定的core上。

Cache way是分区的宽度,Zynq的L2 Cache有8 Cache ways。

L2 Cache控制器只能被锁定8个不同的方式。

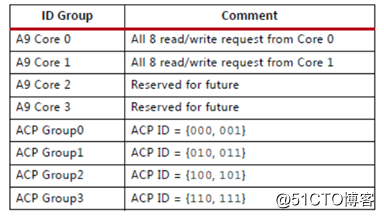

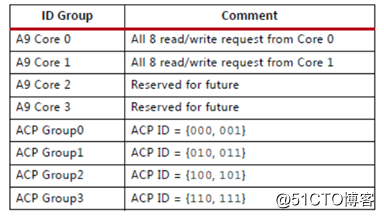

如图 3.1所示,在Zynq 7000中,Cortex-A9 MP核的64个AXI被分为8个可以锁定的组。

图 3.1分组

配置

具体寄存器说明参照Xilinx 官方数据手册UG585。

配置1:通常情况(L2 Cache 被core 0和core 1共享)。

Reg9_d_lockdown0 = 0x0;

Reg9_1_lockdown0 = 0x0;

Reg9_d_lockdown1 = 0x0;

Reg9_1_lockdown1 = 0x0;

配置2:4-0-4方式,每个核用一半(core 0使用Cache way【0..3】;core 1使用Cache way【4..7】)。

reg9_d_lockdown0 = 0xFFF0;

reg9_1_lockdown0 = 0xFFF0;

reg9_d_lockdown1 = 0xFF0F;

reg9_1_lockdown1 = 0xFF0F;

配置3:2-4-2方式(core 0使用Cache way【0..1】;core 1使用Cache way【6..7】;两个核共享Cache way【2..5】)。

reg9_d_lockdown0 = 0xFFC0;

reg9_1_lockdown0 = 0xFFC0;

reg9_d_lockdown1 = 0xFF03;

reg9_1_lockdown1 = 0xFF03;

本文档介绍了SylixOS在Xilinx Zynq-7000开发板上如何进行L2 Cache划分。

在AMP模式中,core 0与core 1共用512K L2 Cache,这势必会引起两个核的Cache竞争问题。

用处

通常情况下,L2 Cache被core 0,core 1共享。

core 0的内存访问操作可能会清除core 1所使用的L2缓存内容,从而使core 1的软件性能有不确定性。

有时,我们需要为core 0 或core 1提供更多的确定性行为。

尤其是架构为AMP时。

L2 Cache划分可以满足这种需求。

如图 2.1、图 2.2为SMP与AMP架构图。

图 2.1 SMP架构图

图 2.2 AMP架构图

原理

通过寄存器的控制可以将L2 Cache锁定在不同core上。

这让用户可以将L2 Cache的功能保留在特定的core上。

Cache way是分区的宽度,Zynq的L2 Cache有8 Cache ways。

L2 Cache控制器只能被锁定8个不同的方式。

如图 3.1所示,在Zynq 7000中,Cortex-A9 MP核的64个AXI被分为8个可以锁定的组。

图 3.1分组

配置

具体寄存器说明参照Xilinx 官方数据手册UG585。

配置1:通常情况(L2 Cache 被core 0和core 1共享)。

Reg9_d_lockdown0 = 0x0;

Reg9_1_lockdown0 = 0x0;

Reg9_d_lockdown1 = 0x0;

Reg9_1_lockdown1 = 0x0;

配置2:4-0-4方式,每个核用一半(core 0使用Cache way【0..3】;core 1使用Cache way【4..7】)。

reg9_d_lockdown0 = 0xFFF0;

reg9_1_lockdown0 = 0xFFF0;

reg9_d_lockdown1 = 0xFF0F;

reg9_1_lockdown1 = 0xFF0F;

配置3:2-4-2方式(core 0使用Cache way【0..1】;core 1使用Cache way【6..7】;两个核共享Cache way【2..5】)。

reg9_d_lockdown0 = 0xFFC0;

reg9_1_lockdown0 = 0xFFC0;

reg9_d_lockdown1 = 0xFF03;

reg9_1_lockdown1 = 0xFF03;

相关文章推荐

- SylixOS在ZYNQ中划分CACHE

- SylixOS下DMA操作带cache的地址时的处理

- SylixOS NandFlash读CACHE

- zynq7000的cache

- SylixOS NandFlash读CACHE

- Linux中Buffer和Cache的区别

- 记录一些自己对java程序设计的大概划分吧

- C#读取IE的Cache

- TLBs,页结构cache和无效协议 阅读总结

- Maven最佳实践:模块划分

- 冒险岛问题:划分岛屿与陆地(矩阵求四邻域个数问题)

- C++程序中的内存划分 - iu_81的专栏 - CSDNBlog

- Oracle RAC 10g – Cache Fusion(original link is under the title)

- SylixOS WIFI

- 计算机体系结构--Cache

- Asp.Net中Cache操作类

- Oracle V$ROWCACHE

- cocos2dx-3.0(33) 中的缓存TextureCache、SPriteFrameCache、AnimationCache

- ASimpleCache缓存框架之简单使用

- 页面中使用cache缓存对象