VTC Fsync_out信号分析

2017-09-26 19:28

253 查看

VTC Fsync_out信号分析

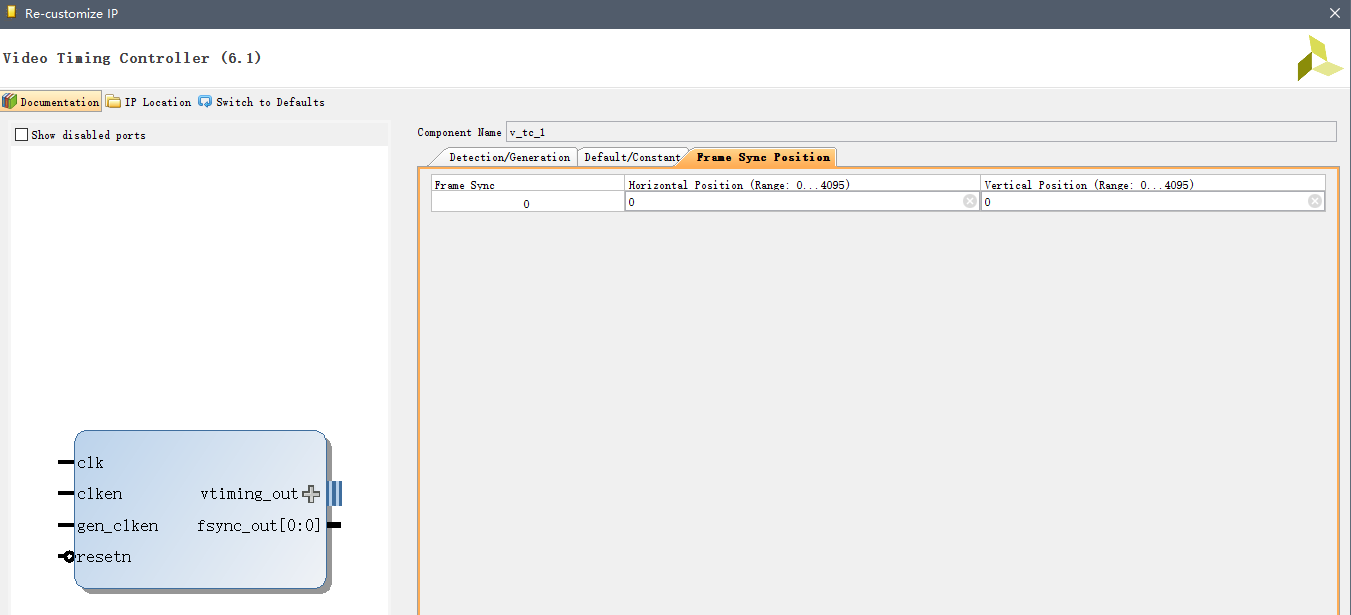

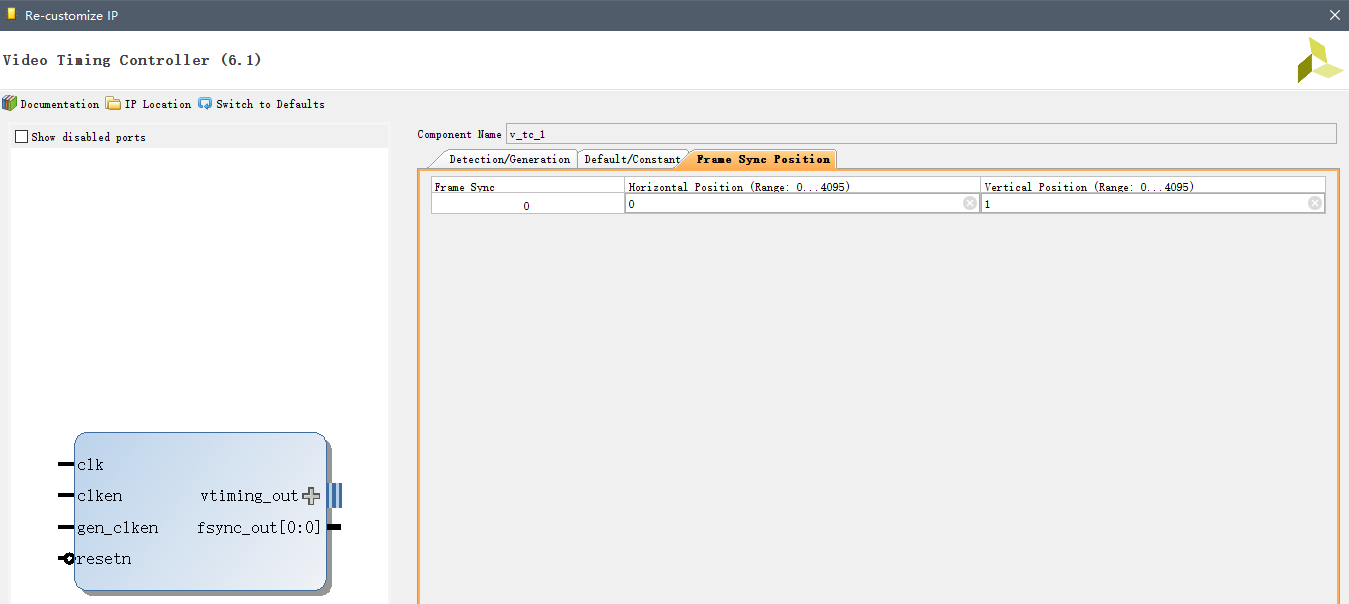

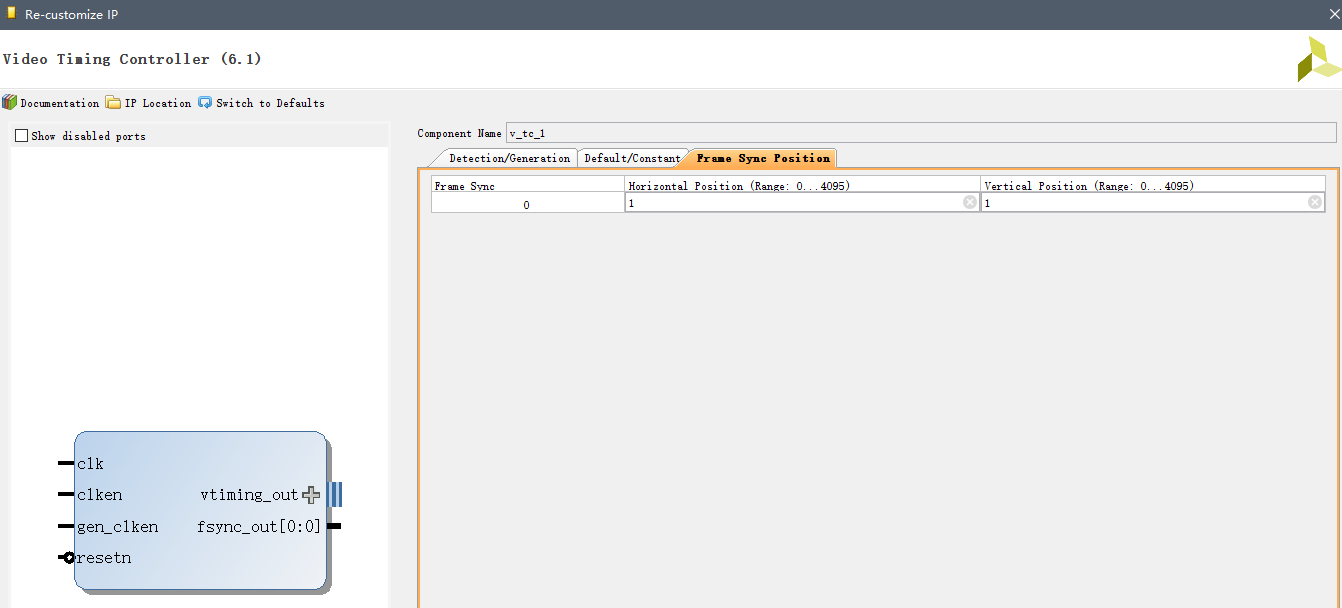

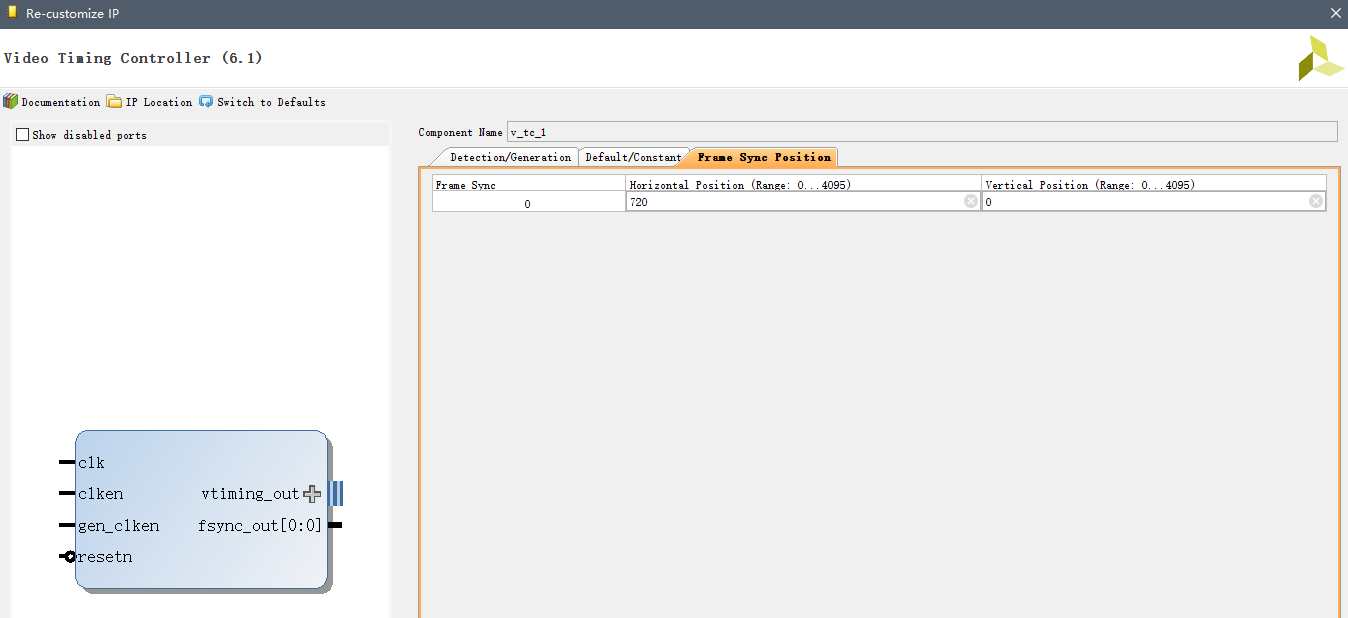

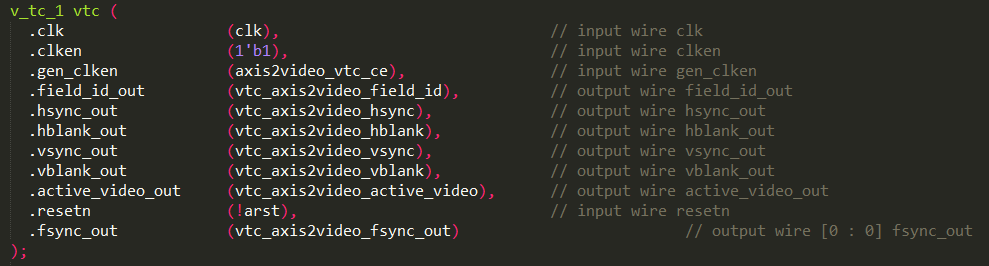

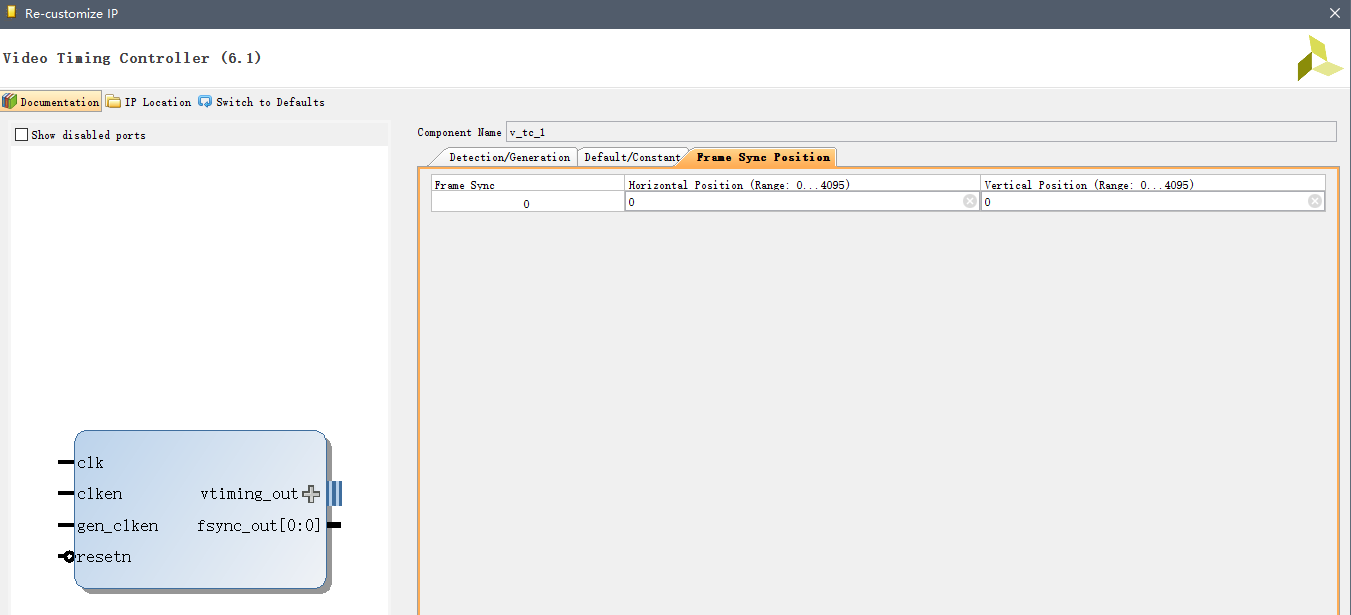

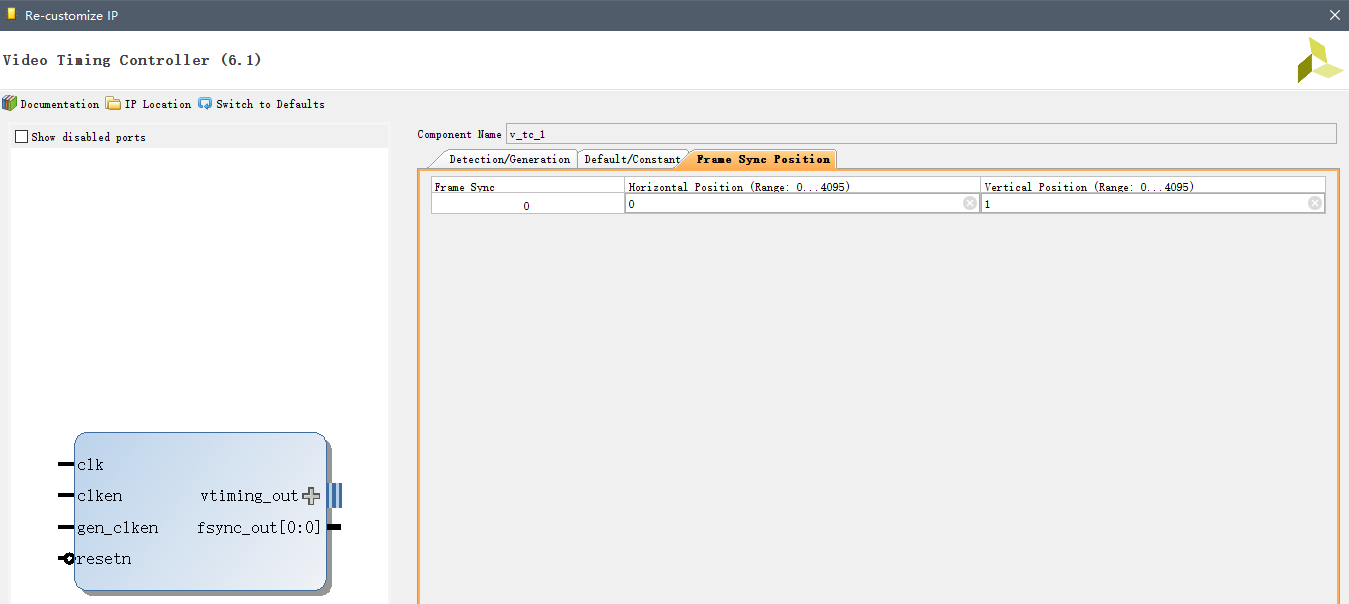

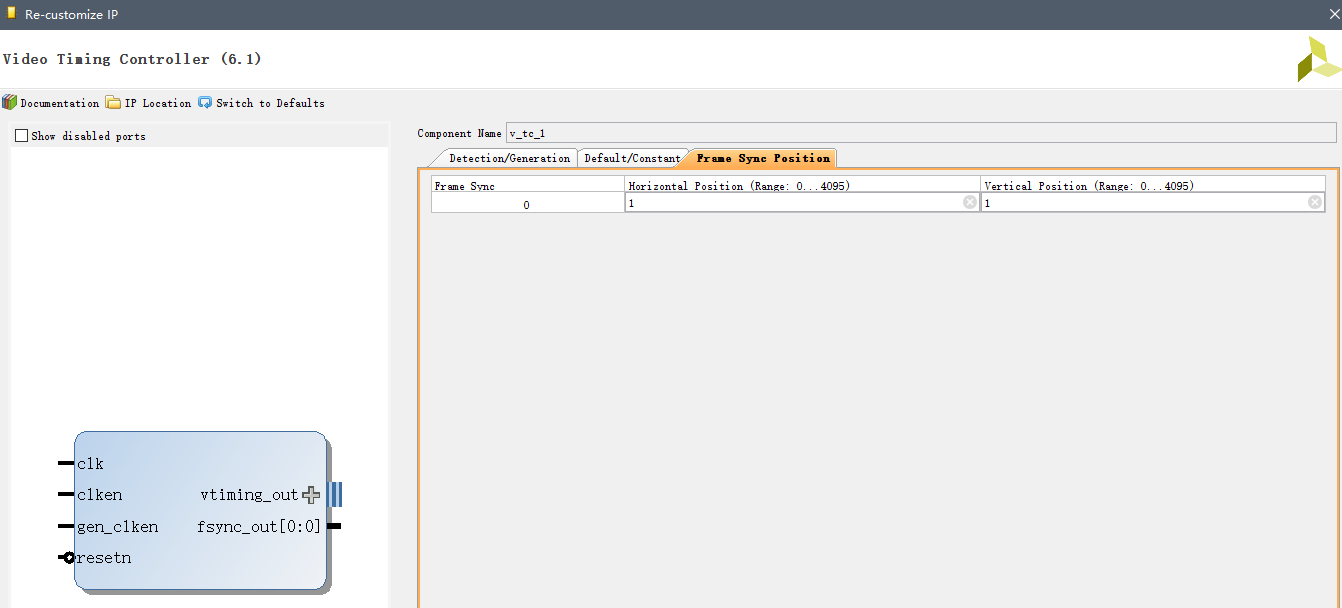

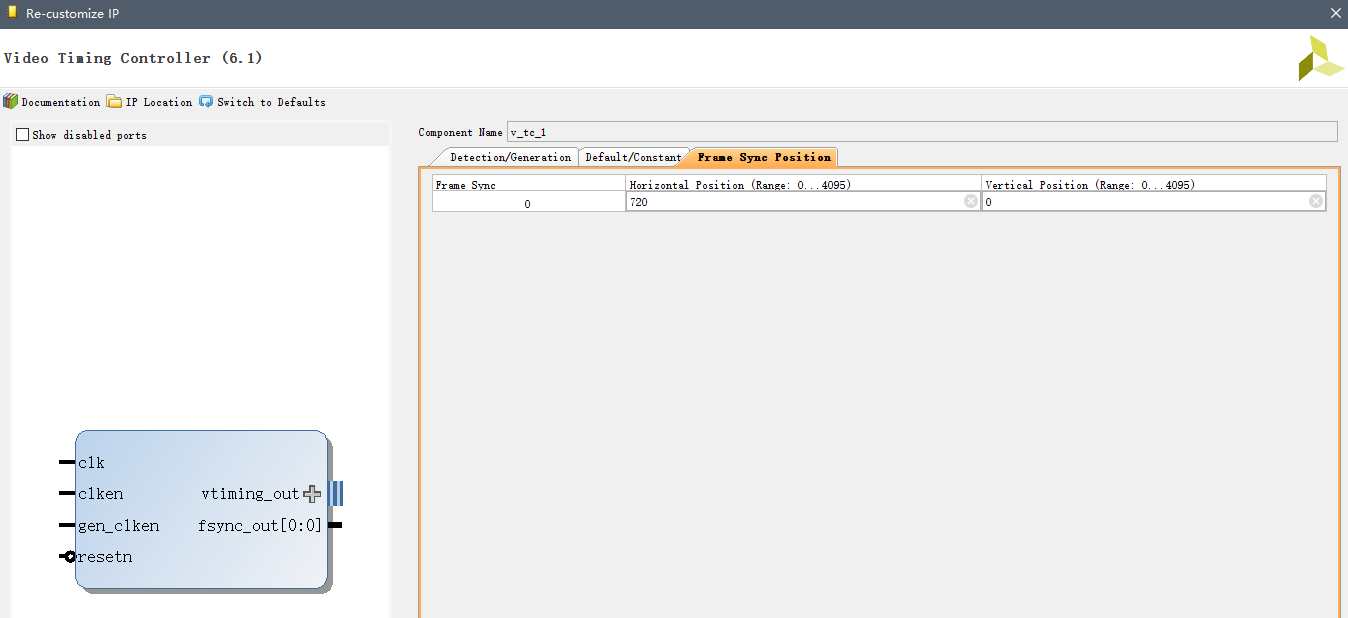

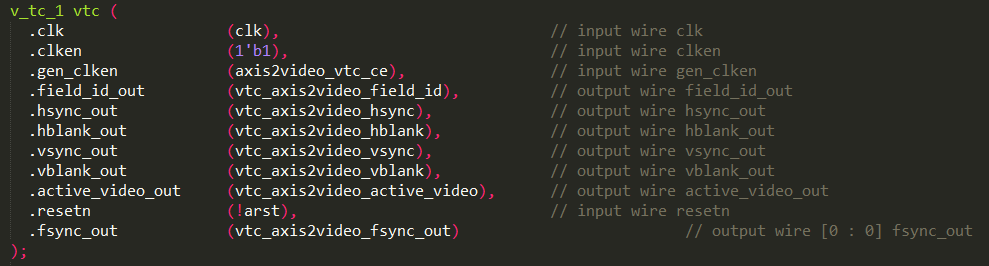

1.GUI配置

Vertical position的值289是根据Frame/Field 0 Vertical settings一栏中sync start来设置的。

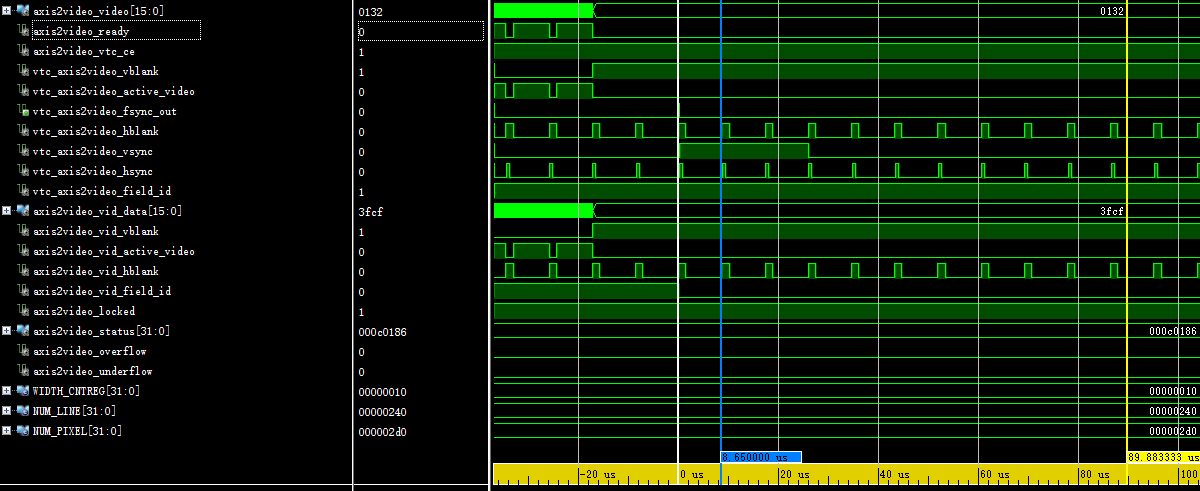

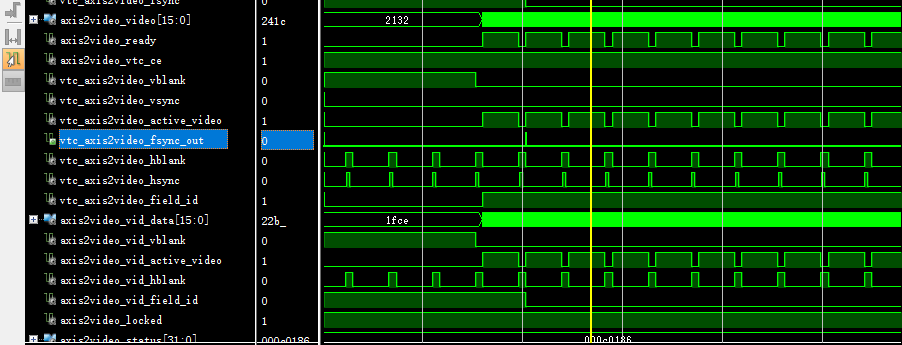

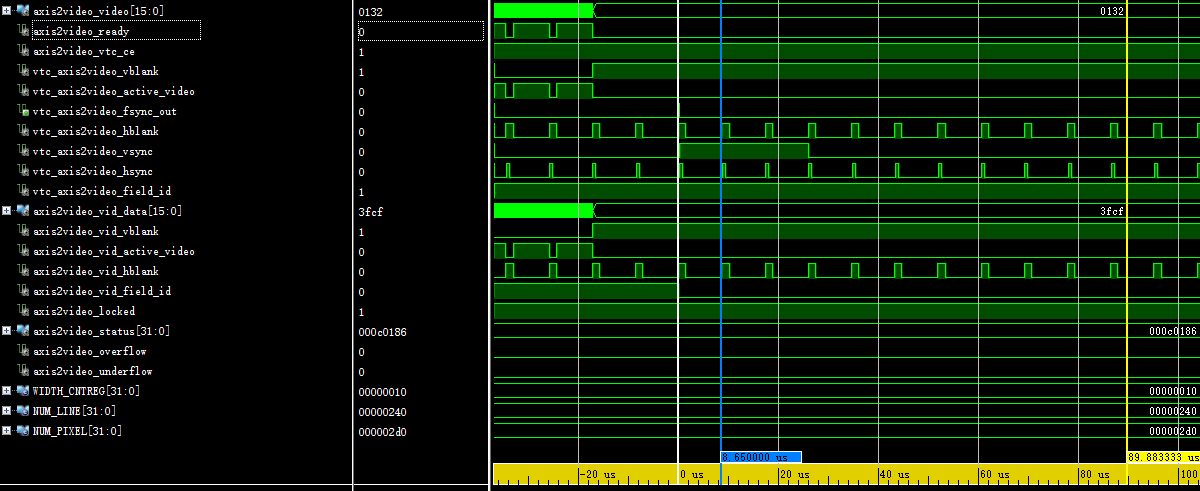

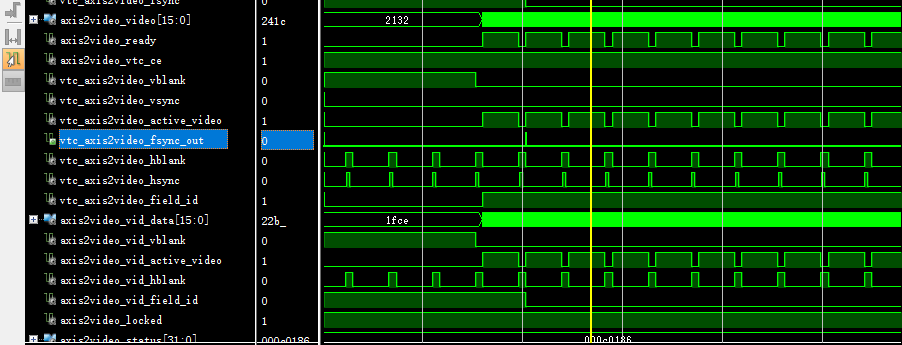

数两个fsync_out 信号之间有多少个hblank:

得到两个fsync_out 信号之间的时间差为:2.69568ms

每两个hblank之间的信号时间间隔为:8.65us

则可以计算两个fsync_out 信号之间有2695.68/8.65=312个hblank(行)

如果:

2704.32/8.64 = 313

如果:

如果:

Fsync_out信号的规律算是弄清楚了。

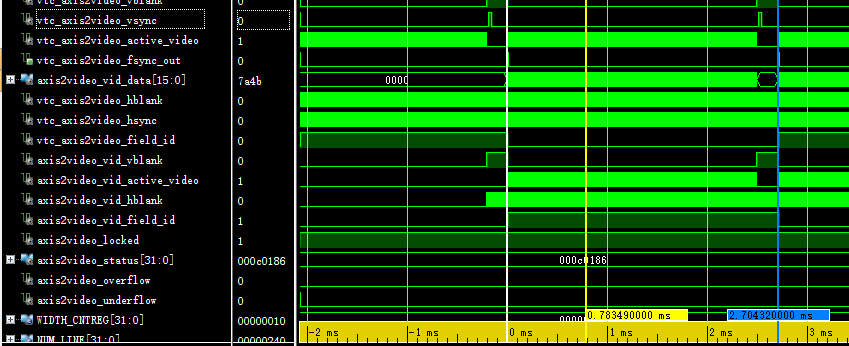

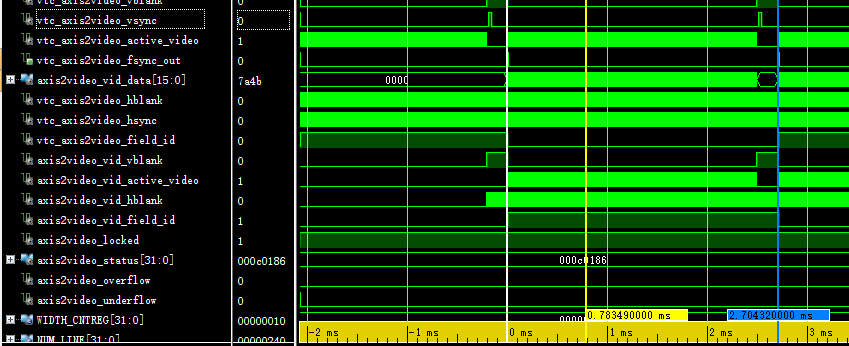

下一步弄清楚vtc_field_id 信号:

一行的时间为:8.65us

Vtc_field_id = 1的时间:2.69568ms

Vtc_field_id周期总时间为:5.4ms

2695.68/8.65 = 312

(5.4-2.69568)*1000/8.65=313

如果:

1.GUI配置

Vertical position的值289是根据Frame/Field 0 Vertical settings一栏中sync start来设置的。

数两个fsync_out 信号之间有多少个hblank:

得到两个fsync_out 信号之间的时间差为:2.69568ms

每两个hblank之间的信号时间间隔为:8.65us

则可以计算两个fsync_out 信号之间有2695.68/8.65=312个hblank(行)

如果:

2704.32/8.64 = 313

如果:

如果:

Fsync_out信号的规律算是弄清楚了。

下一步弄清楚vtc_field_id 信号:

一行的时间为:8.65us

Vtc_field_id = 1的时间:2.69568ms

Vtc_field_id周期总时间为:5.4ms

2695.68/8.65 = 312

(5.4-2.69568)*1000/8.65=313

如果:

相关文章推荐

- 信号完整性分析3——反射现象

- 数字集成电路设计-10-关于采用两级触发器实现双时钟域信号同步方法的分析与验证

- Libev源码分析06:异步信号同步化--sigwait、sigwaitinfo、sigtimedwait和signalfd

- 通信信号与系统分析(二)

- Nginx源码分析 - 主流程篇 - 平滑重启和信号控制

- [转]ORA-3136(WARNING Inbound Connection Timed Out)分析

- dispc_reg_in ,dispc_reg_out , dispc_reg_merge函数功能的分析

- Java中System.out.printf参数传递错误分析与修正

- Java之OutOfMemoryError简单分析

- 基于信号完整性分析的高速数字PCB 的设计方法

- 信号完整性分析方法-1-信号的串扰

- 通信原理-确定信号分析

- Linux信号(signal) 机制分析

- Linux信号(signal) 机制分析

- Maemo Linux手机平台系列分析:9 Maemo平台开发之 使用D-Bus信号做异步操作

- System.out 源码分析

- 信号完整性分析和印制电路板

- Linux信号(signal、sigaction) 机制分析

- 从qtcreator的实例来简单分析qml的信号与响应函数

- 图像信号分析基础