[转载]用verilog写一段代码,实现消除一个glitch

2017-09-04 15:03

357 查看

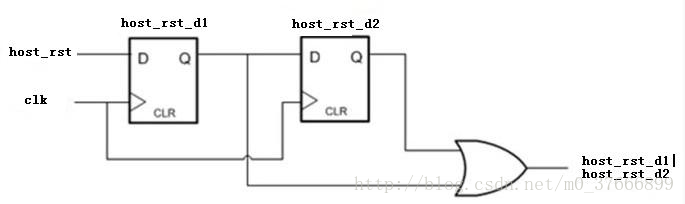

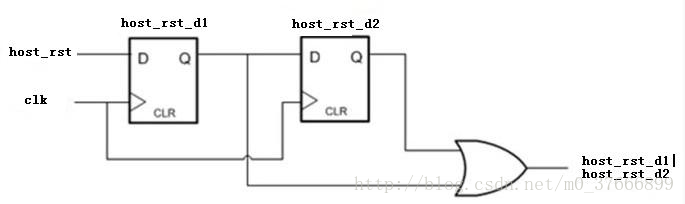

滤掉小于1个周期glitch的原理图如下:

verilog代码实现如下:

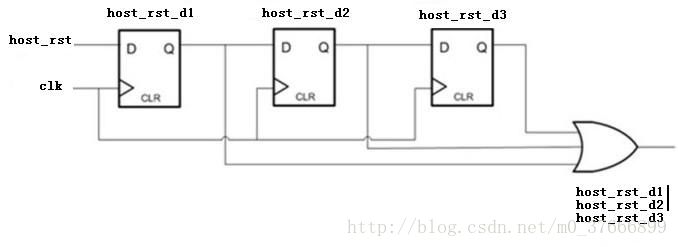

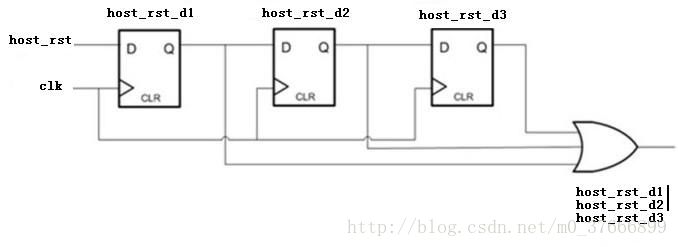

滤掉大于1个周期且小于2个周期glitch的原理图如下:

verilog代码实现如下:

verilog代码实现如下:

module digital_filter_(clk_in,rst,host_rst,host_rst_filter); input clk_in; input rst; input host_rst; output host_rst_filter; reg host_rst_d1; reg host_rst_d2; always@(posedge clk_in or negedge rst) begin if(~rst) begin host_rst_d1 <= 1'b1; host_rst_d2 <= 1'b1; end else begin host_rst_d1 <= host_rst; host_rst_d2 <= host_rst_d1; end end assign host_rst_filter = host_rst_d1 | host_rst_d2; endmodule

滤掉大于1个周期且小于2个周期glitch的原理图如下:

verilog代码实现如下:

module digital_filter_(clk_in,rst,host_rst,host_rst_filter); input clk_in; input rst; input host_rst; output host_rst_filter; reg host_rst_d1; reg host_rst_d2; reg host_rst_d3; always@(posedge clk_in or negedge rst) begin if(~rst) begin host_rst_d1 <= 1'b1; host_rst_d2 <= 1'b1; host_rst_d3 <= 1'b1; end else begin host_rst_d1 <= host_rst; host_rst_d2 <= host_rst_d1; host_rst_d3 <= host_rst_d2; end end assign host_rst_filter = host_rst_d1 | host_rst_d2 | host_rst_d3; endmodule

相关文章推荐

- [转载]一个简单的内存缓存实现--一段漂亮的代码

- **请写出一段Python代码实现删除一个list里面的重复元素

- 求一段CSS样式代码;要求是Table的标签样式,实现Table标签奇数行显示一个颜色;偶数行显示另外一种颜色

- 发一个用状态机实现的按键检测是VERILOG代码

- 实现一个无锁的Stack,并写一段测试代码(多线程访问),证明这个Stack是线程安全的。给出程序以及运行的截图。

- 2.7 请写出一段Python代码实现删除一个list里面的重复元素

- 面试题---请写出一段Python代码实现删除一个list里面的重复元素

- 用一段代码实现一个链表倒序(C++实现)

- 如何实现多个线程同步 (2013-11-10 12:07:24)转载▼ 标签: it 在编写一个类时,如果该类中的代码可能运行于多线程环境下,那么就要考虑同步的问题,Java实现线程同步的方法很多

- python - 列表分组技巧 #写出一段 Python 代码,实现分组一个 list 里面的元素,如 [1,2,3,...100]变成 [[1,2,3],[4,5,6]....]

- 实现一个学生的成绩的录入与查询成绩(不算原创,也不算转载,是根据他人代码改动而来)

- 转载:利用MS SQL实现异构数据库的分布式查询的t-sql代码

- 一段实现选择框javascript代码的重构

- 关于AdoHelper的一个方便之处的代码实现细节

- 分形介绍 && 一个简单的Kotch curve实现代码

- hchxxzx--》一个实现图片上传/产生缩略图/在上传图片上写字功能的完整页面代码

- 一个简单的AJAX实现,基于C#的ASP.Net,包括服务器端的程序代码

- 实现Hibernate 分页的一段代码

- 抄来一段编程实现锁定计算机的代码(支持2000以上的系统)

- 用几行代码实现排序 (转载)