时钟分频方法---verilog代码

2017-08-07 11:02

471 查看

时钟分频方法---verilog代码

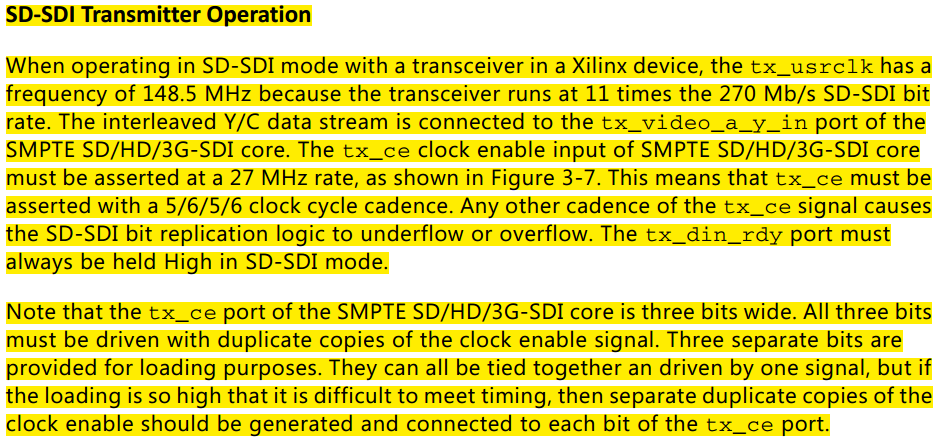

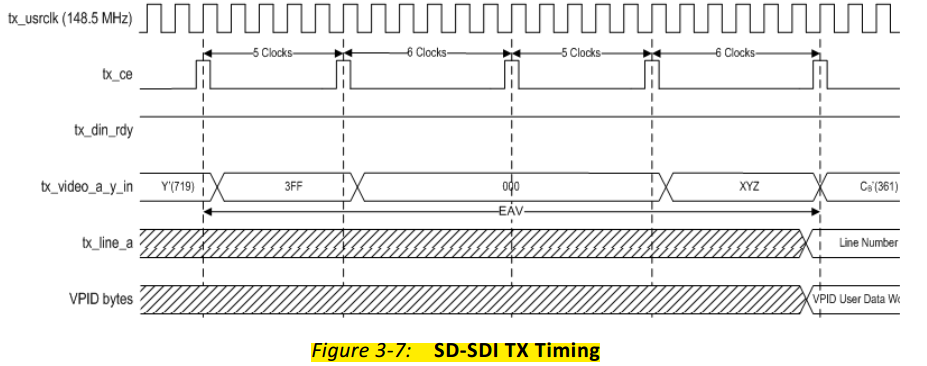

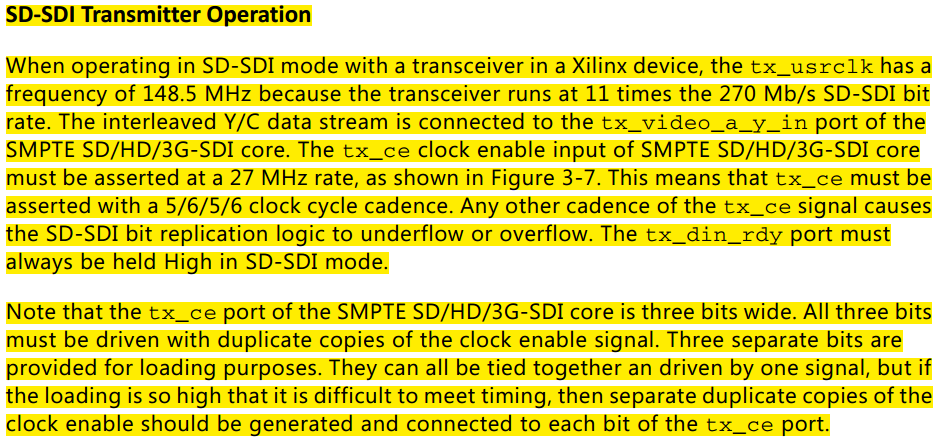

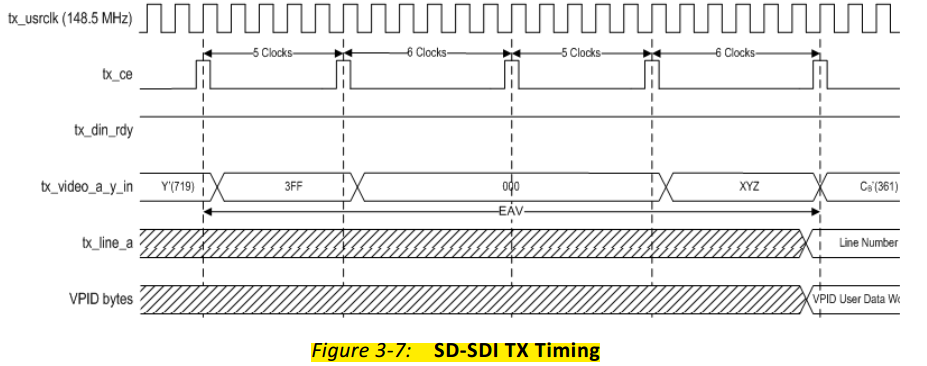

本文以SDI播出部分的工程为例,来说明一种时钟分频的写法。SD-SDI工程中播出时钟tx_usrclk为148.5MHz,但tx_video_a_y_in端的数据采样与tx_ce(门控时钟)有关。通过对tx_usrclk时钟进行分频,5clocks---6clocks---5clocks---6clocks,得到tx_ce信号。

verilog代码写法如下:

重点关注tx_gen_sd_ce = 11'b00000100001信号,用来生成5/6/5/6序列。

每当tx_usrclk上升沿到来时,tx_gen_sd_ce左移一位,最高位移到最低位。tx_sd_ce取tx_gen_sd_ce的最高位,需要注意的是:tx_gen_sd_ce 和tx_sd_ce是同时变化的,都由tx_usrclk上升沿控制。

当tx_gen_sd_ce = 10000100000时,tx_sd_ce为高电平,由此开始,当下一次tx_sd_ce为高电平时,tx_gen_sd_ce = 10000010000需要花费5clocks,当tx_sd_ce再次为高电平时,tx_gen_sd_ce = 10000100000需要花费6clocks,循环下去,由此就产生了5/6/5/6序列。

本文以SDI播出部分的工程为例,来说明一种时钟分频的写法。SD-SDI工程中播出时钟tx_usrclk为148.5MHz,但tx_video_a_y_in端的数据采样与tx_ce(门控时钟)有关。通过对tx_usrclk时钟进行分频,5clocks---6clocks---5clocks---6clocks,得到tx_ce信号。

verilog代码写法如下:

reg [2:0] tx_ce = 3'b111;

reg tx_sd_ce = 1'b0;

reg [10:0] tx_gen_sd_ce = 11'b00000100001; // Generates 5/6/5/6 cadence SD-SDI TX clock enable

wire tx_ce_mux; // Used to generate the tx_ce signals

//

// TX clock enable generator

//

// sd_ce runs at 27 MHz and is asserted at a 5/6/5/6 cadence

// tx_ce is always 1 for 3G-SDI and HD-SDI and equal to sd_ce for SD-SDI

//

// Create 3 identical but separate copies of the clock enable for loading purposes.

//

always @ (posedge tx_usrclk)

if (tx_fabric_reset) //复位信号来源于?

tx_gen_sd_ce <= 11'b00000100001;

else

tx_gen_sd_ce <= {tx_gen_sd_ce[9:0], tx_gen_sd_ce[10]}; //此段代码用于产生

always @ (posedge tx_usrclk)

tx_sd_ce <= tx_gen_sd_ce[10];

assign tx_ce_mux = tx_mode == 2'b01 ? tx_gen_sd_ce[10] : 1'b1;

always @ (posedge tx_usrclk)

tx_ce <= {3 {tx_ce_mux}};重点关注tx_gen_sd_ce = 11'b00000100001信号,用来生成5/6/5/6序列。

always @ (posedge tx_usrclk)

if (tx_fabric_reset) //复位信号来源于?

tx_gen_sd_ce <= 11'b00000100001;

else

tx_gen_sd_ce <= {tx_gen_sd_ce[9:0], tx_gen_sd_ce[10]}; //此段代码用于产生always @ (posedge tx_usrclk) tx_sd_ce <= tx_gen_sd_ce[10];

每当tx_usrclk上升沿到来时,tx_gen_sd_ce左移一位,最高位移到最低位。tx_sd_ce取tx_gen_sd_ce的最高位,需要注意的是:tx_gen_sd_ce 和tx_sd_ce是同时变化的,都由tx_usrclk上升沿控制。

当tx_gen_sd_ce = 10000100000时,tx_sd_ce为高电平,由此开始,当下一次tx_sd_ce为高电平时,tx_gen_sd_ce = 10000010000需要花费5clocks,当tx_sd_ce再次为高电平时,tx_gen_sd_ce = 10000100000需要花费6clocks,循环下去,由此就产生了5/6/5/6序列。

相关文章推荐

- verilog时钟分频设计

- verilog时钟分频设计(来源:http://blog.csdn.net/moon9999/article/details/75020355)

- Verilog HDL的时钟分频(2次方分频)

- Verilog时钟n分频

- [smart210] 通过PLL设置各时钟频率的方法以及代码注释

- Verilog HDL 学习篇——任意时钟分频

- verilog代码中避免出现latch方法

- FPGA中用verilog分频实现方法

- verilog时钟分频设计(整合模块)

- 谷歌推出理解神经网络的新方法SVCCA | NIPS论文+代码

- vim之高效编辑verilog代码(2)

- Window8.1 64位无法使用Debug命令的解决方法[附牛人代码]

- J2EE开发中减少编写代码工作量的几种方法

- Android - 百度地图打包混淆代码后地图崩溃的解决方法

- MVVM 后台代码调用viewModel方法

- Struts 2最新0day破坏性漏洞(远程任意代码执行)等的重现方法

- javascript入门·动态的时钟,显示完整的一些方法,新年倒计时

- Selenium应用代码(常见封装的方法一)

- 拼接html代码相对美观的方法

- eclipse以及以此为原型的软件,设置代码字体大小的方法