声音采集播放及IIS接口介绍

2017-06-21 00:00

411 查看

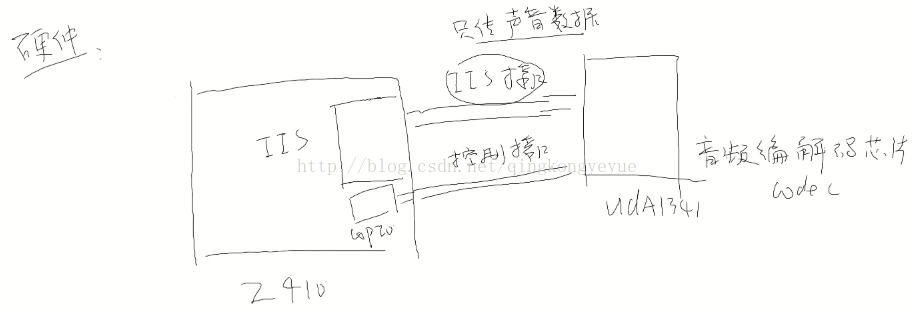

1、硬件接口

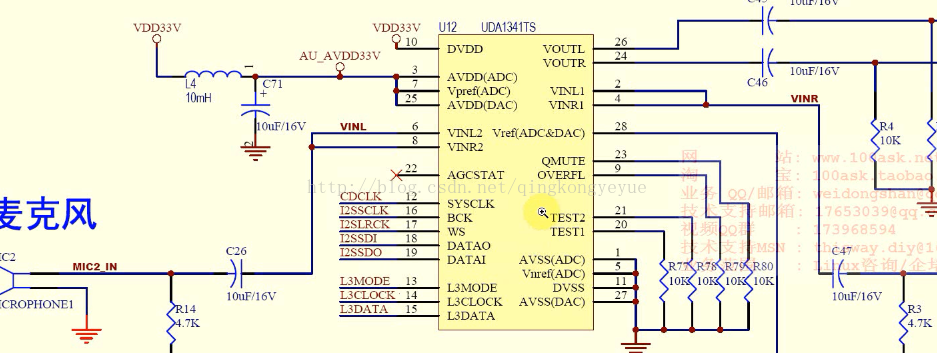

(1)硬件原理图

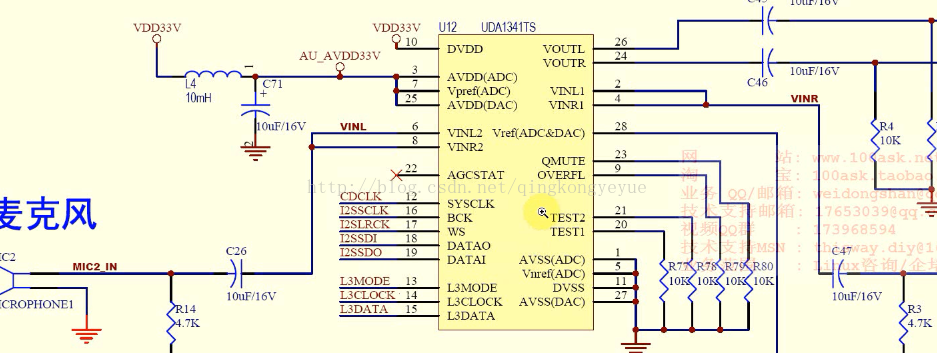

IIS部分用来传声音和收声音,L3接口部分用来控制声音。

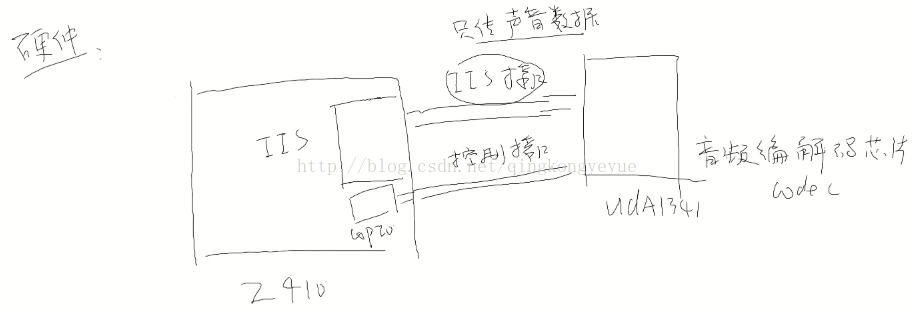

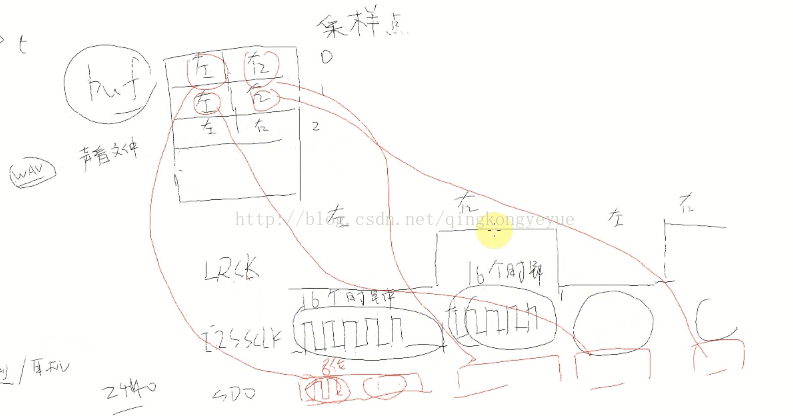

(2)2410和声卡连接图

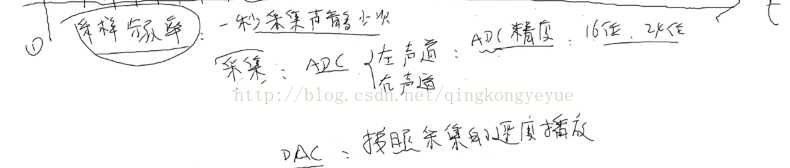

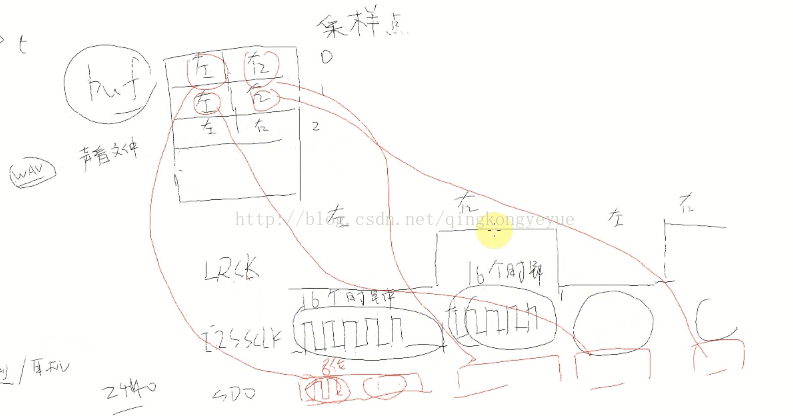

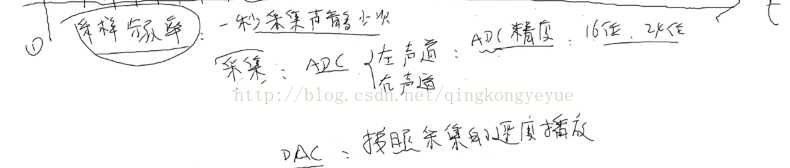

(3)声音采集

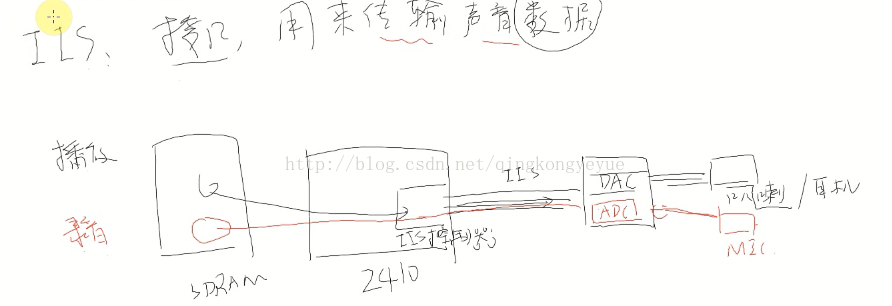

(4)录音和播放

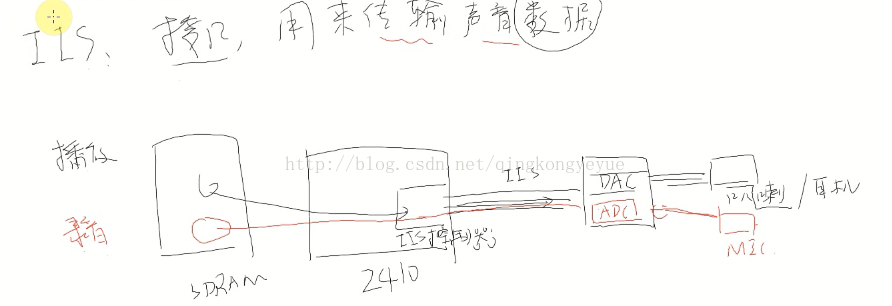

2、IIS

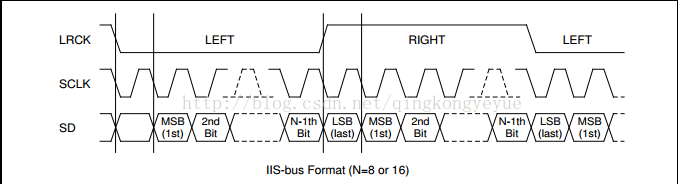

(1)

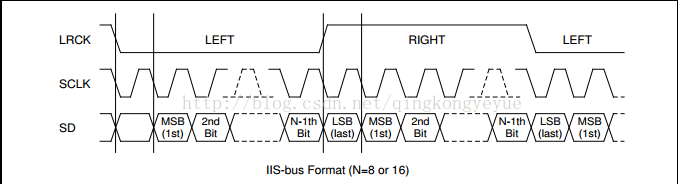

当LRCK是低电平时传输的是左声道数据,是高电平时传输的是右声道数据。是采样频率,

SCLK是位时钟,每个时钟传输1位数据。

还有CDCLK,系统时钟,用于让芯片工作于一定的频率下。2410提供给编解码芯片的。

(2)最多支持16位数据

(3)传输8位数据时,因为有16个时钟,所以后面八位填0

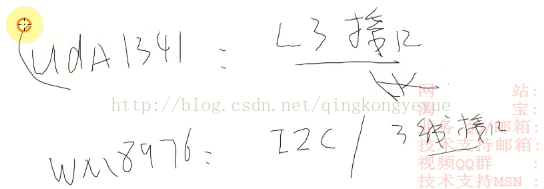

3、L3接口不等于3线接口

4、L3接口各线功能

1、UDA1341TS这颗CODEC和S3C2440的硬件接口为L3和IIS.其中,L3为实现UDA1341TS这颗CODEC内部寄存器配置的硬件接口,而IIS则为音频数据流的数据接口.

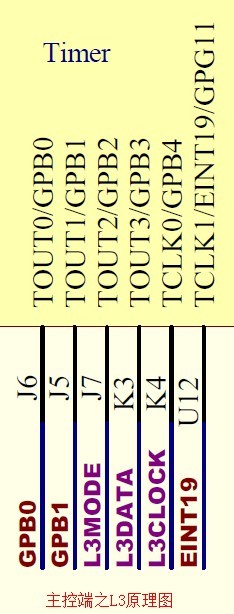

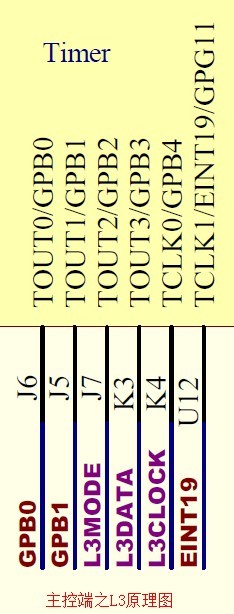

1-2.主控端原理图:

S3C2440-L3原理图:

2.数据手册及通讯协议:

主控需要根据一定的协议(如IIC、SPI、IIS、L3等)和设备端通讯,从而达到数据的交互效果.而这过程往往是基于某种协议来实现设备端内部寄存器的配置而达到设备功能的设置动作.这些信息往往需要从SOC的数据手册和DEV的数据手册获取.

2-1.UDA1341TS的DATASHEET:

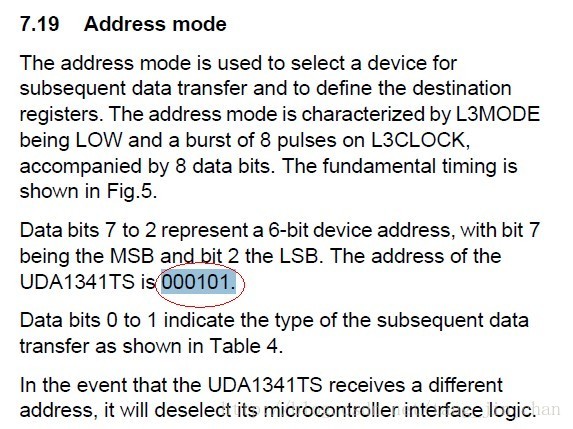

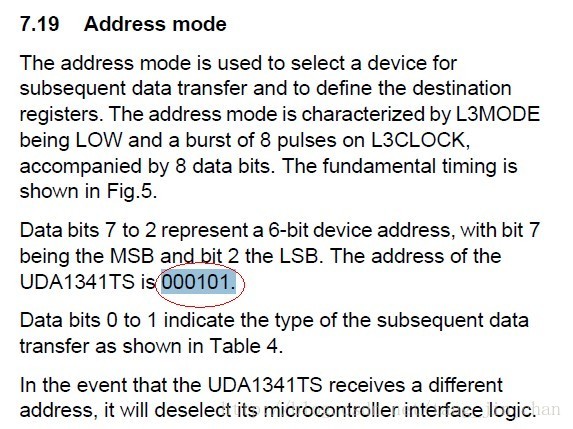

我们要达到控制某颗IC内部的信息,往往是通过其寄存器的读写实现的.下面针对UDA1341TS这颗CODEC的数据手册来看一下其内部寄存器.在这里实现UDA1341TS的内部寄存器操作是通过L3总线实现的.类似IIC总线协议,L3总线上也可以挂多个设备,每个设备都要有一个唯一的地址.UDA1341TS的设备地址为0x5.见数据手册:

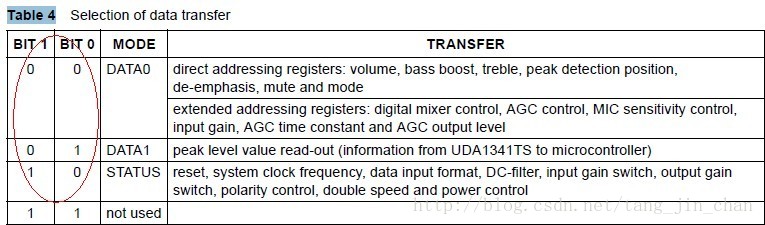

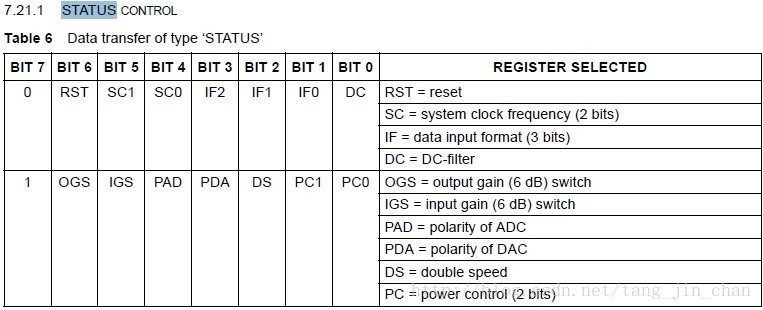

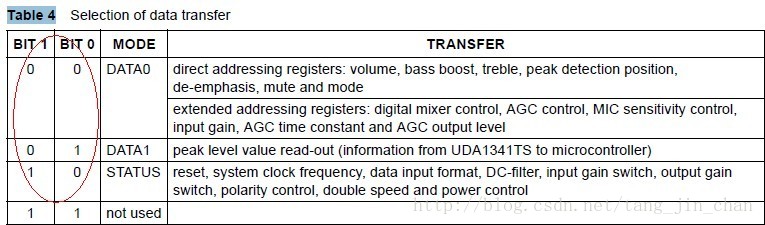

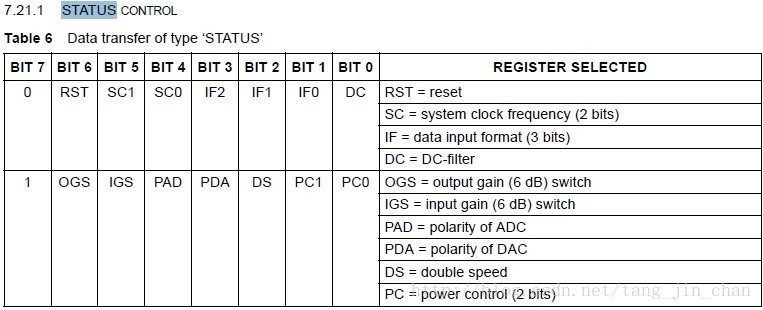

其中第一个byte中,bit[7]~bit[2]表示UDA1341TS的设备地址,见上图红色标识部分:000101.而bit[1]~bit[0]表示后续传输的数据类型.一共有三种类型(还有一种保留未使用).如下图:

00表示DATA0,01表示DATA1,10表示STATUS.这里其实就是指UDA1341TS的内部寄存器的地址.因此,

00010100b表示是DATA0的地址; 用于控制音量

00010101b表示是DATA1的地址; 表示读回一些信息

00010110b表示是STATUS的地址; 表示状态信息(时钟,数据位宽)

00010111b保留.

因此,sound/soc/codecs/uda134x.h中宏定义便轻易理解:

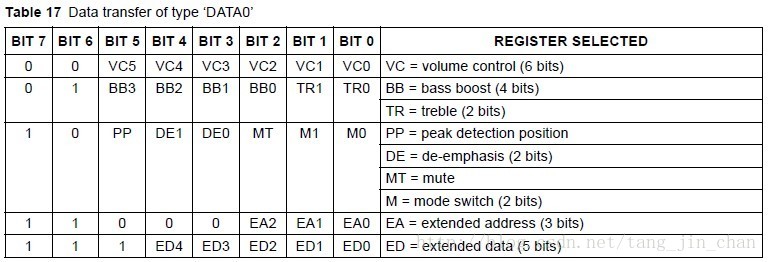

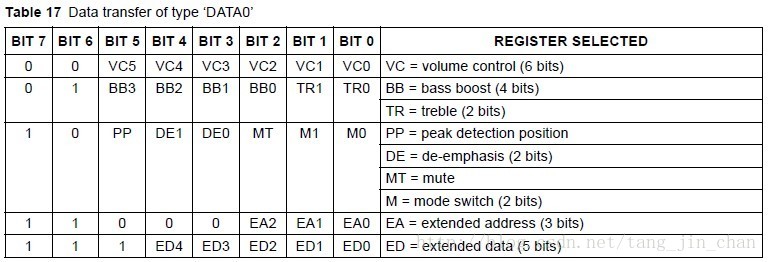

其中,DATA0里面就包含了音量的控制:

用于设置音量

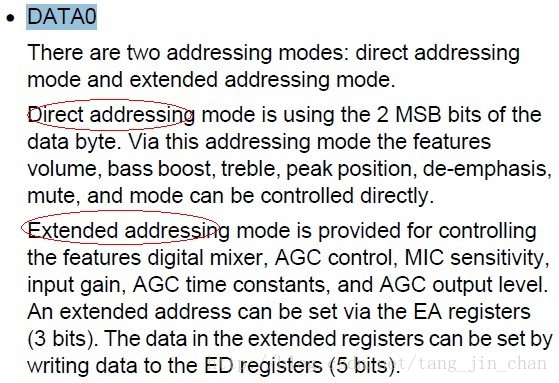

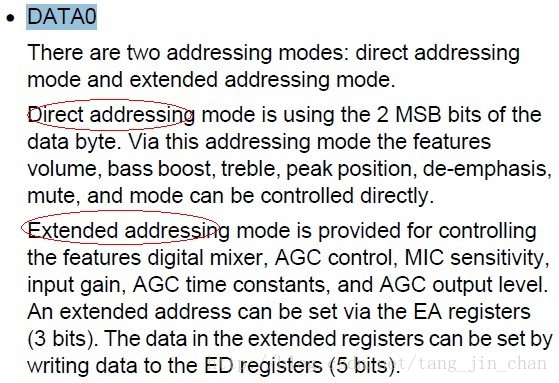

其中,往DATA0这个寄存器写入一些特定的数值还可以进入"扩展地址"模式,见上图中的EAn(n = 2,1,0)一栏.根据其数据手册.如下:

当进入EA模式,必须通过ED进行设置.因此,EA的基地址为0xC0,ED的基地址为0xE0.因此,sound/soc/codecs/uda134x.h下面的宏便很容易理解了:

同样,EAn有三个位(n = 0,1,2).其偏移地址为0x0到0x7.因此,sound/soc/codecs/uda134x.h下面的宏便很容易理解:

当处理EA模式下,可以实现增益、MIC灵敏度的设置.如下:

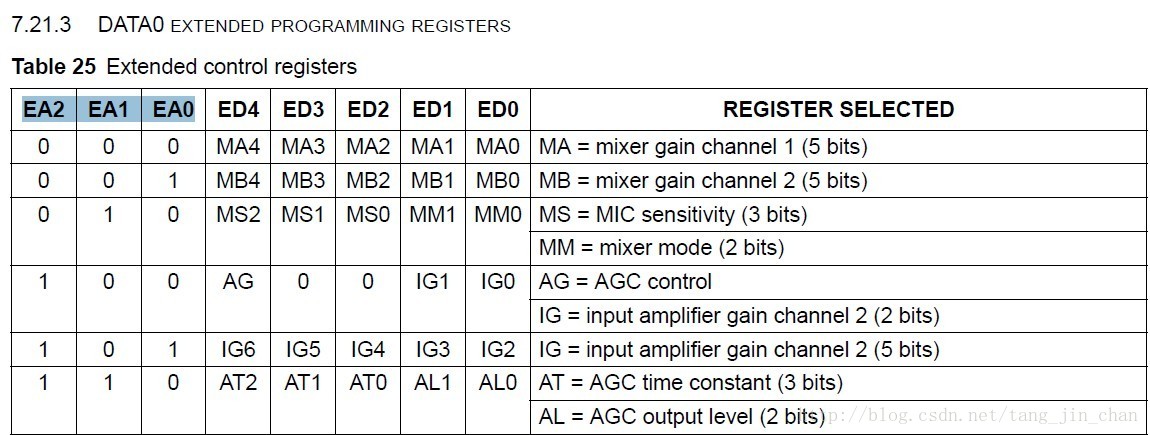

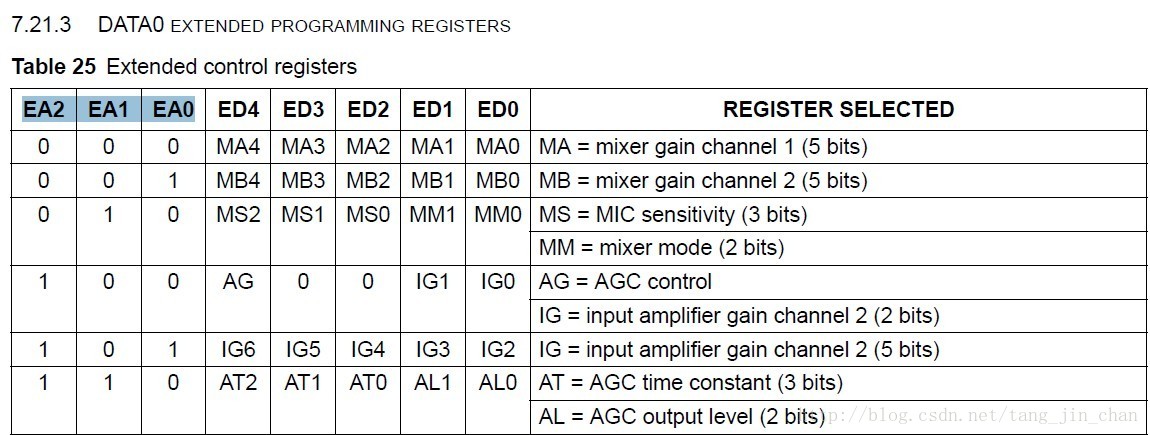

其中,DATA1表示峰值级别:

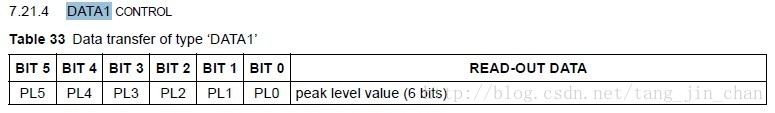

其中,STATUS包括里面IC系统的功能控制,比如复位:看最高位是0还是1.

2-2.S3C2440相关的DATASHEET:

S3C2440和UDA1341TS的硬件接口主要分两部分:L3和IIS.

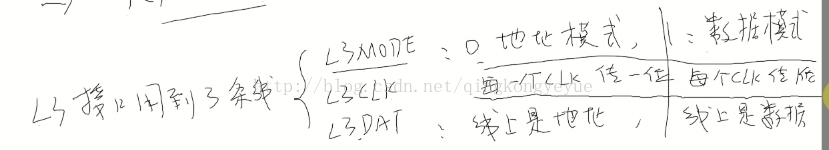

2-2-1.L3

其中,UDA1341TS的L3三根线L3MODE、L3DATA、L3CLOCK分别接到S3C2440的GPB2、GPB3、GPB4.因此,只能通过模拟L3时序协议来实现和UDA1341TS通讯配置.其中L3分为地址模式和数据模式.

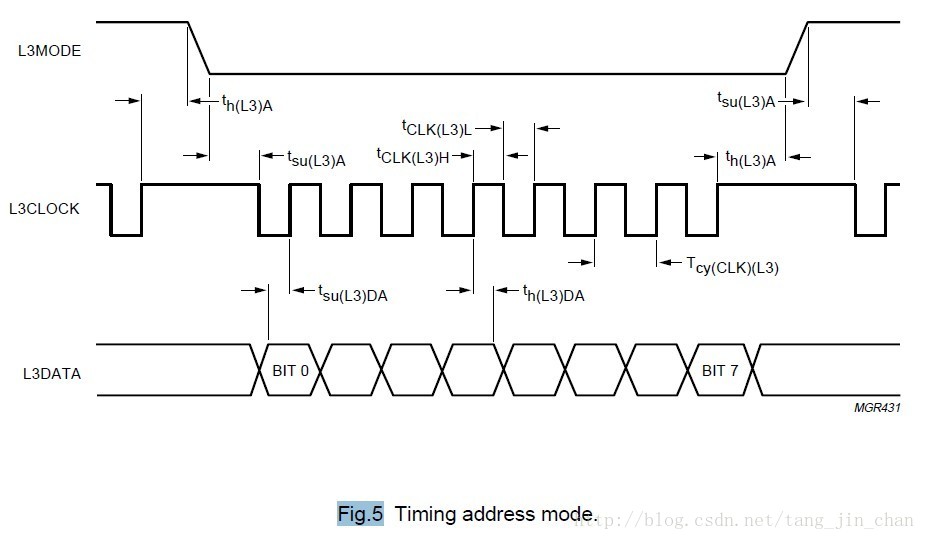

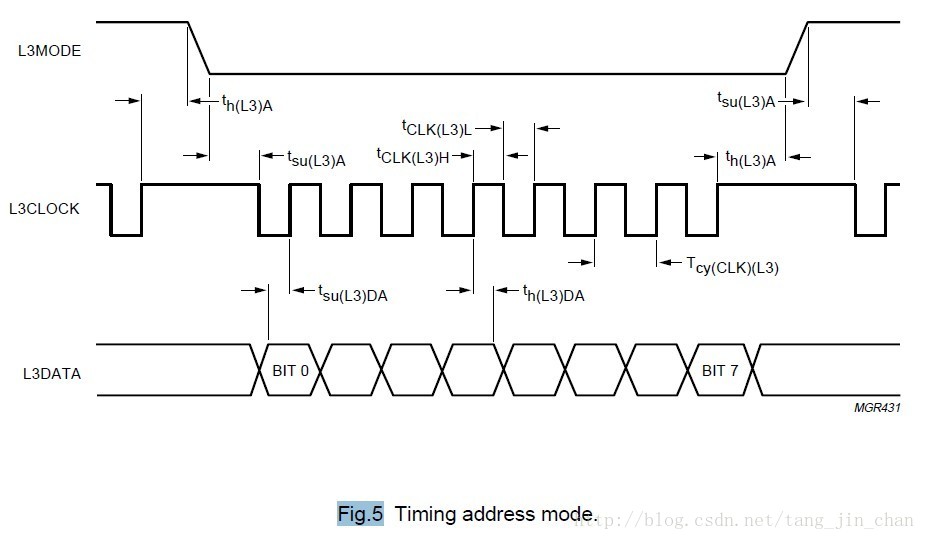

地址模式对应的协议时序图如下:

由此时序图可知,L3MODE处于低电平,在L3CLOCK的上升沿的时候,L3DATA上的数据被识别.因此,用GPIO模拟.

对应sound/soc/codecs/l3.c下面代码:

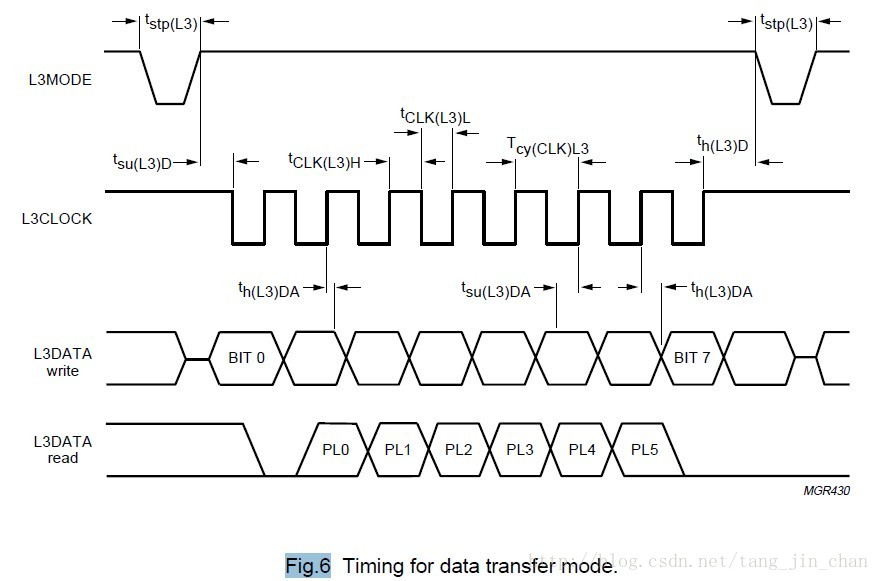

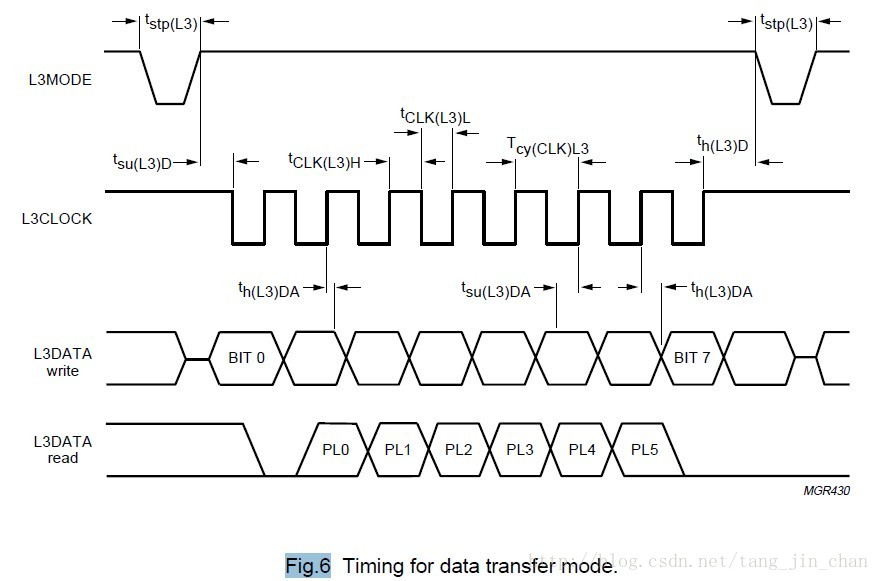

数据模式对应的协议时序图如下:

由此时序图可知,L3MODE处于高电平,在L3CLOCK的上升沿时L3DATA线上的数据被识别.因此,用GPIO模拟.

对应sound/soc/codecs/l3.c下面代码:

2-2-2.IIS

S3C2440内部集成了IIS控制单元.对外引出了五个引脚:IISDO、IISDI、IISSCLK、IISLRCK和CDCLK.由IIS的协议可知:

[注:]采样频率fs对频率的设置至关重要,常用的fs有8kHz、16kHz、22.05kHz、44.1kHz、48kHz、96kHz等

(1)硬件原理图

IIS部分用来传声音和收声音,L3接口部分用来控制声音。

(2)2410和声卡连接图

(3)声音采集

(4)录音和播放

2、IIS

(1)

当LRCK是低电平时传输的是左声道数据,是高电平时传输的是右声道数据。是采样频率,

SCLK是位时钟,每个时钟传输1位数据。

还有CDCLK,系统时钟,用于让芯片工作于一定的频率下。2410提供给编解码芯片的。

(2)最多支持16位数据

(3)传输8位数据时,因为有16个时钟,所以后面八位填0

3、L3接口不等于3线接口

4、L3接口各线功能

1、UDA1341TS这颗CODEC和S3C2440的硬件接口为L3和IIS.其中,L3为实现UDA1341TS这颗CODEC内部寄存器配置的硬件接口,而IIS则为音频数据流的数据接口.

1-2.主控端原理图:

S3C2440-L3原理图:

2.数据手册及通讯协议:

主控需要根据一定的协议(如IIC、SPI、IIS、L3等)和设备端通讯,从而达到数据的交互效果.而这过程往往是基于某种协议来实现设备端内部寄存器的配置而达到设备功能的设置动作.这些信息往往需要从SOC的数据手册和DEV的数据手册获取.

2-1.UDA1341TS的DATASHEET:

我们要达到控制某颗IC内部的信息,往往是通过其寄存器的读写实现的.下面针对UDA1341TS这颗CODEC的数据手册来看一下其内部寄存器.在这里实现UDA1341TS的内部寄存器操作是通过L3总线实现的.类似IIC总线协议,L3总线上也可以挂多个设备,每个设备都要有一个唯一的地址.UDA1341TS的设备地址为0x5.见数据手册:

其中第一个byte中,bit[7]~bit[2]表示UDA1341TS的设备地址,见上图红色标识部分:000101.而bit[1]~bit[0]表示后续传输的数据类型.一共有三种类型(还有一种保留未使用).如下图:

00表示DATA0,01表示DATA1,10表示STATUS.这里其实就是指UDA1341TS的内部寄存器的地址.因此,

00010100b表示是DATA0的地址; 用于控制音量

00010101b表示是DATA1的地址; 表示读回一些信息

00010110b表示是STATUS的地址; 表示状态信息(时钟,数据位宽)

00010111b保留.

因此,sound/soc/codecs/uda134x.h中宏定义便轻易理解:

其中,DATA0里面就包含了音量的控制:

用于设置音量

其中,往DATA0这个寄存器写入一些特定的数值还可以进入"扩展地址"模式,见上图中的EAn(n = 2,1,0)一栏.根据其数据手册.如下:

当进入EA模式,必须通过ED进行设置.因此,EA的基地址为0xC0,ED的基地址为0xE0.因此,sound/soc/codecs/uda134x.h下面的宏便很容易理解了:

#define UDA134X_EXTADDR_PREFIX 0xC0 #define UDA134X_EXTDATA_PREFIX 0xE0

同样,EAn有三个位(n = 0,1,2).其偏移地址为0x0到0x7.因此,sound/soc/codecs/uda134x.h下面的宏便很容易理解:

#define UDA134X_EA000 0 #define UDA134X_EA001 1 #define UDA134X_EA010 2 #define UDA134X_EA011 3 #define UDA134X_EA100 4 #define UDA134X_EA101 5 #define UDA134X_EA110 6 #define UDA134X_EA111 7

当处理EA模式下,可以实现增益、MIC灵敏度的设置.如下:

其中,DATA1表示峰值级别:

其中,STATUS包括里面IC系统的功能控制,比如复位:看最高位是0还是1.

2-2.S3C2440相关的DATASHEET:

S3C2440和UDA1341TS的硬件接口主要分两部分:L3和IIS.

2-2-1.L3

其中,UDA1341TS的L3三根线L3MODE、L3DATA、L3CLOCK分别接到S3C2440的GPB2、GPB3、GPB4.因此,只能通过模拟L3时序协议来实现和UDA1341TS通讯配置.其中L3分为地址模式和数据模式.

地址模式对应的协议时序图如下:

由此时序图可知,L3MODE处于低电平,在L3CLOCK的上升沿的时候,L3DATA上的数据被识别.因此,用GPIO模拟.

对应sound/soc/codecs/l3.c下面代码:

/*

* Send one byte of data to the chip. Data is latched into the chip on

* the rising edge of the clock.

*/

static void sendbyte(struct l3_pins *adap, unsigned int byte)

{

int i;

for (i = 0; i < 8; i++) {

adap->setclk(0);

udelay(adap->data_hold);//Tclk(L3)L-Tsu(L3)DA

adap->setdat(byte & 1);

udelay(adap->data_setup);//Tsu(L3)DA

adap->setclk(1);

udelay(adap->clock_high);//Th(L3)DA

byte >>= 1;

}

}数据模式对应的协议时序图如下:

由此时序图可知,L3MODE处于高电平,在L3CLOCK的上升沿时L3DATA线上的数据被识别.因此,用GPIO模拟.

对应sound/soc/codecs/l3.c下面代码:

/*

* Send a set of bytes to the chip. We need to pulse the MODE line

* between each byte, but never at the start nor at the end of the

* transfer.

*/

static void sendbytes(struct l3_pins *adap, const u8 *buf,

int len)

{

int i;

for (i = 0; i < len; i++) {

if (i) {

udelay(adap->mode_hold);

adap->setmode(0);

udelay(adap->mode);

}

adap->setmode(1);

udelay(adap->mode_setup);

sendbyte(adap, buf[i]);

}

}2-2-2.IIS

S3C2440内部集成了IIS控制单元.对外引出了五个引脚:IISDO、IISDI、IISSCLK、IISLRCK和CDCLK.由IIS的协议可知:

IISDO: 用于数字音频信号的输出; IISDI: 用于数字音频信号的输入; IISSCLK: 串行时钟,也叫位时钟BCLK.每一个时钟信号代表一位数字音频信号,因此IISSCLK的频率=声道数×采样频率×采样位数,如采样频率fs为44.1kHz,采样的位数为16位,声道数2个(左、右两个声道),则IISSCLK的频率=32fs=1411.2kHz; IISLRCK: 也称WS.用于切换左右声道的数据.LRCK为“1”表示正在传输的是左声道的数据,为“0”则表示正在传输的是右声道的数据.LRCK的频率等于采样频率; CDCLK: 为该芯片提供系统编解码时钟,主要用于音频的A/D、D/A采样时的采样时钟,一般CDCLK为256fs或384fs.

[注:]采样频率fs对频率的设置至关重要,常用的fs有8kHz、16kHz、22.05kHz、44.1kHz、48kHz、96kHz等

相关文章推荐

- 声音采集播放及IIS接口介绍

- 声音采集播放及IIS接口介绍

- 声音采集播放以及I2S接口

- Android实现直接播放麦克风采集到的声音

- 使用waveOut接口在Windows中播放声音

- 【iOS录音与播放】实现利用音频队列,通过缓存进行对声音的采集与播放

- iOS中声音采集与播放的实现(使用AudioQueue)

- 声音采集播放程序

- 声卡录制:采集声卡播放的声音,并录制成mp3文件!

- 【iOS录音与播放】实现利用音频队列,通过缓存进行对声音的采集与播放

- Android直接播放麦克风采集到的声音

- 【iOS录音与播放】实现利用音频队列,通过缓存进行对声音的采集与播放

- C#播放声音的5种方法介绍

- Android直接播放麦克风采集到的声音

- 使用waveOut接口在Windows中播放声音

- 使用waveOut接口在Windows中播放声音(非常实用,转载)

- AudioToolbox--利用AudioQueue音频队列,通过缓存对声音进行采集与播放

- 阶段小结-声音的采集和播放

- Android使用AudioRecord采集声音时声音播放很快解决方案

- 使用waveOut接口在Windows中播放声音