阅读 ‘External Memory PHY Interface (ALTMEMPHY)’笔记

2017-02-23 15:24

246 查看

阅读 ‘External Memory PHY Interface (ALTMEMPHY)’笔记

1.PLL reference clock frequency

此处控制器输入时钟设置为100MHz,同样在顶层文件的代码中也有体现:

2.Memory clock frequency

此时钟是传给memory device的,根据需要在设备最大频率与最小频率之间的值。

3.关于phy_clk和reset_phy_clk_n这一对信号

控制器发送需要写入memory的数据,和接受从memory读取的数据,地址信号等都需要用时钟(phy_clk)。

4.关于memory burst length的设定

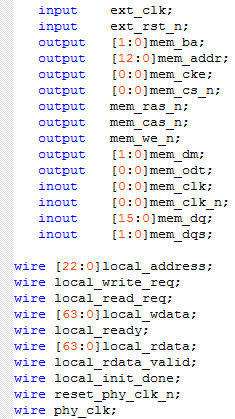

当controller data rate:half,local interface是memory data bus的四倍,如下图中:

Inout [15:0]mem_dq;

wire [63:0]local_wdata;

wire [63:0]local_rdata;

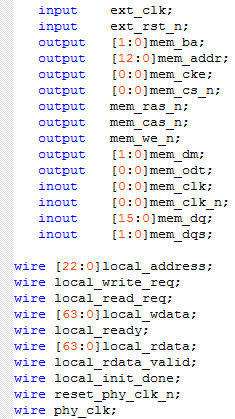

当controller data rate:Full,local interface是memory data bus的2倍,如下图中:

inout [15:0]mem_dq;

input [31:0]local_wdata;

output [31:0]local_rdata;

1.PLL reference clock frequency

此处控制器输入时钟设置为100MHz,同样在顶层文件的代码中也有体现:

2.Memory clock frequency

此时钟是传给memory device的,根据需要在设备最大频率与最小频率之间的值。

3.关于phy_clk和reset_phy_clk_n这一对信号

控制器发送需要写入memory的数据,和接受从memory读取的数据,地址信号等都需要用时钟(phy_clk)。

4.关于memory burst length的设定

当controller data rate:half,local interface是memory data bus的四倍,如下图中:

Inout [15:0]mem_dq;

wire [63:0]local_wdata;

wire [63:0]local_rdata;

当controller data rate:Full,local interface是memory data bus的2倍,如下图中:

inout [15:0]mem_dq;

input [31:0]local_wdata;

output [31:0]local_rdata;

相关文章推荐

- Spark源码阅读笔记之MemoryStore

- Readactor: Practical Code Randomization Resilient to Memory Disclosure阅读笔记(一)

- Hybrid computing using a neural network with dynamic external memory(可微神经计算机)阅读

- Ask Me Anything: Dynamic Memory Networks for Natural Language Processing 阅读笔记及tensorflow实现

- xilinx 网站应用笔记 12 _Memory Interface and Storage Element

- Readactor: Practical Code Randomization Resilient to Memory Disclosure阅读笔记(二)

- Attention and Memory in Deep Learning and NLP(深度学习和NLP中的注意和记忆机制) 阅读笔记

- User Interface Design Tips - [Android官方设计指南阅读笔记]

- 论文笔记之:Hybrid computing using a neural network with dynamic external memory

- 阅读ARM Memory(L1/L2/MMU)笔记

- 【笔记】DE2 硬件和处理器范例-2 External SRAM interface (DE2)(digital logic)(verilog hdl)

- 大道至简阅读笔记之三

- 程序开发心理学阅读笔记之一

- 蓝牙Host Controller Interface笔记

- 论文阅读,GAN 生成对抗网络 2014 Goodfellow原文阅读笔记

- Hadoop 2.2.0 Job源代码阅读笔记

- <<JavaScript编程全解>>阅读笔记之javascript基础

- caffe代码阅读:SyncedMemory和Blob

- Neural Machine Translation论文阅读笔记

- 文献阅读笔记——Non-Associative Higher-Order Markov Networks for Point Cloud Classification