异步 FIFO 控制器 (Asynchronous FIFO Controller)

2017-02-04 11:28

309 查看

异步 FIFO 控制器 (Asynchronous FIFO Controller)

但学习和理解 FIFO 设计方法,对于理解跨时钟域异步信号的处理方法很有帮助。

项目地址:Laotzu

参数化数据宽度和 FIFO 深度

增强的同步数据有效指示

增强的首数据预读加速功能(可关闭)

FWFT = 0 的情况

FWFT = 1 的情况

注:

在某些设计中,“首数据自动预读”的功能可能引起错误,可以使 FWFTEN = 0 关掉这个功能。

如果 FIFO 读侧确实需要空信号或者需要进行门限控制设计,请使用 r_counter[] 替代。

注:

一般 Dual-port RAM 的时序是在 r_ram_en 和 r_ram_addr[] 有效的下一个时钟周期输出读数据。

[2] Clifford E. Cummings and Peter Alfke, “Simulation and Synthesis Techniques for Asynchronous FIFO Design with Asynchronous Pointer Comparisons,” SNUG 2002 (Synopsys Users Group Conference, San Jose, CA, 2002) User Papers, March 2002, Section TB2, 3rd paper. Also available at www.sunburst-design.com/papers

Introduction

FIFO 是设计中常用的器件,用于跨时钟域的数据传送。一般从厂家库中直接调用即可,是不需要自己设计的。但学习和理解 FIFO 设计方法,对于理解跨时钟域异步信号的处理方法很有帮助。

项目地址:Laotzu

Feature

经典 FIFO 设计方法(见参考文档)参数化数据宽度和 FIFO 深度

增强的同步数据有效指示

增强的首数据预读加速功能(可关闭)

Application

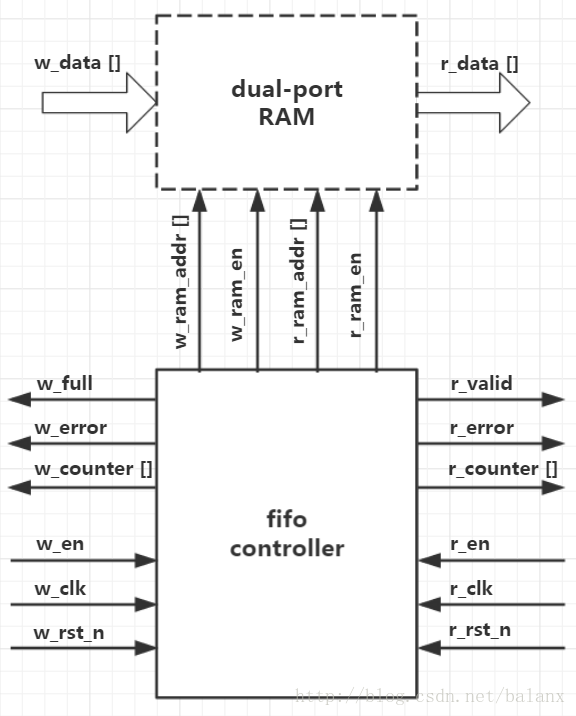

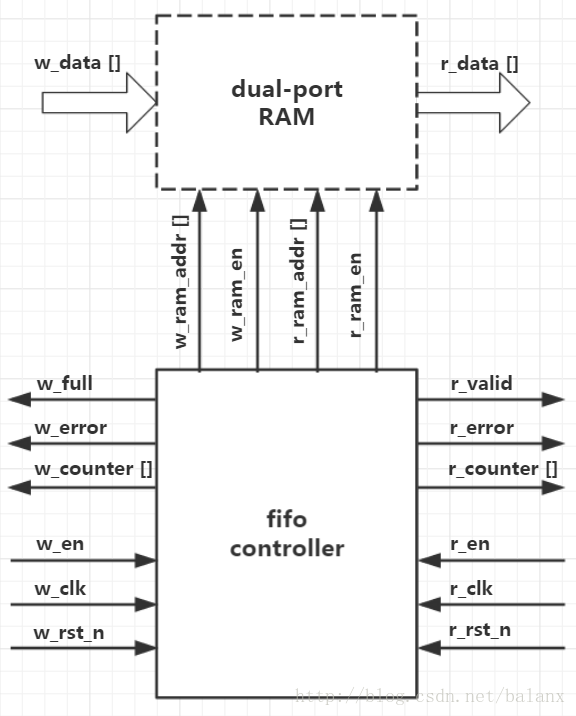

Input/Output

| Name | I/O | Description |

|---|---|---|

| w_rst_n | I | Reset in write-side 1 is normal 0 is reset |

| w_clk | I | Clock in write-side |

| w_en | I | Write enable 1 is write 0 is NOP |

| w_full | O | 1 is FIFO full |

| w_error | O | Error in write-side 1 is error 0 is normal |

| w_counter [] | O | FIFO counter in write-side |

| r_rst_n | I | Reset in read-side 1 is normal 0 is reset |

| r_clk | I | Clock in read-side |

| r_en | I | Read enable 1 is read 0 is NOP |

| r_valid | O | 1 is data valid in read-side |

| r_error | O | Error in read-side 1 is error 0 is normal |

| r_counter [] | O | FIFO counter in read-side |

| w_ram_addr [] | O | Write address for dual-port RAM |

| w_ram_en | O | Write enable for dual-port RAM 1 is enable 0 is disable |

| r_ram_addr [] | O | Read address for dual-port RAM |

| r_ram_en | O | Read enable for dual-port RAM 1 is enable 0 is disable |

Parameter

| Name | Description |

|---|---|

| FWFTEN | First word pre-read enable 1 is enable 0 is disable |

| ADDRWIDTH | Address bus width |

| FIFODEPTH | FIFO depth |

首数据预读加速

比较下面两种情况下的时序,在 FWFTEN = 1 的情况,FIFO 从空到有数据的时候不用等到 r_en 有效,其第一个数据 (D0) 就被自动读出。相对于 FWFTEN = 0 的情况,r_valid 指示信号提前了,这样可以加快 FIFO 的吞吐率。FWFT = 0 的情况

FWFT = 1 的情况

注:

在某些设计中,“首数据自动预读”的功能可能引起错误,可以使 FWFTEN = 0 关掉这个功能。

同步数据有效指示

和传统 FIFO 控制器使用空信号 (EMPTY) 指示读数据有效不同,此控制器采用 r_valid 信号同步指示 FIFO 读数据有效,这样可以给 FIFO 应用带来一点方便。如果 FIFO 读侧确实需要空信号或者需要进行门限控制设计,请使用 r_counter[] 替代。

注:

一般 Dual-port RAM 的时序是在 r_ram_en 和 r_ram_addr[] 有效的下一个时钟周期输出读数据。

References

[1] Clifford E. Cummings, “Simulation and Synthesis Techniques for Asynchronous FIFO Design”, SNUG 2002 (Synopsys Users Group Conference, San Jose, CA, 2002). Also available at www.sunburst-design.com/papers[2] Clifford E. Cummings and Peter Alfke, “Simulation and Synthesis Techniques for Asynchronous FIFO Design with Asynchronous Pointer Comparisons,” SNUG 2002 (Synopsys Users Group Conference, San Jose, CA, 2002) User Papers, March 2002, Section TB2, 3rd paper. Also available at www.sunburst-design.com/papers

相关文章推荐

- ruby实现的一个异步文件下载HttpServer实例

- C#异步绑定数据实现方法

- 科学知识:同步、异步、阻塞和非阻塞区别

- 探讨Ajax中同步与异步之间的区别

- C#中异步回调函数用法实例

- jQuery Ajax 异步加载显示等待效果代码分享

- 使用AJAX完成用户名是否存在异步校验

- C#实现异步GET的方法

- C#异步下载文件

- C#异步执行任务的方法

- 简单实现C#异步操作

- 浅谈socket同步和异步、阻塞和非阻塞、I/O模型

- 使用Promise解决多层异步调用的简单学习心得

- 深入理解JavaScript编程中的同步与异步机制

- Ajax 异步加载解析

- 详解ASP.NET MVC下的异步Action的定义和执行原理

- Jquery异步提交表单代码分享

- javascript-解决mongoose数据查询的异步操作

- JQuery异步获取返回值中文乱码的解决方法

- 解析ajaxFileUpload 异步上传文件简单使用