Verilog模块的设计流程

2016-09-13 09:50

169 查看

September 13, 2016

作者:dengshuai_super

出处:http://blog.csdn.net/dengshuai_super/article/details/52523224

声明:转载请注明作者及出处。

2.有哪些端口(输入输出端口)

3.端口之间的逻辑时序关系

只要是电路一定有输入输出。

把我们需要测试的模型放到Testbench内部去。为这段模型加载激励信号,然后观测他的输出和内部信号。

出了问题直接修改代码。

这里的内置逻辑分析仪是Signal Tap II。

时序过了,还可能出现的问题是:

信号完整性,电池兼容的问题。

这种问题容易在高频的情况下发生。

内置的逻辑分析仪就是一个核一段代码,如果空间资源剩余足够就把这段加载运行,从内部信号里抽取,从Jtag口反映到屏幕。

好处:避免真实仪器测试线发生延迟。

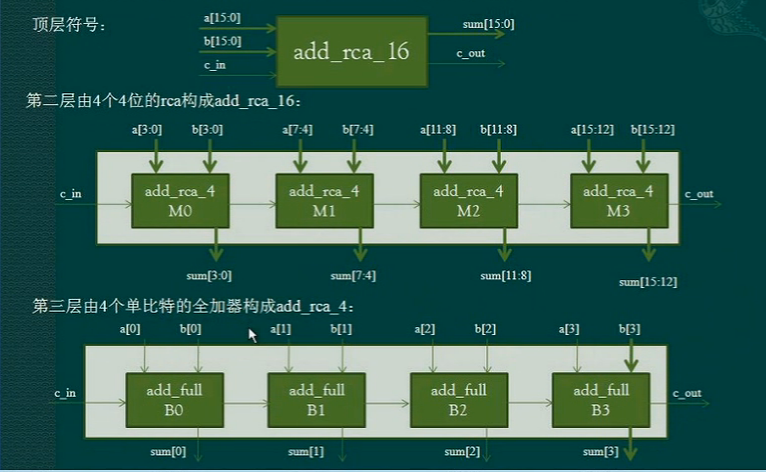

例二:设计一个十六位的行波进位加法器,要求按照层次化原则进行设计和验证。

来源:

https://ke.qq.com/user/tasks/index.html?cid=117307#tid=100127911&fr=2

作者:dengshuai_super

出处:http://blog.csdn.net/dengshuai_super/article/details/52523224

声明:转载请注明作者及出处。

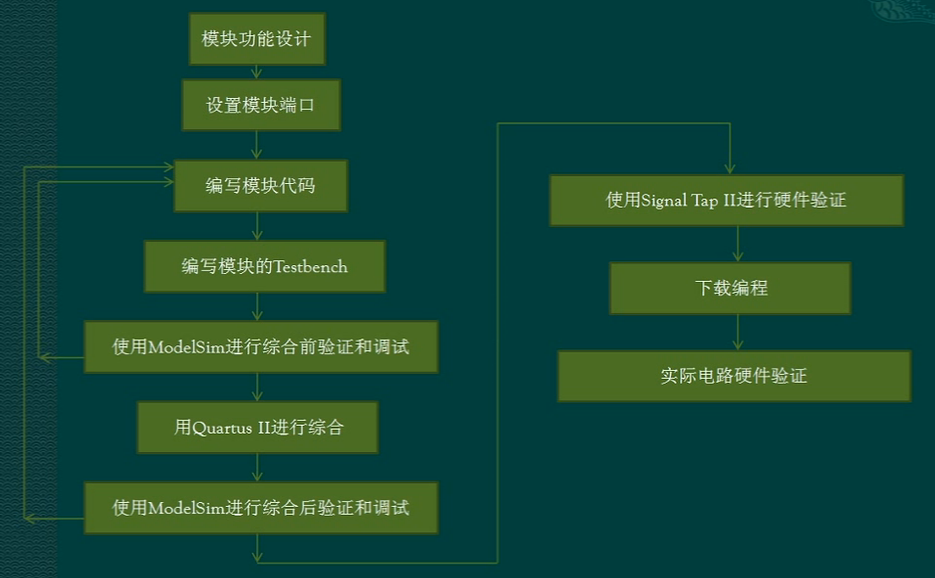

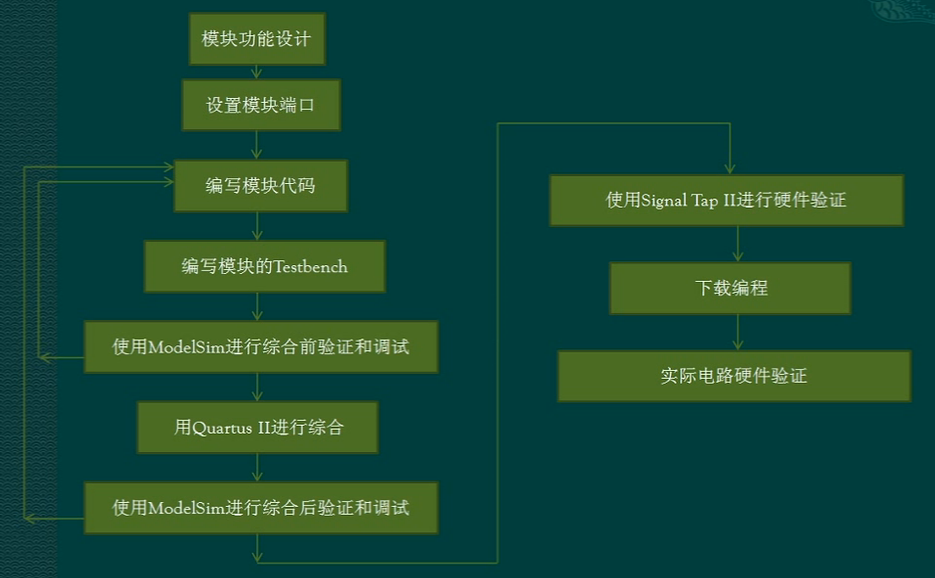

一、功能设计(序曲:三步曲:功能设计)

1.做什么2.有哪些端口(输入输出端口)

3.端口之间的逻辑时序关系

二、编写代码

编码的过程就是描述的过程,描述的过程就成为建模modeling,完成编码之后就形成了一个抽象电路模块。这段代码对应一个抽象电路。(这个电路通过某种方式可以变成实际的物理电路)只要是电路一定有输入输出。

三、编写Testbench

在得到实际电路之前进行早期验证,写一个测试平台Testbench,它也是抽象的,需要用代码描述,激励信号也是用代码描述的。把我们需要测试的模型放到Testbench内部去。为这段模型加载激励信号,然后观测他的输出和内部信号。

四、前仿

运行Testbench段抽象模型的方式就叫做仿真。验证的模型是我们自己编写的模型,验证的内容主要是端口之间的逻辑功能是否符合是否和我们的设计吻合。(功能仿真,RTL的仿真)出了问题直接修改代码。

五、综合

用Quartus II 综合生成网表。形成了Gate Level的抽象电路模型。六、后仿

验证时序。(加载延迟参数,信号之间的延迟。)七、硬件验证

用内置的逻辑分析仪进行验证。这里的内置逻辑分析仪是Signal Tap II。

时序过了,还可能出现的问题是:

信号完整性,电池兼容的问题。

这种问题容易在高频的情况下发生。

内置的逻辑分析仪就是一个核一段代码,如果空间资源剩余足够就把这段加载运行,从内部信号里抽取,从Jtag口反映到屏幕。

好处:避免真实仪器测试线发生延迟。

八、下载编程并验证

例一:设计一个双输入与门逻辑,编写Testbanch,进行前仿和后仿。module and_gate(a,b,f); input a; input b; output f; assign f = a & b; endmoudle

`timescale 1ns /1ns //分子是时间单位,分母是频率 modu 4000 le and_gate_tb; reg a,b;//register类型 wire f;//线网类型 and_gate u1( .a(a), .b(b), .f(f)); initial begin a=0;b=0; forever begin #20 a = 0;b = 0; #20 a = 0;b = 0; #20 a = 0;b = 0; #20 a = 0;b = 0; end end

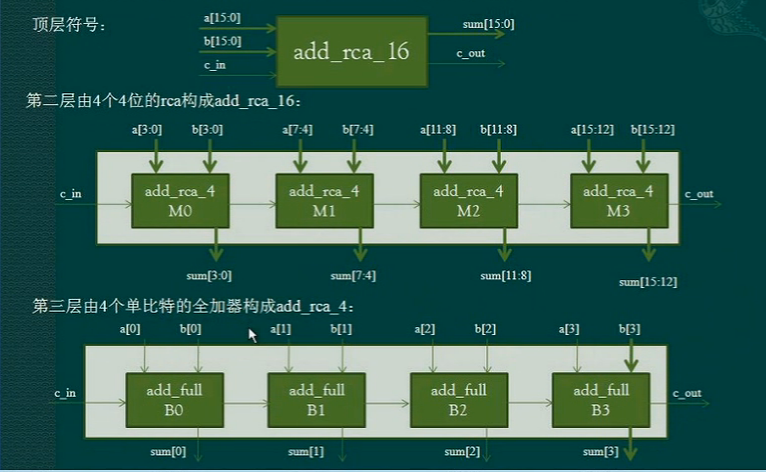

例二:设计一个十六位的行波进位加法器,要求按照层次化原则进行设计和验证。

module add_rca_16(a,b,c_in,sum,c_out); input [15:0] a; input [15:0] b; input c_in; output [15:0] sum; output c_out; wire c_out_m0,c_out_m1,c_out_m2; add_rca_4 m0(.a(a[3:0]),.b(b[3:0]),.c_in(c_in),.sum(sum[3:0]),.c_out(c_out_m0)); add_rca_4 m1(.a(a[7:4]),.b(b[7:4]),.c_in(c_out_m0),.sum(sum[7:4]),.c_out(c_out_m1)); add_rca_4 m2(.a(a[11:8]),.b(b[11:8]),.c_in(c_out_m1),.sum(sum[11:8]),.c_out(c_out_m2)); add_rca_4 m3(.a(a[15:12]),.b(b[15:12]),.c_in(c_out_m2),.sum(sum[15:12]),.c_out(c_out)); endmodule

module add_rca_4(a,b,c_in,sum,c_out); input [3:0] a; input [3:0] b; input c_in; output [3:0] sum; output c_out; wire c_out_b0,c_out_b1,c_out_b2; add_full b0(.a(a[0]),.b(b[0]),.c_in(c_in),.sum(sum[0]),.c_out(c_out_b0)); add_full b1(.a(a[1]),.b(b[1]),.c_in(c_out_b0),.sum(sum[1]),.c_out(c_out_b1)); add_full b2(.a(a[2]),.b(b[2]),.c_in(c_out_b1),.sum(sum[2]),.c_out(c_out_b2)); add_full b3(.a(a[3]),.b(b[3]),.c_in(c_out_b2),.sum(sum[3]),.c_out(c_out)); endmodule

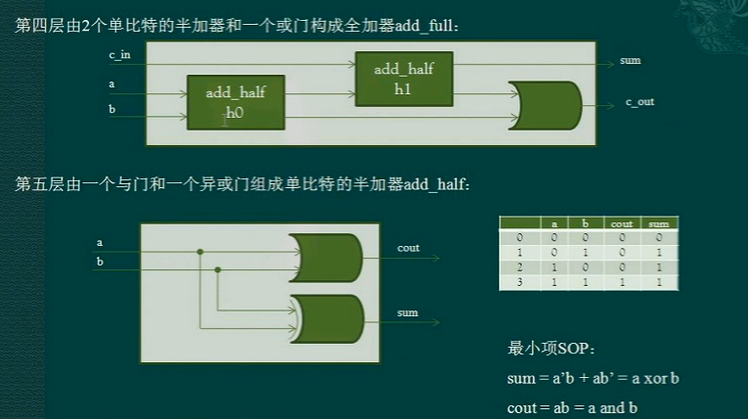

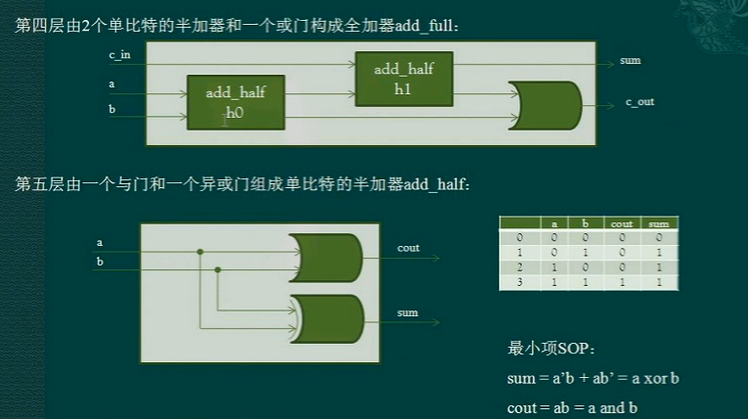

module add_full(a,b,c_in,sum,c_out); input a; input b; input c_in; output sum; output c_out; wire c_out_h0,c_out_h1,sum_h0; add_half h0(.a(a),.b(b),.sum(sum_h0),.c_out(c_out_h0)); add_half h1(.a(c_in),.b(sum_h0),.sum(sum),.c_out(c_out_h1)); or (c_out,c_out_h0,c_out_h1);//第一个参数是输出 endmodule

module add_half(a,b,sum,c_out); input a; input b; output sum; output c_out; xor(sum,a,b); and(c_out,a,b); endmodule

来源:

https://ke.qq.com/user/tasks/index.html?cid=117307#tid=100127911&fr=2

相关文章推荐

- 我脑残实验室Verilog学习笔记——在Xilinx ISE中运用符号设计顶层模块的方法

- 工作流系统-业务流程模块的详细设计

- 【翻译】在Verilog设计中使用参数化模块库(Quartus II)(Verilog)

- 流程填报模块 填报表单设计规范

- FPGA学习(第10节)-模块的例化-Verilog层次化设计实现LED流水灯

- 前端开发零部件管理模块的设计流程

- verilog 层次化设计的简单问题 -- 如何调用底层模块

- VGA控制的verilog模块设计

- verilog 层次化设计的简单问题 -- 如何调用底层模块

- verilog语言RS232串口接收模块设计——串口调试工具发送数据在数码管显示

- verilog语言RS232串口发送模块设计——采集ps2键盘数据在串口调试工具显示

- verilog时钟分频设计(整合模块)

- 通用权限模块设计搞好了,但是又没耐心写出来了

- UI界面设计—界面设计流程

- 拍卖系统模块设计方案

- 变频模块的详细设计

- 以增加收藏夹功能为实例,解析asp.net forums2结构流程及组件设计

- [转]Verilog数字系统设计教程(大连理工一博士学习笔记)

- Shark流程跳转的设计