[verilog读书笔记]5.门级建模

2016-09-12 20:00

295 查看

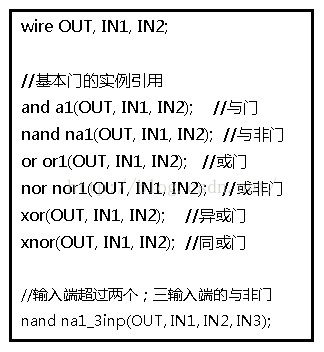

一、门的类型

1.与门(and)和或门(or)

与门和或门都具有一个标量输出端和多个标量输入端。门的端口列表中的第一个端口必定是输出,其后为输入端口。

2.缓冲门/非门

buf/not 门具有一个标量输入和多个标量输出。端口列表最后一个端口为输入端口,其他终端连接至输出端口。

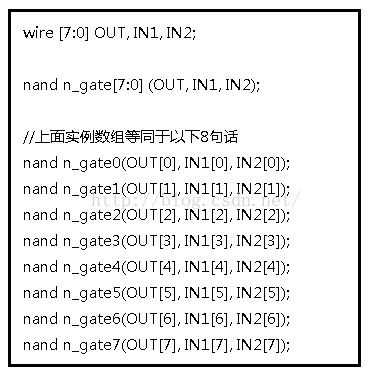

3.实例数组

在许多情况下,我们需要对某种类型的门进行多次调用,这些门实例之间的区别仅仅在于他们分别连接在不同的向量信号位上。这时候可以使用实例数组的方法。

二、门延迟

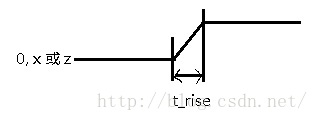

1.上升、下降和关断延迟上升延迟:在门的输入发生变化的情况下,门的输出从0, x, z变化为1所需的时间称为上升延迟

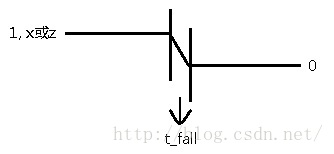

下降延迟:下降延迟是指门的输出从1, x, z变化为0所需的时间

关断延迟:关断延迟是指门的输出从0, 1, x变化为高阻抗z所需的时间。

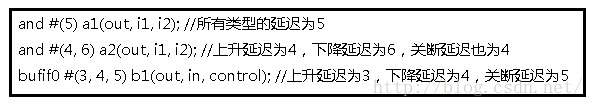

在verilog中,如果我们只指定了一个延迟值,那么对所有类型的延迟都是用这个延迟值;如果我们指定了两个延迟值,则他们分别代表上升延迟和下降延迟,两者中的小者为关断延迟;如果未指定延迟值,那么默认延迟值为0。

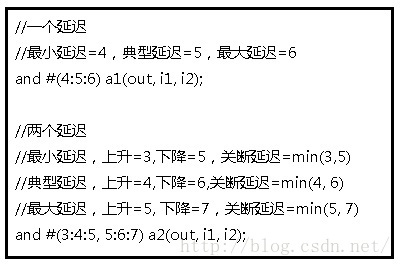

2.最小/典型/最大延迟

除了上升、下降和关断延迟以外,对于每种类型的延迟还可以指定其最小值、最大值和典型值。在建立器件行为模型时要用到延迟的最小值/最大值/典型值,这是因为受到集成电路制造工艺过程的影响,真是的器件延迟总是在最大值和最小值之间的范围内变化。最小值:设计者预期逻辑门所具有的最小延迟

典型值:设计者预期逻辑门所具有的典型延迟

最大值:设计者预期逻辑门所具有的最大延迟

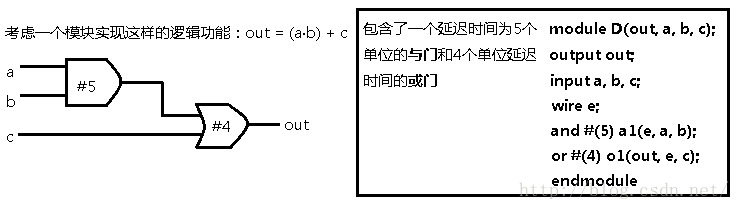

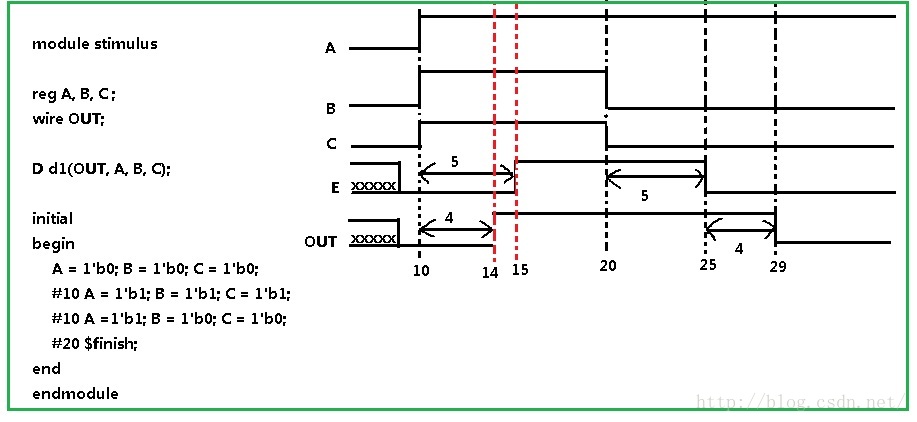

3.一个例子

相关文章推荐

- [bzoj3729]Gty的游戏

- 组原 之 数字

- JavaScript学习笔记之DOM对象操作html元素

- POJ 2065 SETI(高斯消元解同余方程组)

- LeetCode 383:Ransom Note

- 并查集

- 160809132 梁佳佳

- Django踩坑

- Android Volley使用之二:Volley请求网络图片

- sass实战演练06 - 把布局拆分为12列(2):拆分和偏移

- 行内元素和块元素

- MongoDB 的用户认证

- 【JZOJ4771】爬山

- 第9章:面向对象变量与关键字

- Mac 下gdb 的安装过程

- opencv实现多图像读取并显示,sprintf_s函数,static_cast

- stream_context_create() 模拟 POST、GET数据

- HDU 5873 - Football Match【2016大连区域赛网络赛1006】

- Hive在spark2.0.0启动时无法访问../lib/spark-assembly-*.jar: 没有那个文件或目录的解决办法

- javascript网页特效——table