BMT硬件之放大器(一):运算放大器的一些注意点

2016-09-02 19:03

309 查看

运算放大器是作为最通用的模拟器件,广泛用于信号变换调理、ADC采样前端、电源电路等场合中。虽然运放外围电路简单,不过在使用过程中还是有很多需要注意的地方。

本文引用地址:http://www.eepw.com.cn/article/276268.htm

1、注意输入电压是否超限

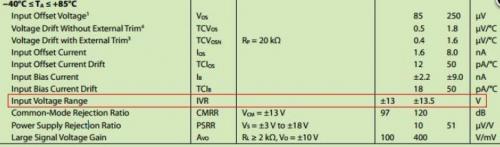

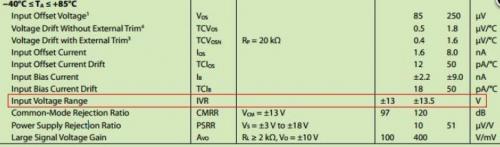

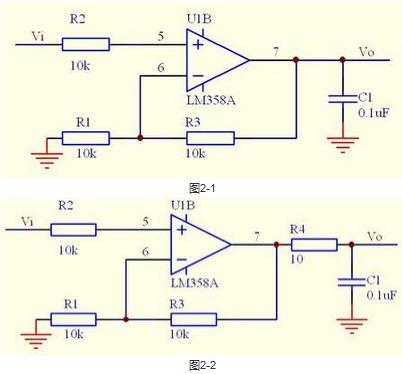

图1是ADI的OP07数据表中的输入电气特性的一部分,可以看到在电源电压±15V的条件下,输入电压的范围是±13.5V,如果输入电压超出范围,那么运放就会工作不正常,出现一些意料不到的情况。

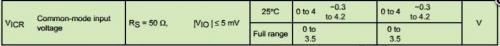

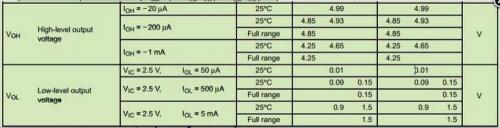

而有一些运放标注的不是输入电压范围,而是共模输入电压范围,如图1-2是TI的TLC2272数据表的一部分,在单电源+5V的条件下,共模输入范围是0-3.5V.其实由于运放正常工作时,同相端和反相端输入电压基本是一致的(虚短虚断),所以“输入电压范围”与“共模输入电压范围”都是一样的意思。

图1-1

图1-2

2、不要在运放输出直接并接电容

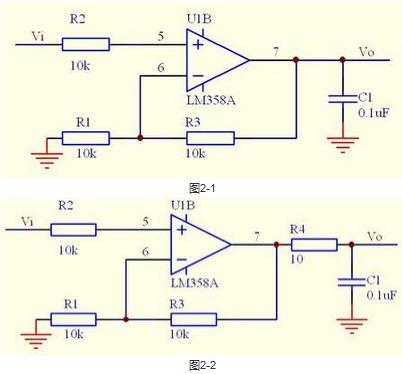

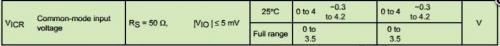

在直流信号放大电路中,有时候为了降低噪声,直接在运放输出并接去耦电容(如图2-1)。虽然放大的是直流信号,但是这样做是很不安全的。当有一个阶跃信号输入或者上电瞬间,运放输出电流会比较大,而且电容会改变环路的相位特性,导致电路自激振荡,这是我们不愿意看到的。

正确的去耦电容应该要组成RC电路,就是在运放的输出端先串入一个电阻,然后再并接去耦电容(如图2-2)。这样做可以大大削减运放输出瞬间电流,也不会影响环路的相位特性,可以避免振荡。

3、不要在放大电路反馈回路并接电容

如图3-1所示,同样是一个用于直流信号放大的电路,为了去耦,不小心把电容并接到了反馈回路,反馈信号的相位发生了改变,很容易就会发生振荡。所以,在放大电路中,反馈回路不能加入任何影响信号相位的电路。由此延伸至稳压电源电路,如图3-2,并接在反馈脚的C3是错误的。为了降低纹波,可以把C3与R1并联,适当增大纹波的负反馈作用,抑制输出纹波。

4、注意运放的输出摆幅

本文引用地址:http://www.eepw.com.cn/article/276268.htm

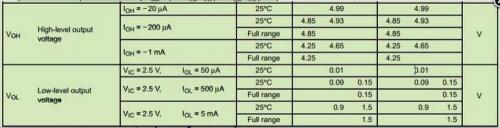

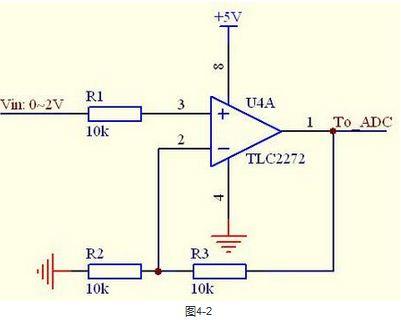

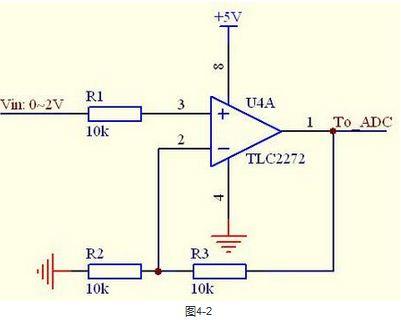

任何运放都不可能是理想运放,输出电压都不可能达到电源电压,一般基于MOS的运放都是轨对轨运放,在空载情况下输出可以达到电源电压,但是输出都会带一定的负载,负载越大,输出降落越多。基于三极管的运放输出幅度的相对值更小,有的运放输出幅度比电源电压要小2~6V,比如NE5532.图4-1就是TI的TLC2272在+5V供电的输出特性,它属于轨对轨运放,如果用该器件作为ADC采样的前级放大(如图4-2),单电源+5V供电,那么当输入接近0V的时候,输入和输出变得非线性的了。解决的方法是引入负电源,比如在4脚加入-1V的负电源,这样在整个输入范围内,输出与输入都是线性的了。

图4-1

5、注意反馈回路的Layout

反馈回路的元器件必须要靠近运放,而且PCB走线要尽量短,同时要尽量避开数字信号、晶振等干扰源。反馈回路的布局布线不合理,则会容易引入噪声,严重会导致自激振荡。

6、要重视电源滤波

运放的电源滤波不容忽视,电源的好坏直接影响输出。特别是对于高速运放,电源纹波对运放输出干扰很大,弄不好就会变成自激振荡。所以最好的运放滤波是在运放的电源脚旁边加一个0.1uF的去耦电容和一个几十uF的钽电容,或者再串接一个小电感或者磁珠,效果会更好。

[align=left]

[/align]

本文引用地址:http://www.eepw.com.cn/article/276268.htm

1、注意输入电压是否超限

图1是ADI的OP07数据表中的输入电气特性的一部分,可以看到在电源电压±15V的条件下,输入电压的范围是±13.5V,如果输入电压超出范围,那么运放就会工作不正常,出现一些意料不到的情况。

而有一些运放标注的不是输入电压范围,而是共模输入电压范围,如图1-2是TI的TLC2272数据表的一部分,在单电源+5V的条件下,共模输入范围是0-3.5V.其实由于运放正常工作时,同相端和反相端输入电压基本是一致的(虚短虚断),所以“输入电压范围”与“共模输入电压范围”都是一样的意思。

图1-1

图1-2

2、不要在运放输出直接并接电容

在直流信号放大电路中,有时候为了降低噪声,直接在运放输出并接去耦电容(如图2-1)。虽然放大的是直流信号,但是这样做是很不安全的。当有一个阶跃信号输入或者上电瞬间,运放输出电流会比较大,而且电容会改变环路的相位特性,导致电路自激振荡,这是我们不愿意看到的。

正确的去耦电容应该要组成RC电路,就是在运放的输出端先串入一个电阻,然后再并接去耦电容(如图2-2)。这样做可以大大削减运放输出瞬间电流,也不会影响环路的相位特性,可以避免振荡。

3、不要在放大电路反馈回路并接电容

如图3-1所示,同样是一个用于直流信号放大的电路,为了去耦,不小心把电容并接到了反馈回路,反馈信号的相位发生了改变,很容易就会发生振荡。所以,在放大电路中,反馈回路不能加入任何影响信号相位的电路。由此延伸至稳压电源电路,如图3-2,并接在反馈脚的C3是错误的。为了降低纹波,可以把C3与R1并联,适当增大纹波的负反馈作用,抑制输出纹波。

4、注意运放的输出摆幅

本文引用地址:http://www.eepw.com.cn/article/276268.htm

任何运放都不可能是理想运放,输出电压都不可能达到电源电压,一般基于MOS的运放都是轨对轨运放,在空载情况下输出可以达到电源电压,但是输出都会带一定的负载,负载越大,输出降落越多。基于三极管的运放输出幅度的相对值更小,有的运放输出幅度比电源电压要小2~6V,比如NE5532.图4-1就是TI的TLC2272在+5V供电的输出特性,它属于轨对轨运放,如果用该器件作为ADC采样的前级放大(如图4-2),单电源+5V供电,那么当输入接近0V的时候,输入和输出变得非线性的了。解决的方法是引入负电源,比如在4脚加入-1V的负电源,这样在整个输入范围内,输出与输入都是线性的了。

图4-1

5、注意反馈回路的Layout

反馈回路的元器件必须要靠近运放,而且PCB走线要尽量短,同时要尽量避开数字信号、晶振等干扰源。反馈回路的布局布线不合理,则会容易引入噪声,严重会导致自激振荡。

6、要重视电源滤波

运放的电源滤波不容忽视,电源的好坏直接影响输出。特别是对于高速运放,电源纹波对运放输出干扰很大,弄不好就会变成自激振荡。所以最好的运放滤波是在运放的电源脚旁边加一个0.1uF的去耦电容和一个几十uF的钽电容,或者再串接一个小电感或者磁珠,效果会更好。

[align=left]

[/align]

相关文章推荐

- java矩阵运算包ujmp中的一些小示例和注意事项

- java矩阵运算包ujmp中的一些小示例和注意事项

- 硬件设计基础:什么是 rail-to-rail运算放大器?

- 硬件设计の运算放大器の一

- 硬件电路设计基础:运算放大器

- (5)java语言基础(注释,关键字,标识符,常变量,类型转换,转义字符、位运算和一些注意的运算)

- 硬件十万个为什么——运放篇(八)运算放大器容性负载驱动问题

- 使用运算放大器需要注意的6个事项

- 大数据基础环境搭建的从spark到hadoop,从底层硬件到上层软件的一些必备注意事项

- DSP硬件设计的一些注意事项

- 运算放大器使用的6个注意事项

- 位运算的一些注意事项

- JAVA学习中应该注意的一些简单问题?

- 编写Windows服务应该注意的一些心得

- 漂亮MM拍照时需要注意的一些问题(火力增强版)

- 管理Oracle数据库要注意的一些问题

- C++程序员在学习C#时需要注意的一些问题(一)

- 编程中的一些注意事项

- 打包可执行jar文件的一些注意事项

- 在用ORACLE数据库和JSP连接时要注意的一些问题精粹