Verilog HDL那些事_建模篇笔记(实验八:键盘解码)

2016-08-16 14:43

309 查看

1.PS2接口与协议时序图

对于PS2的接口来说,需要额外关注的是PIN5与PIN1,一个是时钟,一个是数据。PS2协议对数据的移位是“CLOCK下降沿”有效,其CLOCK的频率通常在10KHz左右。每当CLOCK的下降沿到来时,发送一位数据。

协议时序图

传输数据定义表

要想获得键盘的数据,我们只需要关注(1~8)数据位,其余的位可以忽略,但程序中要给出相应的处理。

2.电平检测模块

下面对PS2解码过程建模,本模型有两个输入,PS2的时钟信号输入与PS2的数据输入。其中电平检测模块用于检测PS2的“下降沿”,当下降沿到来时,使能PS2解码模块,解码模块对输入的每一帧数据进行解码,最后将解码后的数据输出,并产生一个解码完成信号。

以上为检测下降沿到来的always块语句。对于电平检测模块的编写一般遵循以下技巧:设定两个reg型变量,一个用来接收新的时钟周期传进来的电平信号,另外一个用来存储上一个时钟周期的电平信号。即:

H2L_F1 <= PS2_CLK_Pin_In;

H2L_F2 <= H2L_F1;

其中需要说明的是,以上两个语句采用的是非阻塞式赋值,非阻塞式赋值语句是在整个模块结束之际才完成赋值操作。

位于begin/end块内的多条非阻塞式赋值语句是并行执行的,这些非阻塞赋值语句都会在其中任何一条语句执行完成之前开始执行。这是硬件电路的特点,因为实际的逻辑门电路都是独立工作的,而不是等到其他门电路运转结束之后自己才开始运转。

因此,第一条赋值语句并不会立刻改变H2L_F1的值。而是H2L_F1与H2L_F2的值是同时刷新的。

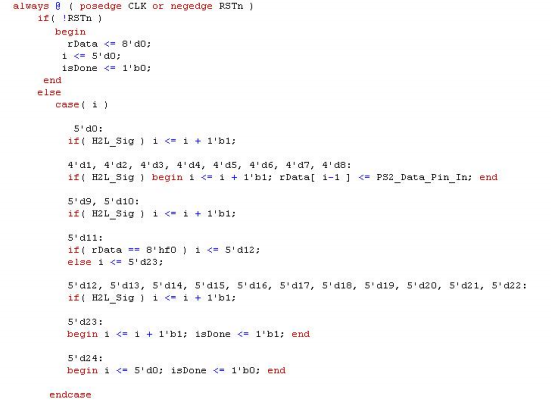

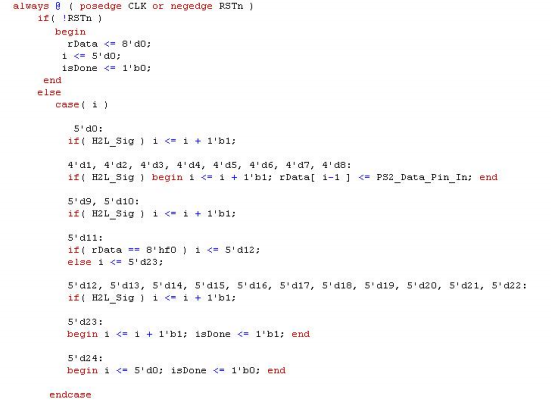

3.解码模块

解码模块的输入为键盘码数据与解码使能信号,输出为解码后的数据与解码完成信号。

键盘码的数据是一位一位传给解码模块的,即PS2的时钟由高电平跳变到低电平时,传入键盘码的一位数据。always块语句中的i是一个状态标志位,用来控制状态变化后的相应操作。

4’d1,4’d2,4’d3......:

If(H2L_Sig) begin i <= i + 1’b1; rData[i-1] <= PS2_Data_Pin_In; end

当PS2时钟信号由高变低,需要作出的处理有:将系统转移到下一个状态,接收当前传来的数据。

注意:本实验有两个时钟,一个是系统时钟,带动整个系统运行。一个是PS2的时钟,用来接收键盘传过来的数据。

对于PS2的接口来说,需要额外关注的是PIN5与PIN1,一个是时钟,一个是数据。PS2协议对数据的移位是“CLOCK下降沿”有效,其CLOCK的频率通常在10KHz左右。每当CLOCK的下降沿到来时,发送一位数据。

协议时序图

传输数据定义表

| 第N位 | 属性 |

| 0 | 开始位 |

| 1~8 | 数据位 |

| 9 | 校验位 |

| 10 | 结束位 |

2.电平检测模块

下面对PS2解码过程建模,本模型有两个输入,PS2的时钟信号输入与PS2的数据输入。其中电平检测模块用于检测PS2的“下降沿”,当下降沿到来时,使能PS2解码模块,解码模块对输入的每一帧数据进行解码,最后将解码后的数据输出,并产生一个解码完成信号。

以上为检测下降沿到来的always块语句。对于电平检测模块的编写一般遵循以下技巧:设定两个reg型变量,一个用来接收新的时钟周期传进来的电平信号,另外一个用来存储上一个时钟周期的电平信号。即:

H2L_F1 <= PS2_CLK_Pin_In;

H2L_F2 <= H2L_F1;

其中需要说明的是,以上两个语句采用的是非阻塞式赋值,非阻塞式赋值语句是在整个模块结束之际才完成赋值操作。

位于begin/end块内的多条非阻塞式赋值语句是并行执行的,这些非阻塞赋值语句都会在其中任何一条语句执行完成之前开始执行。这是硬件电路的特点,因为实际的逻辑门电路都是独立工作的,而不是等到其他门电路运转结束之后自己才开始运转。

因此,第一条赋值语句并不会立刻改变H2L_F1的值。而是H2L_F1与H2L_F2的值是同时刷新的。

3.解码模块

解码模块的输入为键盘码数据与解码使能信号,输出为解码后的数据与解码完成信号。

键盘码的数据是一位一位传给解码模块的,即PS2的时钟由高电平跳变到低电平时,传入键盘码的一位数据。always块语句中的i是一个状态标志位,用来控制状态变化后的相应操作。

4’d1,4’d2,4’d3......:

If(H2L_Sig) begin i <= i + 1’b1; rData[i-1] <= PS2_Data_Pin_In; end

当PS2时钟信号由高变低,需要作出的处理有:将系统转移到下一个状态,接收当前传来的数据。

注意:本实验有两个时钟,一个是系统时钟,带动整个系统运行。一个是PS2的时钟,用来接收键盘传过来的数据。

相关文章推荐

- Verilog HDL那些事_建模篇笔记(实验九:VGA驱动)

- Verilog HDL那些事_建模篇笔记(实验三:按键消抖)

- Verilog HDL那些事_建模篇笔记(实验七:数码管电路驱动)

- Verilog HDL那些事_建模篇笔记(实验一,实验二)

- Verilog 初学笔记--顺序操作 和 并行操作的一点思考(参考黑金教程:Verilog HDL那些事 建模篇)

- Verilog HDL 学习笔记2-blocking and non-blocking assignment

- Verilog HDL 学习笔记3-Latch

- [笔记].串型DAC TLC5620生成锯齿波、三角波实验,Verilog版本

- 【连载】【FPGA黑金开发板】Verilog HDL那些事儿--PS2解码(九)

- 【连载】【FPGA黑金开发板】Verilog HDL那些事儿--PS2解码(九)

- 读书笔记(Verilog HDL那些事儿_建模篇0)

- Verilog HDL 学习笔记1-data type

- [笔记].驱动4x4矩阵键盘的思路.[Verilog]

- ALTERA DE2 之 verilog HDL 学习笔记03 FPGA的PWM输出

- ALTERA DE2 之 verilog HDL 学习笔记04 -altera DE2 上 SRAM的读写

- 【黑金教程笔记之001】veriloghdl 扫盲文—笔记&勘误

- 【原创】DE2实验解答—lab09 (Quartus II)(Verilog HDL)(Digital Logic)

- Verilog HDL语言学习笔记

- 【笔记】再笔记--边干边学Verilog HDL – 009

- ALTERA DE2 之 verilog HDL 学习笔记01 程序的并行