阻塞赋值与非阻塞赋值

2016-07-19 20:57

302 查看

阻塞赋值与非阻塞赋值的区别———摘自《数字系统设计教程》

1.非阻塞(Non_Blocking)赋值(如b<=a)

(1)在语句块中,上面语句所赋的变量值不能立即就为下面的语句所用;

(2)块结束后才能完成这次赋值操作,而所赋的变量值是上一次赋值得到的;

(3)在编写可综合的时序逻辑模块时,这是最常用 的赋值方法。

2.阻塞(blocking)赋值方式(如b=a;)

(1)赋值语句执行完后,块才结束;

(2)b的值在赋值语句执行完后立刻就改变的;

(3)在时序逻辑中使用时,可能会产生意向不到的结果。

举例:1

always @(posedge clk)

begin

b <= a;

c <= b;

end

上述实例中用了非阻塞赋值方式,定义了两个reg型信号b和c。clk信号的上升沿到来时,b就等于a,c就等于b(原始值),这里用到了两个触发器。

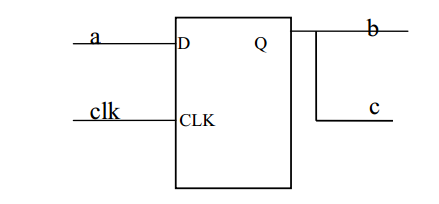

注意:赋值在“always”块结束后执行的,c应为原来b的值。这个always块实际描述的电路功能如图1所示。

例2:

always @(posedge clk)

begin

b = a;

c = b;

end

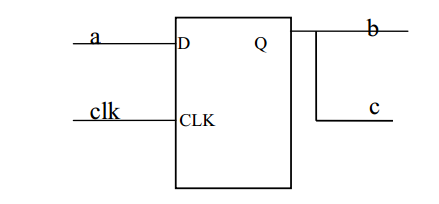

例2采用了阻塞赋值方式。clk信号的上升沿到来时,将发生如下变化:b马上去a的值,c马上取b的值(即等于a),生成如图2所示的电路。图中只用了一个触发器来寄存a的值,又输出给b和c。

1.非阻塞(Non_Blocking)赋值(如b<=a)

(1)在语句块中,上面语句所赋的变量值不能立即就为下面的语句所用;

(2)块结束后才能完成这次赋值操作,而所赋的变量值是上一次赋值得到的;

(3)在编写可综合的时序逻辑模块时,这是最常用 的赋值方法。

2.阻塞(blocking)赋值方式(如b=a;)

(1)赋值语句执行完后,块才结束;

(2)b的值在赋值语句执行完后立刻就改变的;

(3)在时序逻辑中使用时,可能会产生意向不到的结果。

举例:1

always @(posedge clk)

begin

b <= a;

c <= b;

end

上述实例中用了非阻塞赋值方式,定义了两个reg型信号b和c。clk信号的上升沿到来时,b就等于a,c就等于b(原始值),这里用到了两个触发器。

注意:赋值在“always”块结束后执行的,c应为原来b的值。这个always块实际描述的电路功能如图1所示。

例2:

always @(posedge clk)

begin

b = a;

c = b;

end

例2采用了阻塞赋值方式。clk信号的上升沿到来时,将发生如下变化:b马上去a的值,c马上取b的值(即等于a),生成如图2所示的电路。图中只用了一个触发器来寄存a的值,又输出给b和c。

相关文章推荐

- Verilog文件格式范例

- [Verilog]个人.v文件书写规范

- Verilog HDL语言不全面但基本入门够用介绍

- Verilog $Scannf 使用小结

- modelsim仿真波形理解

- 用Modelsim SE 10.1a进行仿真的大致步骤

- Modelsim do脚本文件简单范例

- testbench简单范例

- testbench简单范例

- Modelsim do脚本文件简单范例

- 用Modelsim SE 10.1a进行仿真的大致步骤

- 关于Error: Can't compile duplicate declarations of entity "**" into library "work"的错误

- ISE中将Verilog封装为IPcore

- (筆記) 如何設計邊緣檢測電路? (SOC) (Verilog)

- Verilog笔记

- Verilog 有符号数无符号数混用

- VERILOG实现四位七段数码管显示

- Partitioning for Synthesis

- Veriog_Notes_Chapter 1

- Veriog_Notes_Chapter 2