AHCI vs NVMe

2016-07-02 08:15

316 查看

http://www.hkepc.com/13139

儘管現時有不少高階 SSD 產品改用 PCIe 接口,以突破 SATA 接口的頻寬瓶頸,但控制器設計與 SATA 接口 SSD 一樣,採用老舊的 AHCI 控制器介面,優點是大部份作業系統均已原生支援 AHCI 驅動,相容性高能支援絕多部份作業系統及主機板平台,但 AHCI 控制器介面卻無法完全發揮 PCI Express 介面及 NAND Flash 顆粒的性能優勢。

AHCI 控制器介面 (Advanced Host Controller Interface) 是 PCI 時代非常老舊的技術規範,主要是針對旋轉碟面讀寫的機械式 HDD 而設,例如加入 NCQ (Native Command Queuing) 技術、優化硬碟的資料分佈,將存取順序作最有效率的排序以減少機械臂移動的距離,進而達到省時以及延長硬碟壽命的效果,但當時的設計並非為 SSD 產品而生。

NVMe 控制器介面特別針對 PCI Express 接口及 NAND Flash 特性作出了優化, NVMe 能同時處理最高 6 萬 4 千個 Command Queues 指令列,每個指令列最高可包含 6 萬 4 千個指令,充分發揮 NAND Flash 平行讀寫優勢。 AHCI 控制器介面則只能同時處理 1 個 Command Queues 指令列,每個指令列最高只能包含 32 個指令,令 IOPS 讀寫性能大幅落後 NVMe 。

此外, NVMe 控制器介面支援 PCIe 3.0 技術規範首次引入的 MSI-X 中斷處理 (Interrupts Processing) ,並加入了 Interrupts Steering 中斷導向能力。舊有的 AHCI 控制器僅支援 MSI 中斷處理,裝置僅獲分配 1 個定址並同時只能處理 1 個中斷,在多核心處理器環境下只能讓單顆核心進行存取。

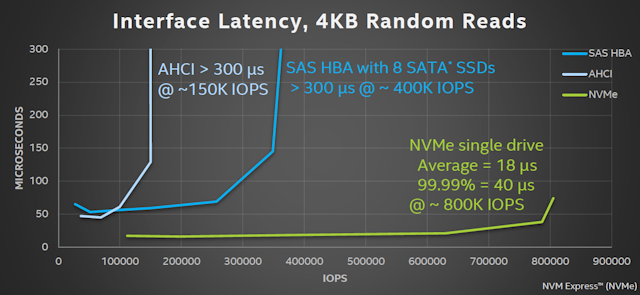

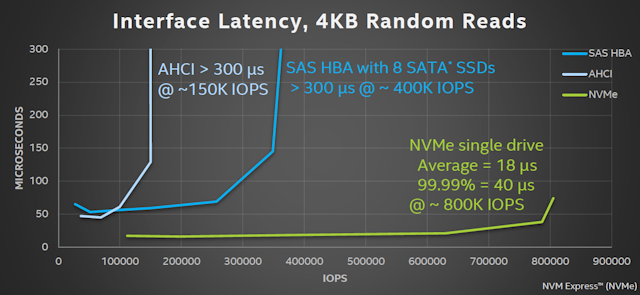

NVMe 控制器則最高可分配多達 2048 個 Interrupts Processing 中斷處理,同時每個中斷均擁有獨立的目標定址,令系統不同處理器核心均能同時存取 SSD 裝置,此一差異令 NVMe 與 AHCI 在 IOPS 及讀寫延遲上存在巨大差距。

當指令所需的資料定址不在寄存器中, AHCI 控制器介面需要額外浪費 6-9 個指令週期才能完成讀取,約浪費 12000 ~ 18,000 個 CPU Cycles ,造成約 2.5 ~ 4μs 的延遲,而 NVMe 控制器介面僅需額外 2 個指令,約浪費 4000 個 CPU Cycles ,令 NVMe 的 SSD 裝置擁有更低延遲,減少對 CPU 資源浪費令運算性能明顯提升。

比較處理大量細碎檔案時, AHCI 與 NVMe 亦存在巨大性能差異, AHCI 控制器介面處理讀寫命令時,命令參數需進行兩次無法並行的系統記憶體存取,而 NVMe 則只需要進行一次 64 Bytes 的系統記憶體存取,令 IOPS 吞吐量大幅提升。此外, AHCI 控制器介面在發出指令時需要進行同步鎖定資料, NVMe 控制器則無需進行同步鎖定資料,將有效提升平行讀寫及多線程運算性能。

就像 IDE 接口一樣, SATA 連接埠與 AHCI 介面已完成歷史任務,為配合未來 NAND Flash 技術發展, NVMe 控制器介面將成為未來儲存介面的主流標準,基於 PCI Express 協定以不同的接口形式普及。

NVMe and AHCI Storage Interface Comparison

Next: 18通道設計、36顆MLC顆粒 Intel SSD 750 400GB U.2版本

儘管現時有不少高階 SSD 產品改用 PCIe 接口,以突破 SATA 接口的頻寬瓶頸,但控制器設計與 SATA 接口 SSD 一樣,採用老舊的 AHCI 控制器介面,優點是大部份作業系統均已原生支援 AHCI 驅動,相容性高能支援絕多部份作業系統及主機板平台,但 AHCI 控制器介面卻無法完全發揮 PCI Express 介面及 NAND Flash 顆粒的性能優勢。

AHCI 控制器介面 (Advanced Host Controller Interface) 是 PCI 時代非常老舊的技術規範,主要是針對旋轉碟面讀寫的機械式 HDD 而設,例如加入 NCQ (Native Command Queuing) 技術、優化硬碟的資料分佈,將存取順序作最有效率的排序以減少機械臂移動的距離,進而達到省時以及延長硬碟壽命的效果,但當時的設計並非為 SSD 產品而生。

NVMe 控制器介面特別針對 PCI Express 接口及 NAND Flash 特性作出了優化, NVMe 能同時處理最高 6 萬 4 千個 Command Queues 指令列,每個指令列最高可包含 6 萬 4 千個指令,充分發揮 NAND Flash 平行讀寫優勢。 AHCI 控制器介面則只能同時處理 1 個 Command Queues 指令列,每個指令列最高只能包含 32 個指令,令 IOPS 讀寫性能大幅落後 NVMe 。

此外, NVMe 控制器介面支援 PCIe 3.0 技術規範首次引入的 MSI-X 中斷處理 (Interrupts Processing) ,並加入了 Interrupts Steering 中斷導向能力。舊有的 AHCI 控制器僅支援 MSI 中斷處理,裝置僅獲分配 1 個定址並同時只能處理 1 個中斷,在多核心處理器環境下只能讓單顆核心進行存取。

NVMe 控制器則最高可分配多達 2048 個 Interrupts Processing 中斷處理,同時每個中斷均擁有獨立的目標定址,令系統不同處理器核心均能同時存取 SSD 裝置,此一差異令 NVMe 與 AHCI 在 IOPS 及讀寫延遲上存在巨大差距。

當指令所需的資料定址不在寄存器中, AHCI 控制器介面需要額外浪費 6-9 個指令週期才能完成讀取,約浪費 12000 ~ 18,000 個 CPU Cycles ,造成約 2.5 ~ 4μs 的延遲,而 NVMe 控制器介面僅需額外 2 個指令,約浪費 4000 個 CPU Cycles ,令 NVMe 的 SSD 裝置擁有更低延遲,減少對 CPU 資源浪費令運算性能明顯提升。

比較處理大量細碎檔案時, AHCI 與 NVMe 亦存在巨大性能差異, AHCI 控制器介面處理讀寫命令時,命令參數需進行兩次無法並行的系統記憶體存取,而 NVMe 則只需要進行一次 64 Bytes 的系統記憶體存取,令 IOPS 吞吐量大幅提升。此外, AHCI 控制器介面在發出指令時需要進行同步鎖定資料, NVMe 控制器則無需進行同步鎖定資料,將有效提升平行讀寫及多線程運算性能。

就像 IDE 接口一樣, SATA 連接埠與 AHCI 介面已完成歷史任務,為配合未來 NAND Flash 技術發展, NVMe 控制器介面將成為未來儲存介面的主流標準,基於 PCI Express 協定以不同的接口形式普及。

NVMe and AHCI Storage Interface Comparison

| AHCI | NVMe | |

| Maximum Queue Depth | 1 Command Queue 32 commands per Q | 64K Queues 64K Commands per Q |

| Un-cacheable register accesses | 12,000-18,000 CPU Cycles wasted | ~ 4,000 CPU Cycles wasted |

| MSI-X and Interrupt | Single Interrupt no Steering | 2048 Interrupt with Steering support |

| Parallelism & Multiple Threads | Requires Synchronization lock to issue command | No Locking required |

| Efficiency for 4KB Commands | Command parameter require two serialized host DRAM fetches | Command parameters in one 64 Bytes Fetch |

相关文章推荐

- Android Studio Instant Run注意事项

- gulp的常用api

- 实现配置文件备份的小脚本

- Expression Add Operators

- Asp.Net MVC 扩展 Html.ImageFor 方法详解

- Android常见面试题(一)

- Java中的内部接口

- Microsoft product line summarize

- 计算机学习路径

- Android自动连接指定的wifi,免密码或指定密码

- 设置元素竖向居中的三种方式

- 上古神器vim插件:你真的学会用NERDTree了吗?

- 通过View获取Controller

- 高并发性能调试经验分享

- 一步步带你,如何网站架构

- NVMe 图解

- 手机页面需要添加的标签

- 绝杀!Debug 大法,让运维不再尴尬

- 001——于2017-12-27 1659修订

- python下划线