verilog中always块延时总结

2016-06-15 16:42

344 查看

在上一篇博文中 verilog中连续性赋值中的延时中对assign的延时做了讨论,现在对always块中的延时做一个讨论。

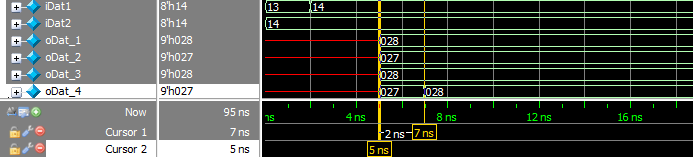

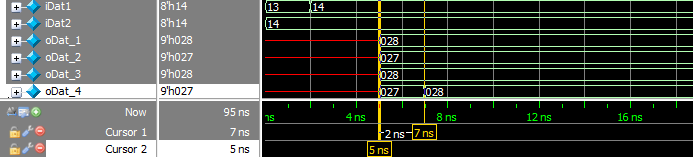

观测下面的程序,@0时刻,输入的数据分别是0x13,0x14 。

@2时刻,输入数据分别是0x14,,0x14 。

四个输出应该是什么样子呢?

直接上图吧

作为阻塞性赋值语句,延时放在前面,就是先延时,再取值赋值。所以oData_1延时之后取了新值。

延时放在后面,就是先取值,再延时赋值。oData_2 是先取了旧值,再延时赋值,中间如果等号右边有变化,被阻塞了。所以oData_2是旧值 。

作为非阻塞性赋值语句,延时放在前面,就是先延时,再取值赋值。所以oData_3延时之后取了新值。

延时放在后面,就是先取值,再延时赋值。oData_4 是先取了旧值,再延时赋值,中间如果等号右边有变化,没有被阻塞,新建event,所以oData_2是旧值之后再更新为新值 。

所以,这以后写TB的时候要慎重啊。

欢迎加入: FPGA广东交流群:162664354

FPGA开发者联盟: 485678884

观测下面的程序,@0时刻,输入的数据分别是0x13,0x14 。

@2时刻,输入数据分别是0x14,,0x14 。

四个输出应该是什么样子呢?

always @ (iDat1 or iDat2) #5 oDat_1 = iDat1 + iDat2; always @ (iDat1 or iDat2) oDat_2 = #5 iDat1 + iDat2; always @ (iDat1 or iDat2) #5 oDat_3 <= iDat1 + iDat2; always @(iDat1 or iDat2) oDat_4 <= #5 iDat1 + iDat2;

直接上图吧

作为阻塞性赋值语句,延时放在前面,就是先延时,再取值赋值。所以oData_1延时之后取了新值。

延时放在后面,就是先取值,再延时赋值。oData_2 是先取了旧值,再延时赋值,中间如果等号右边有变化,被阻塞了。所以oData_2是旧值 。

always @ (iDat1 or iDat2) #5 oDat_1 = iDat1 + iDat2; always @ (iDat1 or iDat2) oDat_2 = #5 iDat1 + iDat2;

作为非阻塞性赋值语句,延时放在前面,就是先延时,再取值赋值。所以oData_3延时之后取了新值。

延时放在后面,就是先取值,再延时赋值。oData_4 是先取了旧值,再延时赋值,中间如果等号右边有变化,没有被阻塞,新建event,所以oData_2是旧值之后再更新为新值 。

always @ (iDat1 or iDat2) #5 oDat_3 <= iDat1 + iDat2; always @(iDat1 or iDat2) oDat_4 <= #5 iDat1 + iDat2;

所以,这以后写TB的时候要慎重啊。

欢迎加入: FPGA广东交流群:162664354

FPGA开发者联盟: 485678884

相关文章推荐

- count-numbers-with-unique-digits

- Precision and Recall

- scanf和cin的区别

- MAC平台下Xcode配置使用OpenCV的具体方法 (2016最新)

- css盒子模型

- 聚合索引和非聚合索引简单介绍

- 图片内存复制性能对比

- 什么是浮动IP

- SqlServer调用CLR服务

- 上田雅美是个 4000 汉子,心然的那首神曲竟然出自reset

- JSON简介

- 图片上传出现的问题

- java nio中buffer缓冲区一些方法

- ZBrush中的皮肤纹理是怎么雕刻出来的

- spring框架的项目报错:No mapping found for HTTP request with URI [ ] in DispatcherServlet with name 'spring'

- 获取String中的所有数字并转化为int类型

- JavaScript专题(二):深入理解iframe

- python lib error

- Spring Boot 打开jsp页面 乱码解决方法

- 进程的关系