汇编语言简介(一)

2016-06-13 00:00

267 查看

摘要: 通过《汇编语言程序设计》第一到三章学习

词汇和指令码功能等同对待(比如:push,mov,sub和call等)。

汇编语言中定义变量包括两个部分:

1)指向一个内存位置的标记

2)内存字节的数据类型和默认值

数据类型决定为变量保存多少字节。如下:

testvalue:

.long 150

message:

.ascii "This is a test message"

pi:

.float 3.14159

第二种方法是使用的堆栈,特别是函数调用

不同之处。

最重要的命令之一是.section命令。这个命令定义内存段、汇编语言程序在其中定义元素。

图1-1

控制总线用于保持处理器和各个系统元素之间功能的同步。数据总线用于在处理器和外部

系统元素之间传送数据。处理器要把读取的内存地址放在地址总线上,然后内存存储单元作出

响应,把这个内存位置存储的值放到数据总线上以便处理器进行访问。

&n

3ff8

bsp; 处理器的主要组件如下:

控制单元

执行单元

寄存器

标志

图1-2显示了这些组件以及它们如何在处理器内进行交互。

图1-2

时,必须从内存获得指令并且加载它们以便处理器进行处理。控制单元的工作是实现4个基本功

能:

1)从内存获得指令

2)对指令进行解码以便进行操作

3)从内存获得所需的数据

4)如果必要,就存储结果

指令计数器从内存获得下一条指令码并且使之准备好进行处理。指令解码器用于把获得的

指令码解码为微操作。微操作是控制处理器芯片之内的特定信号来执行指令码的功能的代码。

微操作准备好后,控制单元把它传递给执行单元进行处理,并且获得所有要储存在正确位置的

结果。

NetBurst架构的特性如下:

指令预取和解码

分支预测

乱序执行

退役

图1-3

指令预取和解码管线

通过管线操作实现指令/数据预取。IA-32平台通过两级(或更多级)的缓存实现管线操作。第

一个缓存级别(称为L1)根据预测算法确定指令码或数据。为了解决程序按连续的顺序执行指

令,比如程序采用某一逻辑分支,创建了第二个缓存级别(L2)(越接近内存)。

图1-4

分支预测单元

缓存并没有解决”跳转的“程序问题。为了解决这个问题,提出了分支预测(branch

prediction)。奔4处理器使用3种技术实现分支预测:深度分支预测、动态数据流分析、推理性

执行。

乱序执行引擎

图1-5

从预取和解码管线获取的指令被分析和重新排序,使它们能尽快地被执行。通过大量分

析指令,乱序执行引擎能够找到那些在程序的其他部分需要它们之前随时可以执行(并且保存

它们的结果)的独立指令。

乱序执行引擎内有3个部分:

分配器

寄存器重命名

微操作调度器

退役单元

接收从管线解码器和乱序执行引擎发送过来的所有微操作,并试图把微操作重新调整为

程序嫩够正确执行的适当顺序。

简单整数操作(如加法,减法,布尔操作)

复杂整数操作(4个时钟处理大多数移位和循环指令,乘法和除法需要14-60时钟)

浮点操作(包含处理长度从64位到128位的数据元素寄存器,MMX和SSE)

通用寄存器

用于临时地存储数据。

EAX 是"累加器"(accumulator), 它是很多加法乘法指令的缺省寄存器。

EBX 是"基地址"(base)寄存器, 在内存寻址时存放基地址。

ECX 是计数器(counter), 是重复(REP)前缀指令和LOOP指令的内定计数器。

EDX 则总是被用来放整数除法产生的余数。

ESI/EDI分别叫做"源/目标索引寄存器"(source/destination index),因为在很多字符串操作指令中,

DS:ESI指向源串,而ES:EDI指向目标串.

EBP是"基址指针"(BASE POINTER), 它最经常被用作高级语言函数调用的"框架指针"(frame pointer).

ESP 专门用作堆栈指针,被形象地称为栈顶指针,堆栈的顶部是地址小的区域,压入堆栈的数

据越多,ESP也就越来越小。在32位平台上,ESP每次减少4字节

段寄存器

段寄存器专门用于引用内存位置。IA-32处理器平台允许3种不同的访问系统内存的方法:

平坦内存模式(所有指令、数据和堆栈包含在相同的地址空间中,线性地址)

分段内存模式(划分为独立的段,用段寄存器中的指针进行引用,逻辑地址)

实地址模式(实地址,偏移量为0)

指令指针寄存器

EIP寄存器,有时候称为程序计数器(program counter),它跟踪要执行的下一条指令码

控制寄存器

5个控制寄存器用于确定处理器的操作模式,还有当前正在执行的任务特性。

不能直接访问控制寄存器中的值,但是可以把控制寄存器中包含的数据传送给通用寄存

器。

言程序是重要的,因为它们是可以用于确定程序的功能是否成功执行的唯一途径。

IA-32平台使用单一的32位寄存器包含一组状态、控制和系统标志。EFLAGS寄存器包含

32位信息,这些信息被映射为表示信息的特定标志。按功能,标志被分为3组:

状态标志

控制标志

系统标志

状态标志

状态标志用于表明处理器进行的数学操作的结果。

控制标志

控制标志用于控制处理器中的特定行为。当前,只定义一个控制器标志--DF标志,即方

向标志。它用于控制处理器处理字符串的方式(置1递减,置0递增)。

系统标志

系统标志用于控制操作系统级别的操作。应用程序绝不应该试图修改系统标志。

Instruction,Multiple Data,SIMD)执行模式的第一种技术。

MMX环境包含处理器可以处理3种新的整数数据类型:

64位打包的字节整数

64位打包的字整数

64位打包的双字整数

MMX为了处理新的数据格式,MMX引入了8个FPU寄存器作为专用寄存器。命名为MM0

到MM7。

和视频会议的复杂浮点算术运算的性能。SSE引入了8个新的128位寄存器(XMM0到XMM7)

和一种新的数据类型----128位打包的单精度浮点数。

SSE2引入了5种新的数据类型:

128位打包的双精度浮点数

128位打包的字节整数

128位打包的字整数

128位打包的双字整数

128打包的四字整数

处理器中的两个或者多个逻辑处理器构成。每个逻辑处理器都包含通用、段、控制和调试寄存

器的完整集合。所有逻辑处理器共享相同的执行单元。乱序执行引擎负责处理不同逻辑处理器

提供的独立线程的指令码。

一、汇编语言由3个组件构成,它们用于定义程序操作:

1、操作码助记符

汇编语言程序的核心使用于创建程序的指令码。而为了轻松编写指令码,汇编器把助记符词汇和指令码功能等同对待(比如:push,mov,sub和call等)。

2、数据段

第一种方法是使用内存位置汇编语言中定义变量包括两个部分:

1)指向一个内存位置的标记

2)内存字节的数据类型和默认值

数据类型决定为变量保存多少字节。如下:

testvalue:

.long 150

message:

.ascii "This is a test message"

pi:

.float 3.14159

第二种方法是使用的堆栈,特别是函数调用

3、命令

命令用于帮助程序员创建指令码的工作更加容易,命令前面有个点号,这是命令和标记的不同之处。

最重要的命令之一是.section命令。这个命令定义内存段、汇编语言程序在其中定义元素。

二、IA-32 平台

1、计算机的四个基本组件:

图1-1

控制总线用于保持处理器和各个系统元素之间功能的同步。数据总线用于在处理器和外部

系统元素之间传送数据。处理器要把读取的内存地址放在地址总线上,然后内存存储单元作出

响应,把这个内存位置存储的值放到数据总线上以便处理器进行访问。

&n

3ff8

bsp; 处理器的主要组件如下:

控制单元

执行单元

寄存器

标志

图1-2显示了这些组件以及它们如何在处理器内进行交互。

图1-2

2、控制单元

处理器的中心是控制单元。主要作用是控制处理器在任何时候进行什么操作。在处理器运行时,必须从内存获得指令并且加载它们以便处理器进行处理。控制单元的工作是实现4个基本功

能:

1)从内存获得指令

2)对指令进行解码以便进行操作

3)从内存获得所需的数据

4)如果必要,就存储结果

指令计数器从内存获得下一条指令码并且使之准备好进行处理。指令解码器用于把获得的

指令码解码为微操作。微操作是控制处理器芯片之内的特定信号来执行指令码的功能的代码。

微操作准备好后,控制单元把它传递给执行单元进行处理,并且获得所有要储存在正确位置的

结果。

NetBurst架构的特性如下:

指令预取和解码

分支预测

乱序执行

退役

图1-3

指令预取和解码管线

通过管线操作实现指令/数据预取。IA-32平台通过两级(或更多级)的缓存实现管线操作。第

一个缓存级别(称为L1)根据预测算法确定指令码或数据。为了解决程序按连续的顺序执行指

令,比如程序采用某一逻辑分支,创建了第二个缓存级别(L2)(越接近内存)。

图1-4

分支预测单元

缓存并没有解决”跳转的“程序问题。为了解决这个问题,提出了分支预测(branch

prediction)。奔4处理器使用3种技术实现分支预测:深度分支预测、动态数据流分析、推理性

执行。

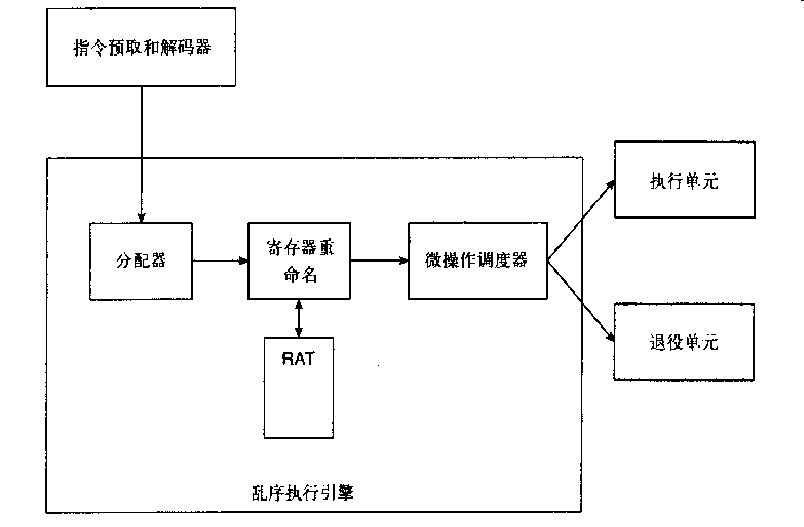

乱序执行引擎

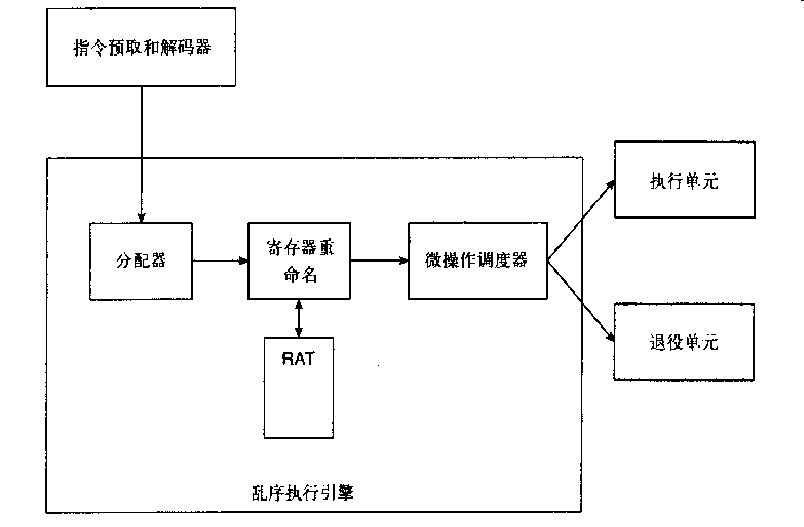

图1-5

从预取和解码管线获取的指令被分析和重新排序,使它们能尽快地被执行。通过大量分

析指令,乱序执行引擎能够找到那些在程序的其他部分需要它们之前随时可以执行(并且保存

它们的结果)的独立指令。

乱序执行引擎内有3个部分:

分配器

寄存器重命名

微操作调度器

退役单元

接收从管线解码器和乱序执行引擎发送过来的所有微操作,并试图把微操作重新调整为

程序嫩够正确执行的适当顺序。

3、执行单元

执行单元由一个或者多个运算逻辑单元(Arithmetic Logic Unit,ALU)构成。简单整数操作(如加法,减法,布尔操作)

复杂整数操作(4个时钟处理大多数移位和循环指令,乘法和除法需要14-60时钟)

浮点操作(包含处理长度从64位到128位的数据元素寄存器,MMX和SSE)

4、寄存器

寄存器加快处理器处理数据的速度。IA-32平台具有不同长度的多组寄存器。

通用寄存器

用于临时地存储数据。

EAX 是"累加器"(accumulator), 它是很多加法乘法指令的缺省寄存器。

EBX 是"基地址"(base)寄存器, 在内存寻址时存放基地址。

ECX 是计数器(counter), 是重复(REP)前缀指令和LOOP指令的内定计数器。

EDX 则总是被用来放整数除法产生的余数。

ESI/EDI分别叫做"源/目标索引寄存器"(source/destination index),因为在很多字符串操作指令中,

DS:ESI指向源串,而ES:EDI指向目标串.

EBP是"基址指针"(BASE POINTER), 它最经常被用作高级语言函数调用的"框架指针"(frame pointer).

ESP 专门用作堆栈指针,被形象地称为栈顶指针,堆栈的顶部是地址小的区域,压入堆栈的数

据越多,ESP也就越来越小。在32位平台上,ESP每次减少4字节

段寄存器

段寄存器专门用于引用内存位置。IA-32处理器平台允许3种不同的访问系统内存的方法:

平坦内存模式(所有指令、数据和堆栈包含在相同的地址空间中,线性地址)

分段内存模式(划分为独立的段,用段寄存器中的指针进行引用,逻辑地址)

实地址模式(实地址,偏移量为0)

指令指针寄存器

EIP寄存器,有时候称为程序计数器(program counter),它跟踪要执行的下一条指令码

控制寄存器

5个控制寄存器用于确定处理器的操作模式,还有当前正在执行的任务特性。

不能直接访问控制寄存器中的值,但是可以把控制寄存器中包含的数据传送给通用寄存

器。

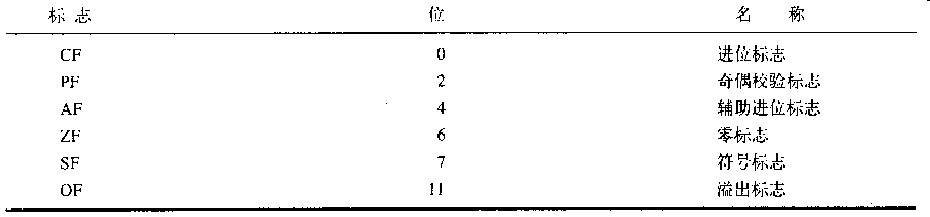

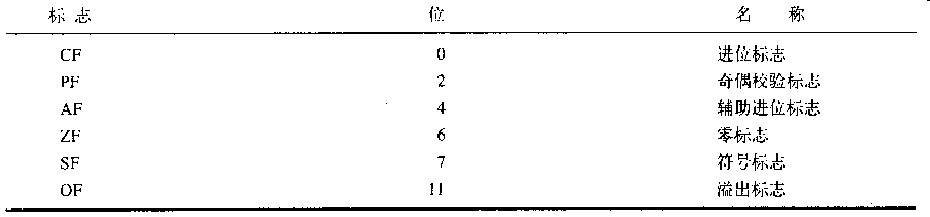

5、标识

对于处理器中实现的每个操作,都必须有一种机制来确定操作是否成功。标识对汇编语言程序是重要的,因为它们是可以用于确定程序的功能是否成功执行的唯一途径。

IA-32平台使用单一的32位寄存器包含一组状态、控制和系统标志。EFLAGS寄存器包含

32位信息,这些信息被映射为表示信息的特定标志。按功能,标志被分为3组:

状态标志

控制标志

系统标志

状态标志

状态标志用于表明处理器进行的数学操作的结果。

控制标志

控制标志用于控制处理器中的特定行为。当前,只定义一个控制器标志--DF标志,即方

向标志。它用于控制处理器处理字符串的方式(置1递减,置0递增)。

系统标志

系统标志用于控制操作系统级别的操作。应用程序绝不应该试图修改系统标志。

6、多媒体扩展

多媒体扩展(multimedia extension,MMX)是支持Intel的单指令多数据(SingleInstruction,Multiple Data,SIMD)执行模式的第一种技术。

MMX环境包含处理器可以处理3种新的整数数据类型:

64位打包的字节整数

64位打包的字整数

64位打包的双字整数

MMX为了处理新的数据格式,MMX引入了8个FPU寄存器作为专用寄存器。命名为MM0

到MM7。

7、流化SIMD扩展

流化SIMD扩展(Streaming SIMD extension,SSE)增强了经常用于3D图形、动态视频和视频会议的复杂浮点算术运算的性能。SSE引入了8个新的128位寄存器(XMM0到XMM7)

和一种新的数据类型----128位打包的单精度浮点数。

SSE2引入了5种新的数据类型:

128位打包的双精度浮点数

128位打包的字节整数

128位打包的字整数

128位打包的双字整数

128打包的四字整数

8、超线程

超线程使单一IA-32处理器能够同时处理多个程序执行线程。超线程技术由位于单一物理处理器中的两个或者多个逻辑处理器构成。每个逻辑处理器都包含通用、段、控制和调试寄存

器的完整集合。所有逻辑处理器共享相同的执行单元。乱序执行引擎负责处理不同逻辑处理器

提供的独立线程的指令码。

相关文章推荐

- 汇编语言简介(二)

- Linux2.4打开一个文件的系统调用

- Linux2.6系统调用

- 数论-Special Numbers

- 《重构》第一章 笔记

- 背包问题

- Linux2.6-4G的线性地址空间的分配与使用

- 快速选择

- redis的持久化

- LychrelNumber实现V1.0

- 算法导论 第10章 10.3 指针和对象实现

- 百度面试经历

- 算法导论-15-3-编辑距离

- 第16章 贪心算法

- docker误区

- 使用Python处理目录(一):打印目录下的文件名

- 算法导论 第22章 图算法 22.3 深度优先搜索

- 算法导论-14.3-6-MIN-GAP

- 算法导论 14.1-7 顺序统计树求逆序对 O(nlgn)

- 2012-9-23 搜狗笔试