FPGA第三篇:加法器

2016-04-21 16:08

344 查看

本文转自半加器 全加器 多位加法器减法器设计

特别声明:根据个人理解,添加与删除了一些内容

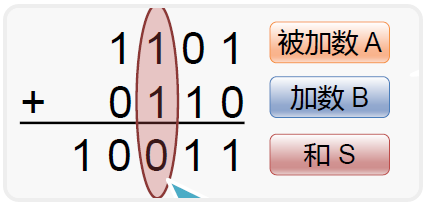

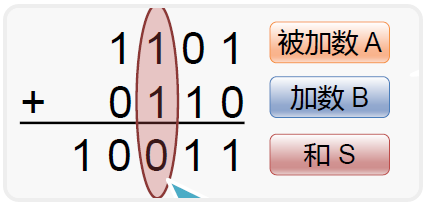

二进制加法

一位的二进制加法非常简单,因为只有四种情况

0+0=0 进位0

0+1=1 进位0

1+0=1 进位0

1+1=0 进位1

多位的二进制加法 和十进制类似,每一位上两个数相加后再加上进位就可以了

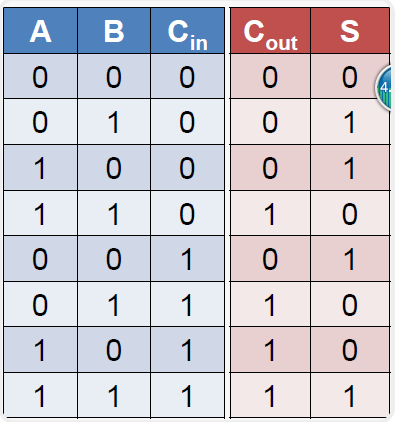

真值表:

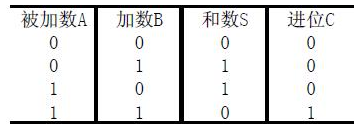

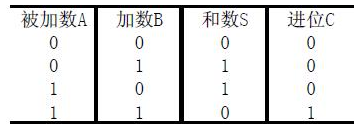

一位半加器真值表

由表中可以看见,这种加法没有考虑低位来的进位,所以称为半加。

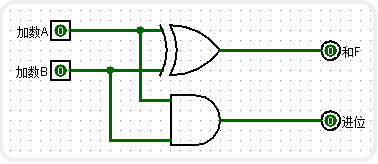

输出和:A和B一个为0 一个为1的时候输出1 两个0或两个1输出0 因此 可以用异或门连接。

进位:只有AB均为1的时候进位输出1 进位Cout = AB 用与门连接。

一位半加器

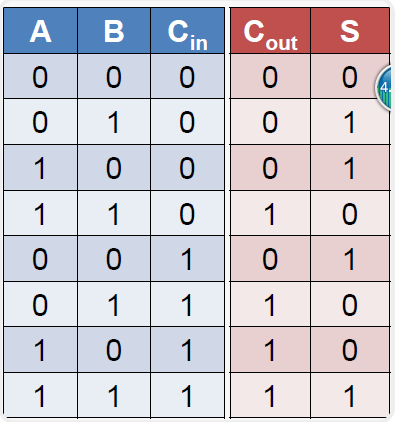

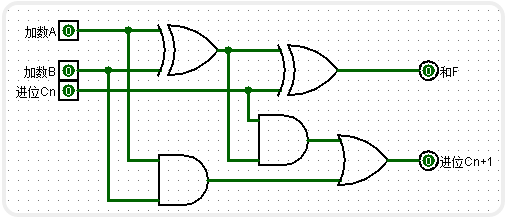

一位全加器真值表

从真值表很容易写出如下逻辑表达式

S=P异或Cout 其中P=A异或B

Cout=P·Cin+G 其中G=A·B

一位全加器

Verilog语言实现

`timescale 1 ns / 1 ps

module sum ( A ,Co ,B ,S ,Ci );

input A ;

wire A ;

input B ;

wire B ;

input Ci ;

wire Ci ;

output Co ;

reg Co ;

output S ;

reg S ;

always @ ( A or B or Ci)

begin

if ( A== 0 && B == 0 && Ci == 0 )

begin

S <= 0;

Co <= 0;

end

else if ( A== 1 && B == 0 && Ci == 0 )

begin

S <= 1;

Co <= 0;

end

else if ( A== 0 && B == 1 && Ci == 0 )

begin

S <= 1;

Co <= 0;

end

else if ( A==1 && B == 1 && Ci == 0 )

begin

S <= 0;

Co <= 1;

end

else if ( A== 0 && B == 0 && Ci == 1 )

begin

S <= 1;

Co <= 0;

end

else if ( A== 1 && B == 0 && Ci == 1 )

begin

S <= 0;

Co <= 1;

end

else if ( A== 0 && B == 1 && Ci == 1 )

begin

S <= 0;

Co <= 1;

end

else

begin

S <= 1;

Co <= 1;

end

end

endmodule

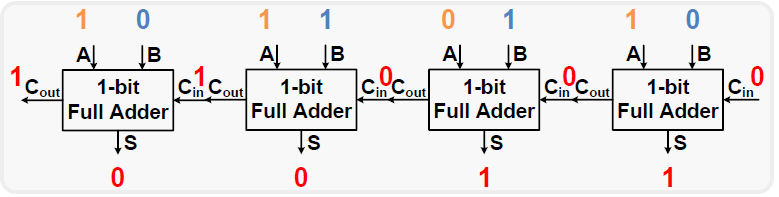

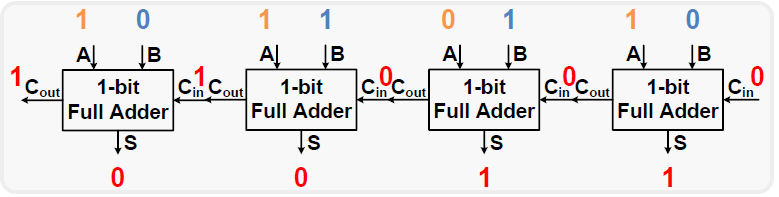

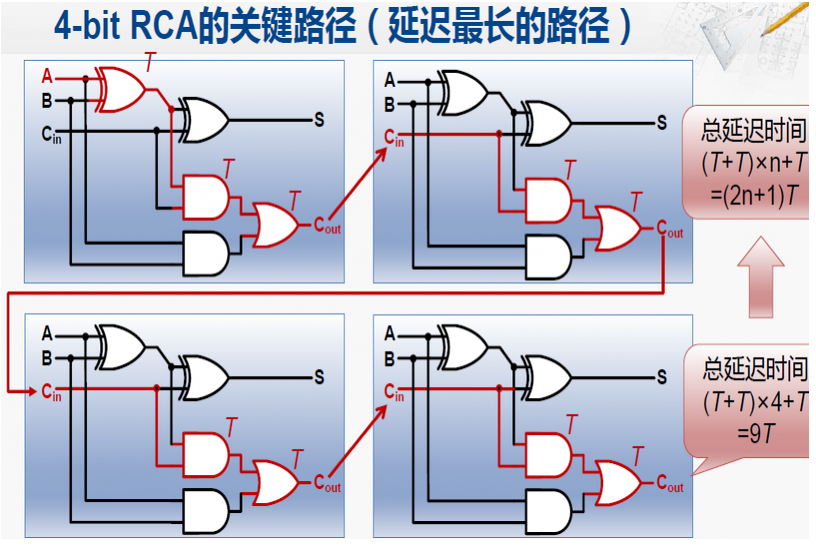

四位行波加法器

这样构成的加法器连接起来很简单,但是也有不足:每一个全加器计算的时候必须等待它的进位输入产生后才能计算,所以四个全加器并不是同时进行计算的,而是一个一个的串行计算。这样会造成较大的延迟。

我们先看一个二进制数字 A 假设8位

A按位取反之后 记为~A

那么 A + ~A = 1111 1111

计算机中使用补码表示数字 1111 1111表示的数字是多少呢?最高位为1 是负数 然后取反加一 是0000 0001 绝对值是1 这个数字是-1

也就是 A + ~A = -1 也就是有 -A = ~A + 1

所以 计算A-B 就等于 A + (-B) = A + (~B + 1)

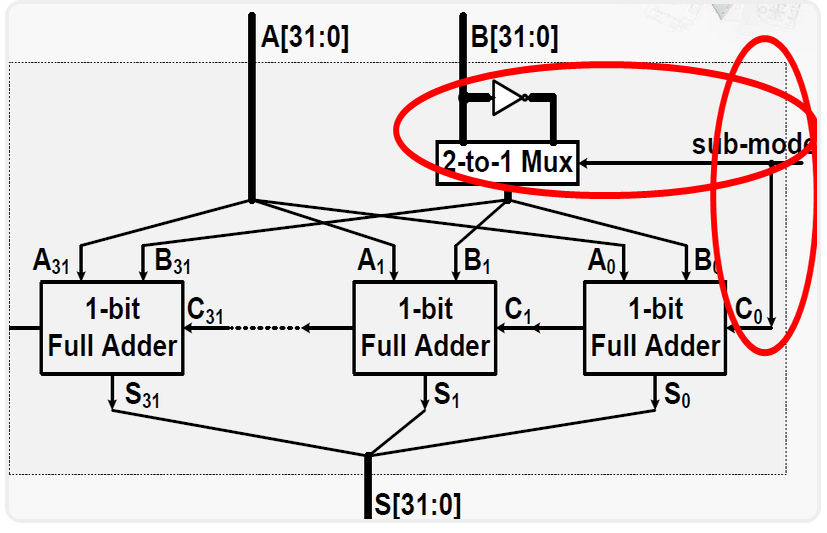

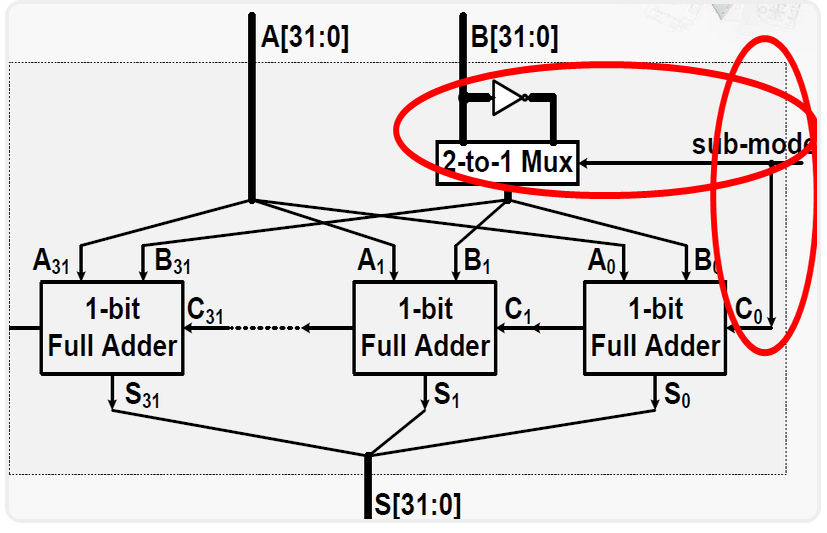

只要将B连接到一个非门 生成~B 然后增加一个多选器,根据减法信号 决定把B还是~B送入加法器。由于减法运算的时候还要+1 因此 加法器的最初的进位连接到减法信号 如果是减法就让最初的进位等于1

32位全加/减器

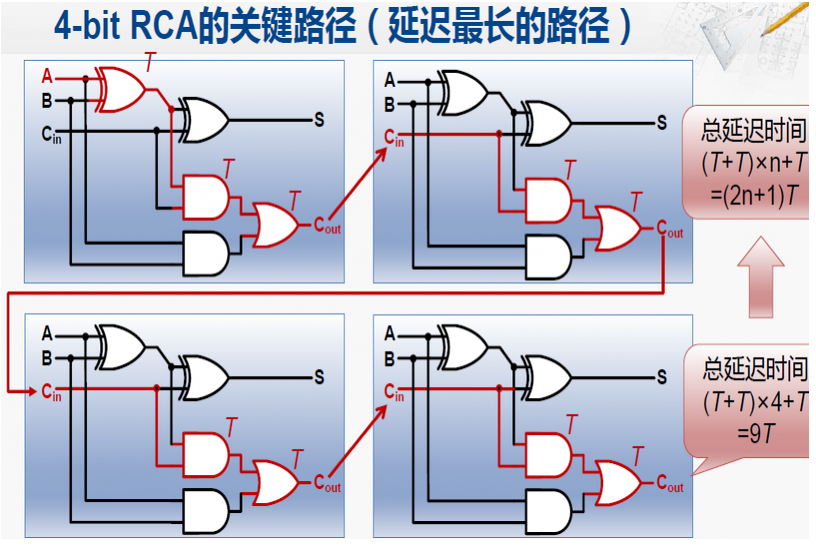

可以看出,如果n位串在一起,门延迟是2*n+1

分析每一个全加器的局部

一个全加器 A B Cn 如果有两个或两个以上的1 那么进位Cn+1就是1

因此 Cn+1 = AB + ACn + BCn = AB + Cn(A+B)

记生成(Generate)信号:Gi=Ai·Bi

传播(Propagate)信号:Pi=Ai+Bi

那么Ci+1=Gi+Pi·Ci

根据这个递推关系,可以推导出每一位的进位

每一位的进位跟前一级进位有关,前一级 又跟 前一级的前一级有关 一直向前 最终是和C0相关。而最开始的第一位C0和A0 B0都是已知的

这样算出结果只需要经过三个门延迟就可以了。

随着位数的增加,进位的计算公式会越来越复杂。32位的进位计算需要32与门

特别声明:根据个人理解,添加与删除了一些内容

一、加法器

计算机最基本的功能就是运算了,其中最基本的又要属加法运算。我们知道计算机使用二进制来保存和处理数据,因此这里的加减法运算都是用二进制进行。下面雅乐网总结了一些运算器中加法器的设计。二进制加法

一位的二进制加法非常简单,因为只有四种情况

0+0=0 进位0

0+1=1 进位0

1+0=1 进位0

1+1=0 进位1

多位的二进制加法 和十进制类似,每一位上两个数相加后再加上进位就可以了

1、半加器

半加器可以实现两个1位的二进制数字相加,并且输出结果和进位。真值表:

一位半加器真值表

由表中可以看见,这种加法没有考虑低位来的进位,所以称为半加。

输出和:A和B一个为0 一个为1的时候输出1 两个0或两个1输出0 因此 可以用异或门连接。

进位:只有AB均为1的时候进位输出1 进位Cout = AB 用与门连接。

一位半加器

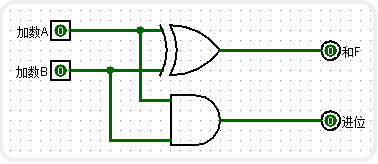

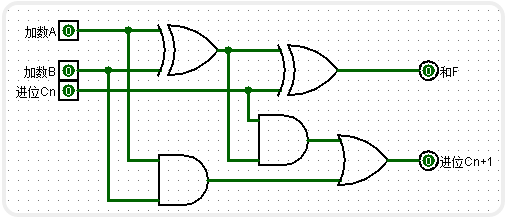

2、全加器

全加器在半加器的基础上 增加了进位 它输入三个数字 两个加数 和 一个进位 Cin,输出结果 和 进位

一位全加器真值表

从真值表很容易写出如下逻辑表达式

S=P异或Cout 其中P=A异或B

Cout=P·Cin+G 其中G=A·B

一位全加器

Verilog语言实现

`timescale 1 ns / 1 ps

module sum ( A ,Co ,B ,S ,Ci );

input A ;

wire A ;

input B ;

wire B ;

input Ci ;

wire Ci ;

output Co ;

reg Co ;

output S ;

reg S ;

always @ ( A or B or Ci)

begin

if ( A== 0 && B == 0 && Ci == 0 )

begin

S <= 0;

Co <= 0;

end

else if ( A== 1 && B == 0 && Ci == 0 )

begin

S <= 1;

Co <= 0;

end

else if ( A== 0 && B == 1 && Ci == 0 )

begin

S <= 1;

Co <= 0;

end

else if ( A==1 && B == 1 && Ci == 0 )

begin

S <= 0;

Co <= 1;

end

else if ( A== 0 && B == 0 && Ci == 1 )

begin

S <= 1;

Co <= 0;

end

else if ( A== 1 && B == 0 && Ci == 1 )

begin

S <= 0;

Co <= 1;

end

else if ( A== 0 && B == 1 && Ci == 1 )

begin

S <= 0;

Co <= 1;

end

else

begin

S <= 1;

Co <= 1;

end

end

endmodule

3、四位行波加法器

将四个全加器 每一个的仅为输出连接到下一个的进位输入 就可以构成一个4位串行加法器了

四位行波加法器

这样构成的加法器连接起来很简单,但是也有不足:每一个全加器计算的时候必须等待它的进位输入产生后才能计算,所以四个全加器并不是同时进行计算的,而是一个一个的串行计算。这样会造成较大的延迟。

二、减法器

1、数学基础

其实,减去一个数,等于加上这个数的相反数。所以,可以考虑使用加法运算代替减法运算。我们先看一个二进制数字 A 假设8位

A按位取反之后 记为~A

那么 A + ~A = 1111 1111

计算机中使用补码表示数字 1111 1111表示的数字是多少呢?最高位为1 是负数 然后取反加一 是0000 0001 绝对值是1 这个数字是-1

也就是 A + ~A = -1 也就是有 -A = ~A + 1

所以 计算A-B 就等于 A + (-B) = A + (~B + 1)

2、电路

电路中,只需要增加一个减法信号。0表示加法 1表示减法只要将B连接到一个非门 生成~B 然后增加一个多选器,根据减法信号 决定把B还是~B送入加法器。由于减法运算的时候还要+1 因此 加法器的最初的进位连接到减法信号 如果是减法就让最初的进位等于1

32位全加/减器

三、行波进位加法器的延迟

上面提到,这种加法器高位的加法必须等待低位加法器运算完毕才能进行,存在延迟

可以看出,如果n位串在一起,门延迟是2*n+1

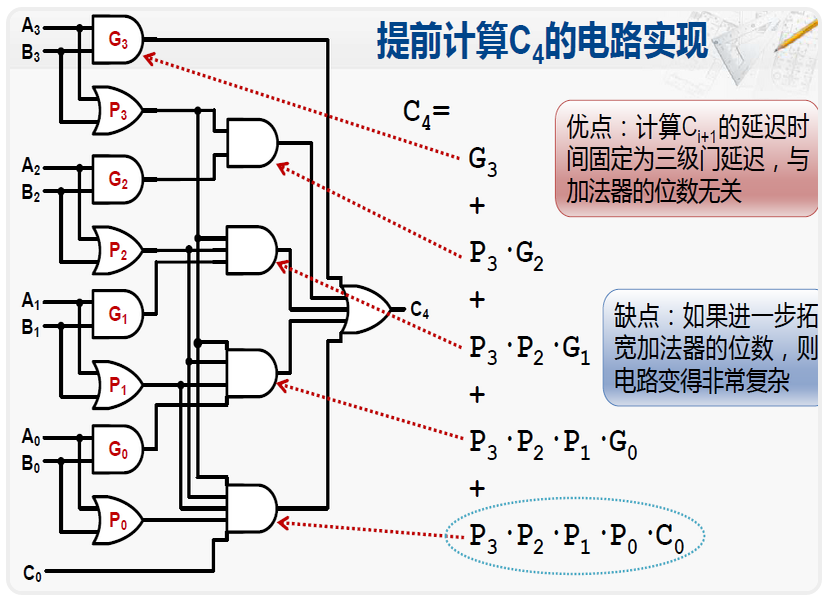

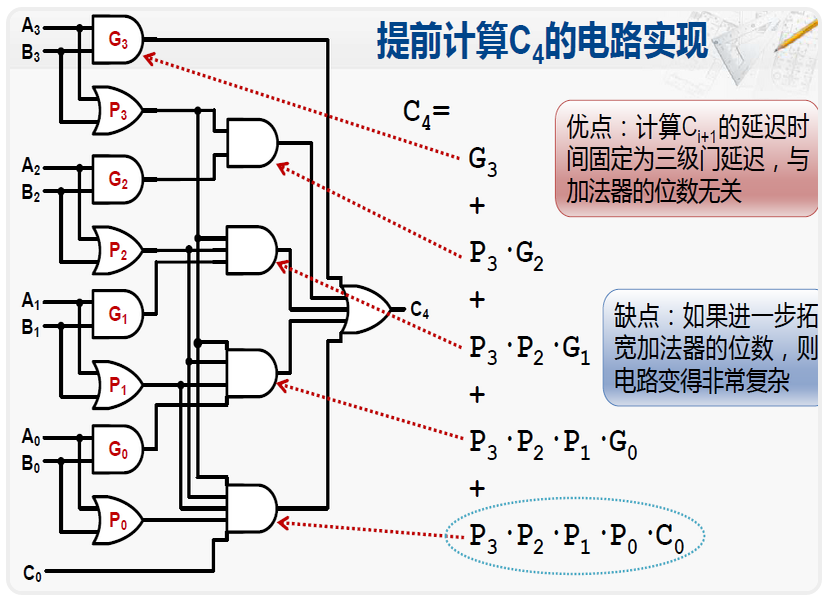

四、超前进位加法器(Carry-Lookahead Adder,CLA)

超前进位加法器的思路是提前算出每一位上的进位。分析每一个全加器的局部

一个全加器 A B Cn 如果有两个或两个以上的1 那么进位Cn+1就是1

因此 Cn+1 = AB + ACn + BCn = AB + Cn(A+B)

记生成(Generate)信号:Gi=Ai·Bi

传播(Propagate)信号:Pi=Ai+Bi

那么Ci+1=Gi+Pi·Ci

根据这个递推关系,可以推导出每一位的进位

每一位的进位跟前一级进位有关,前一级 又跟 前一级的前一级有关 一直向前 最终是和C0相关。而最开始的第一位C0和A0 B0都是已知的

这样算出结果只需要经过三个门延迟就可以了。

随着位数的增加,进位的计算公式会越来越复杂。32位的进位计算需要32与门

五、总结——串行和并行结合的加法器

实际中,通常采用多个小规模的超前进位加法器串联拼接成更多位数的加法器,例如用4个8-bit的超前进位加法器连接成32-bit加法器。相关文章推荐

- Web渗透测试求职问答大全

- hdoj 5666 Segment 【二进制优化乘法】

- 对weblogic一些量化的认识

- Android研发规范

- java多线程编程的volatile应用

- Linux /etc/login.defs配置文件

- Android 音频系统 1 -- codec

- 1.5 显示进度对话框---ProgressDialog

- USACO-Section 4.3 Street Race (枚举&&BFS)

- Shell编写

- JDK之jstat的用法

- HDU1045 Fire Net DFS

- 使用Yeoman搭建 AngularJS 应用 (11) —— 让我们搭建一个网页应用

- 每日Scrum--No.3

- ASP.NET MVC 3 入门级常用设置、技巧和报错

- textfield中键盘风格

- 10倍效率的程序员的好习惯,你有几个?

- hdoj 5665 Lucky 【水题】

- Shell图形界面dialog应用详解

- 文章标题