FPGA BCD计数器(一位)

2016-01-30 20:46

369 查看

模块代码:

testbench代码:

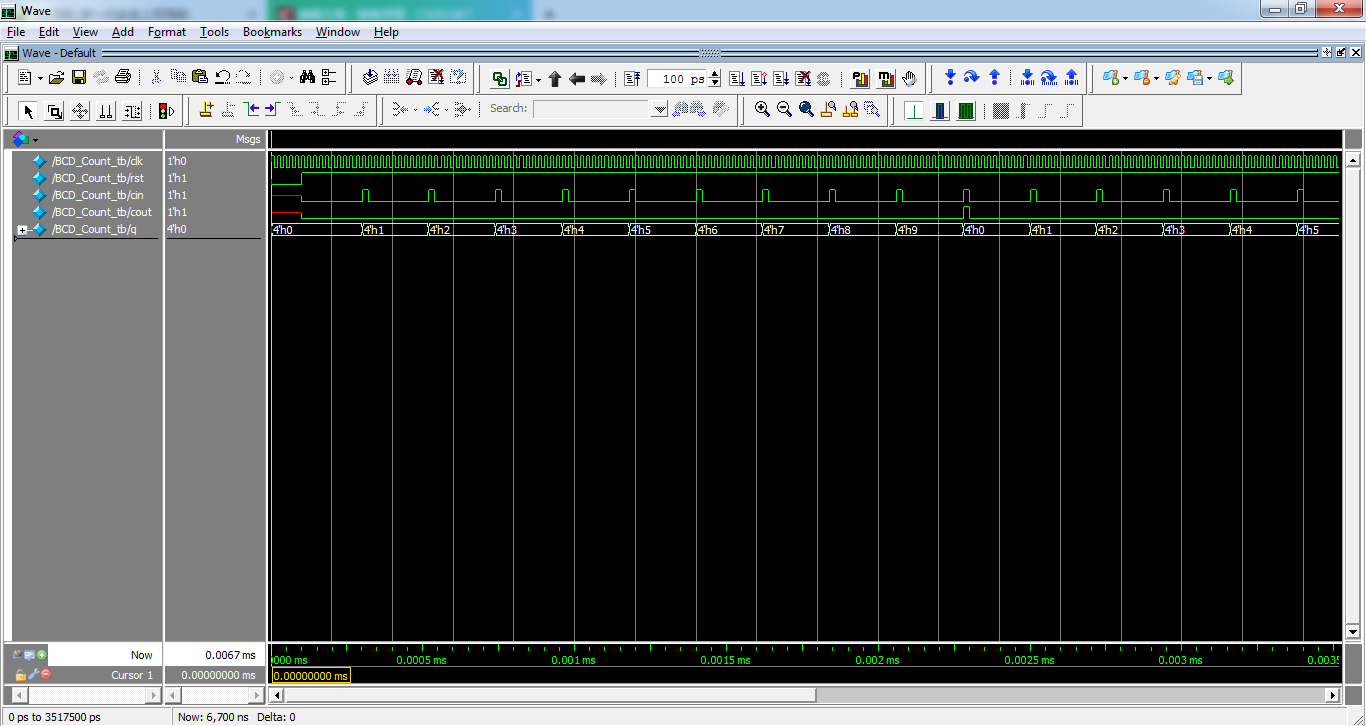

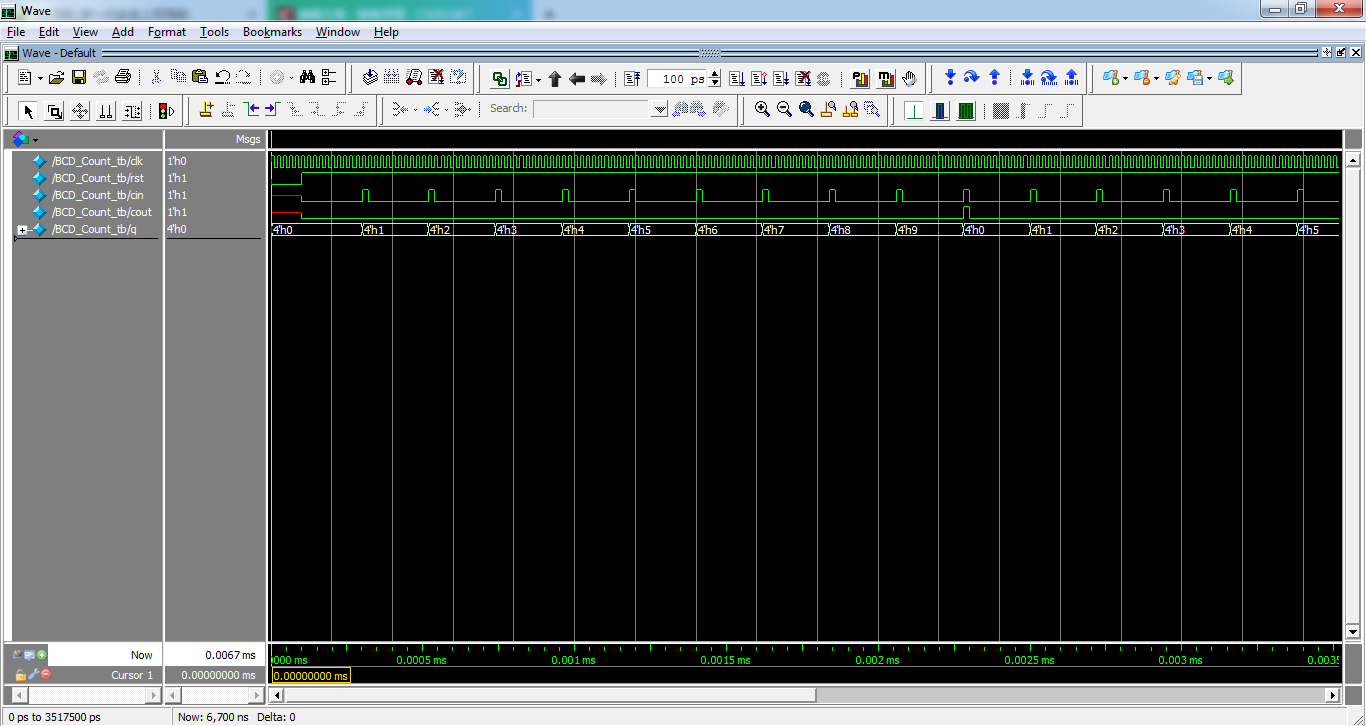

RTL仿真结果:

module BCD_Count(Clk,Rst_n,Cin,Cout,q); input Clk; input Rst_n; input Cin; output reg Cout; output [3:0] q; reg [3:0] cnt; always@( posedge Clk or negedge Rst_n ) begin if( Rst_n==0 ) cnt<=0; else if( Cin==1 ) begin if( cnt==9 ) begin cnt<=0; Cout<=1; end else cnt<=cnt+1; end else if( Cin==0 ) Cout<=0; end assign q=cnt; endmodule

testbench代码:

`timescale 1ns/1ns `define Time_Periord 20 module BCD_Count_tb; reg clk; reg rst; reg cin; wire cout; wire [3:0] q; BCD_Count BCD_Count0 ( .Clk(clk), .Rst_n(rst), .Cin(cin), .Cout(cout), .q(q) ); initial clk=1; always #(`Time_Periord/2) clk=~clk; initial begin rst=0; #100; rst=1; repeat( 30 ) begin cin=0; #(`Time_Periord*10); cin=1; #(`Time_Periord*1); end $stop; end endmodule

RTL仿真结果:

相关文章推荐

- 《FPGA嵌入式项目开发实战》

- 关于FPGA中的Logic Cells, Logic Slices, Configurable Logic Blocks and Gates

- DSP多网口开发板

- Utilities Zynq in a PL only configuration

- ARM+FPGA核心板

- DSP+ARM+FPGA核心板

- 基于VHDL的按键扫描程序

- Xilinx FPFA中LUT4_L 元件的使用

- ISE 综合面积报告分析

- 深圳嵌入式培训 修练软硬件之功 高薪一路相伴

- FPGA点灯

- 深圳视晶无线技术有限公司 狗血经历

- 卫星导航同步时的环路更新时间架构

- 载波同步环路的带宽与信噪比相关问题

- 如何解决NO EPCS LAYOUT DATA --- LOOKING FOR SECTION [EPCS-XXXXXX]

- FPGA基于CORDIC算法的求平方实现

- 应用matlab&modelsim设计FPGA算法(1)

- 《Xilinx可编程逻辑器件设计与开发(基础篇)》连载21:Spartan-6的时钟资源

- 阻塞与非阻塞(blocking and non-blocking)

- FPGA里怎么做小数乘法