我的 FPGA 学习历程(12)—— 电子钟项目准备

2015-12-31 12:02

232 查看

初学 FPGA 的时候,我们总是存在很多疑问,比如:xilinx 和 altera 的 FPGA 那种比较好、verilog 语言被如何综合成具体硬件电路、RTL 级电路是什么意思等等。现在我们就不会迷惑于那些基本的概念问题,是时候来写一个小小的项目了。我决定编写一个没有日期功能的电子钟,还可以来复习以前学过的模块。

这个项目有些复杂,一次不太可能成功,所以我们先写一个秒表,秒表的组成大概如下:

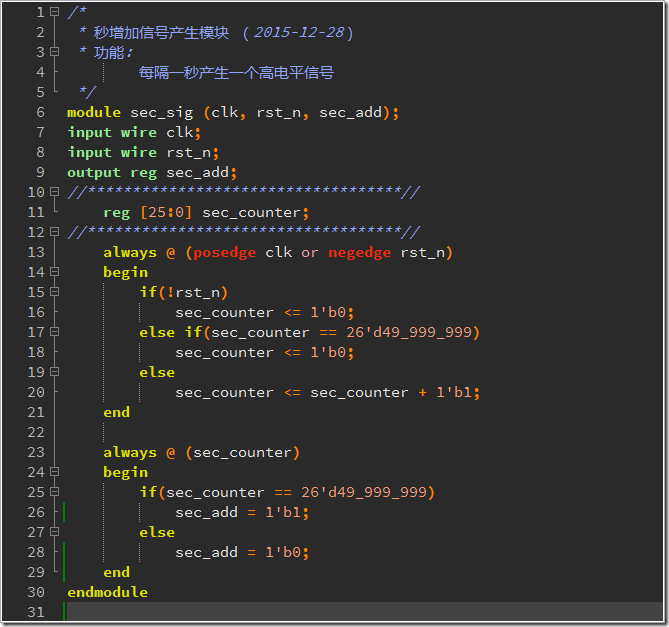

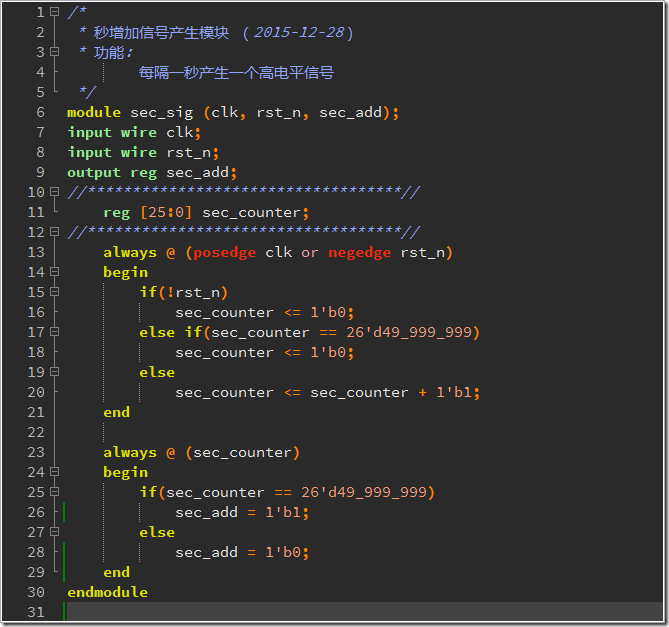

秒增加信号产生模块。

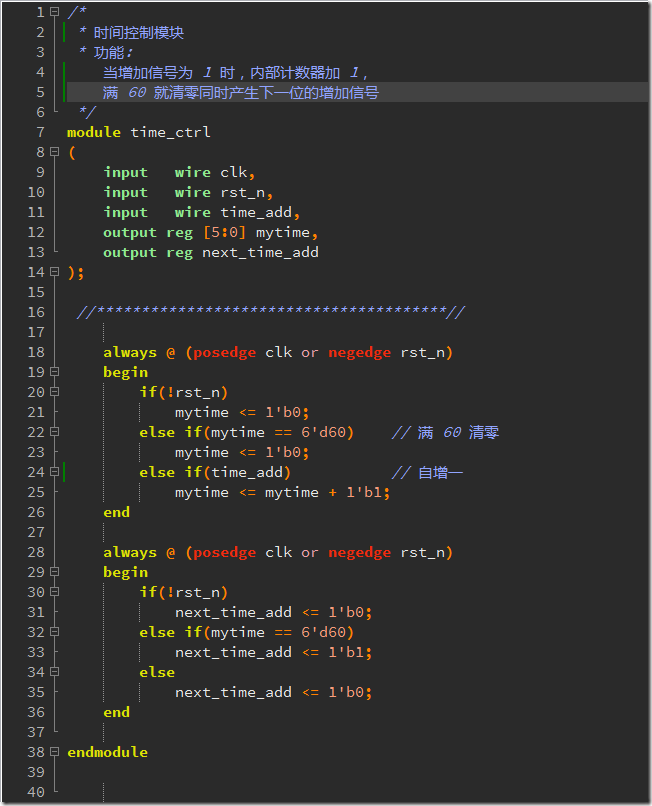

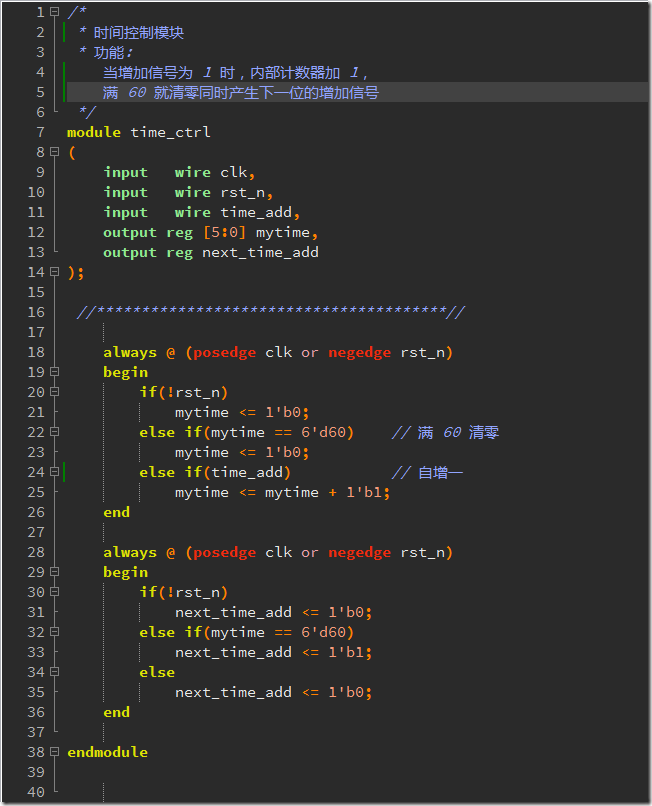

时间计数模块1,当增加信号为 1 时加 1,满 60 清零,并产生分增加信号。

时间计数模块2,当增加信号为 1 时加 1,满 60 清零,并产生小时增加信号。

时间计数模块3,当增加信号为 1 时加 1,满 60 清零。 (小 bug,如果本实验没能成功,后面的电子钟就没发做了)

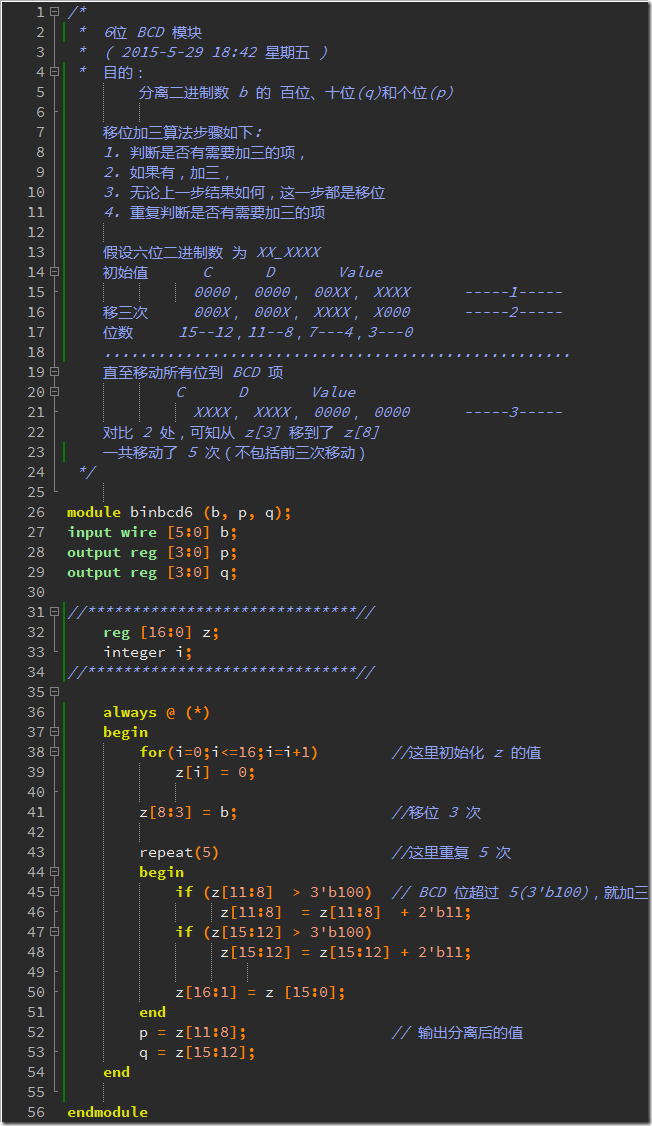

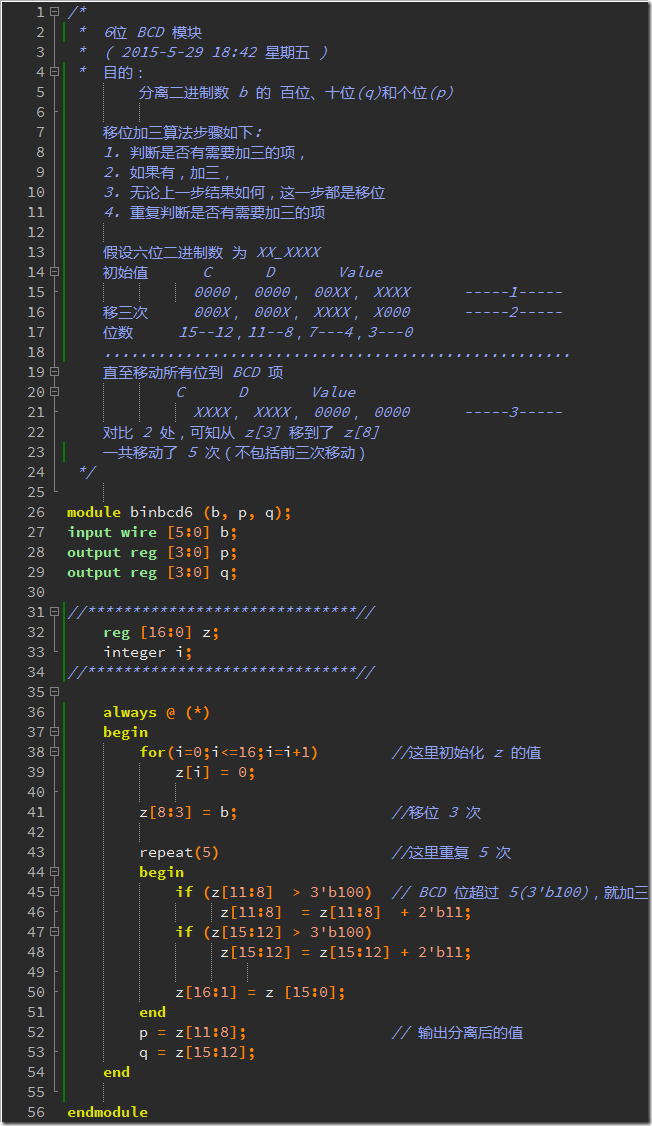

秒计数、分计数、小时计数模块寄存器中的值转化为 BCD 数 24'h??-??-??。

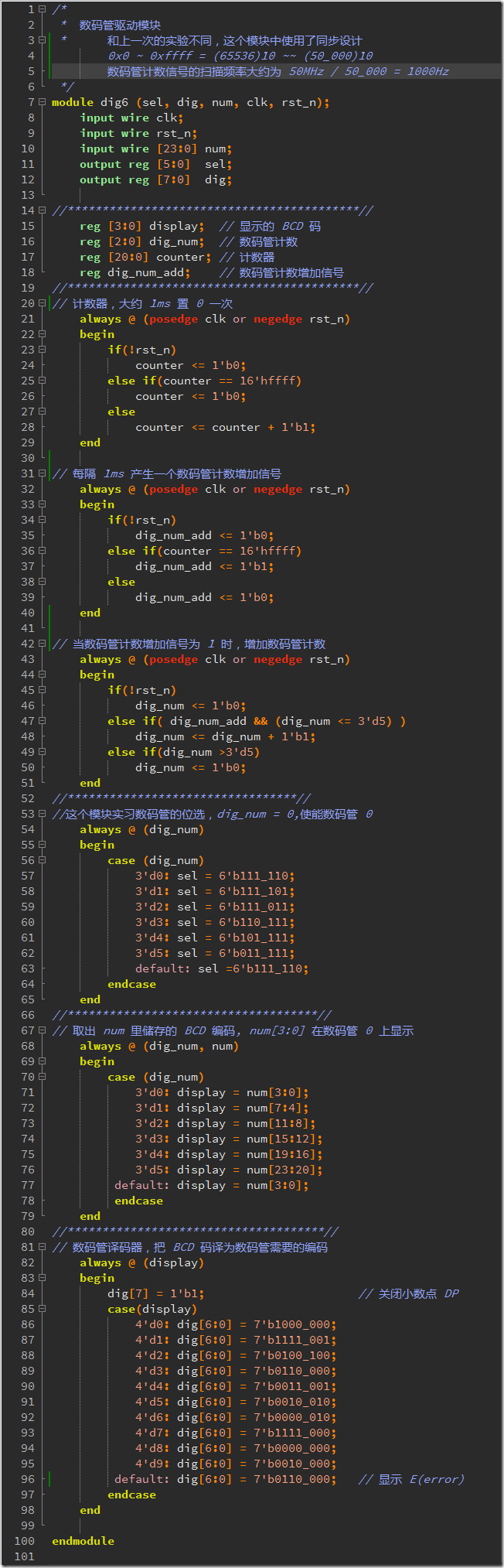

最后使用数码管驱动模块来显示时间,此外秒表还需要一个复位按钮和一个暂停按钮。

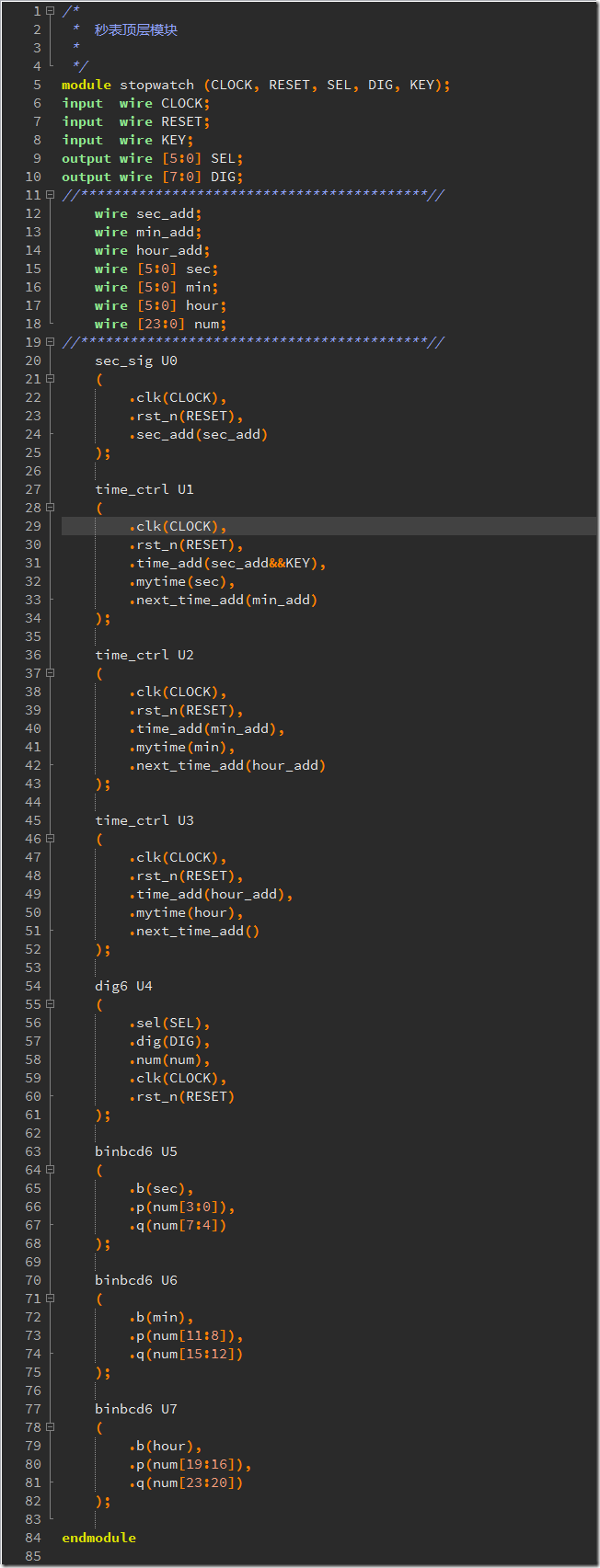

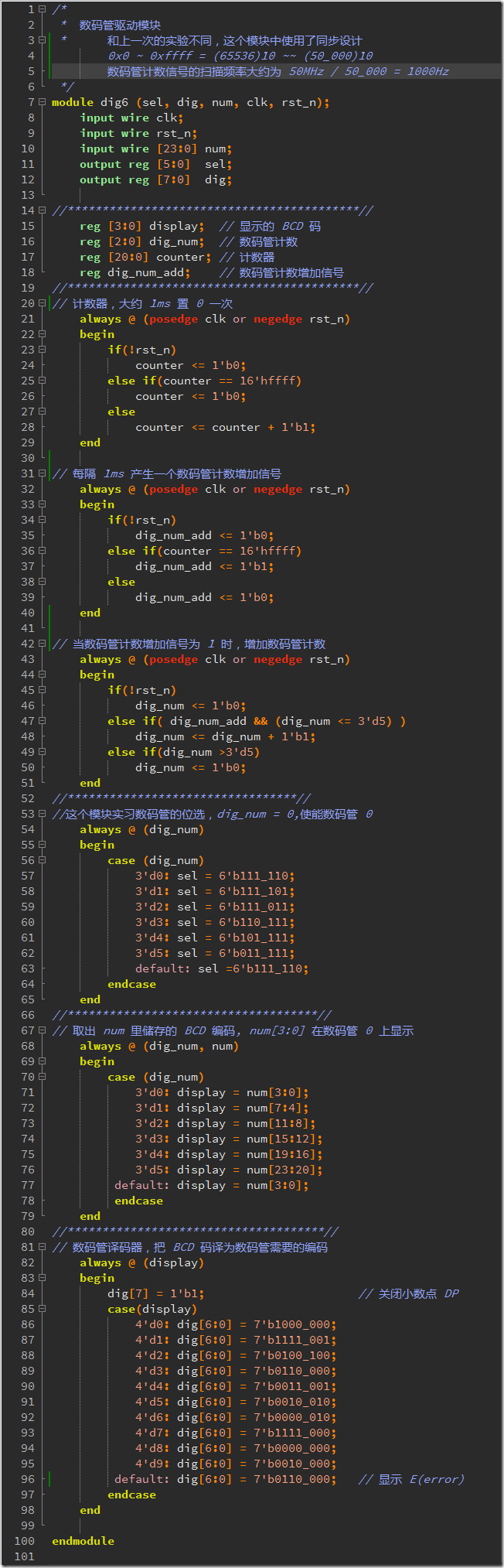

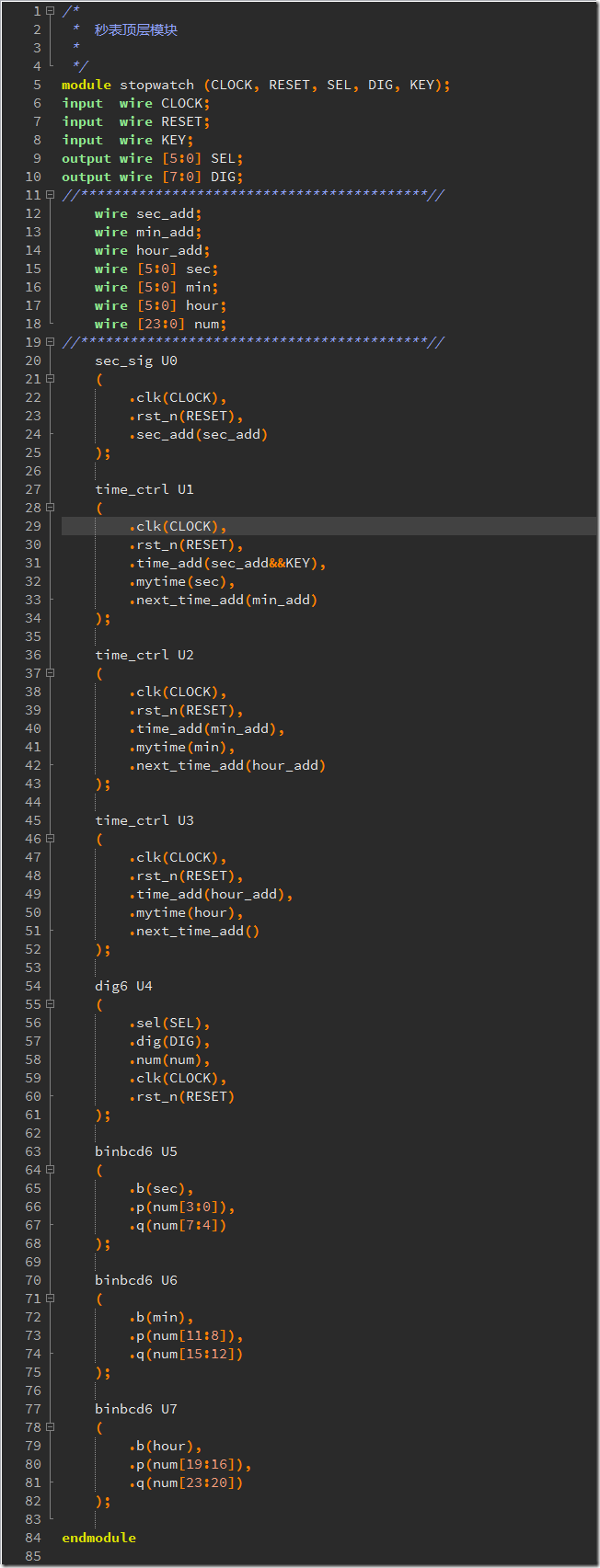

了解完结构之后,下一步就是考虑如何编写代码了,我的代码如下:

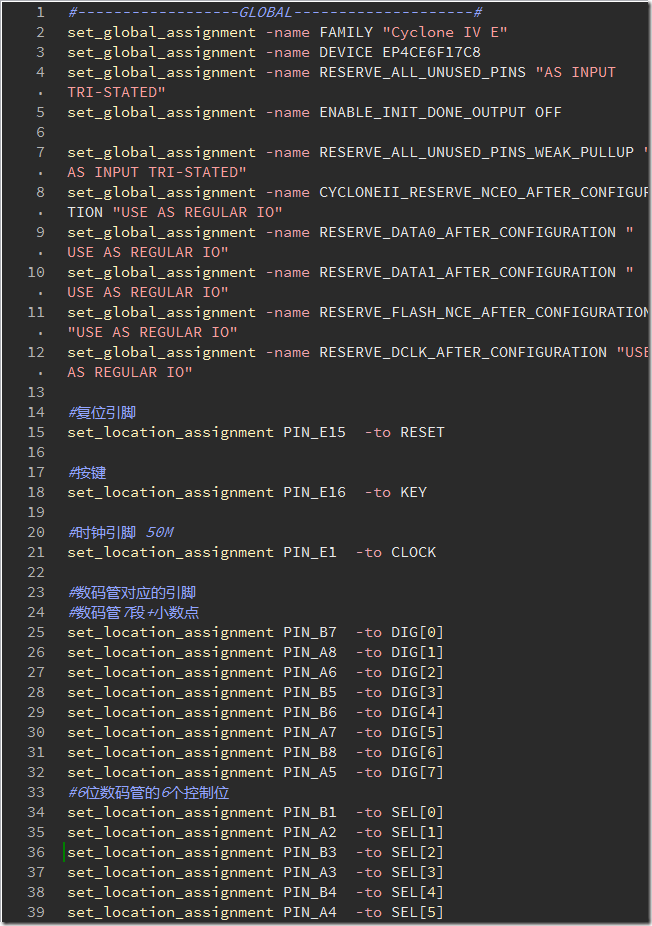

注意:顶层模块中的 信号名称是大写的,用于适配 tcl 脚本文件

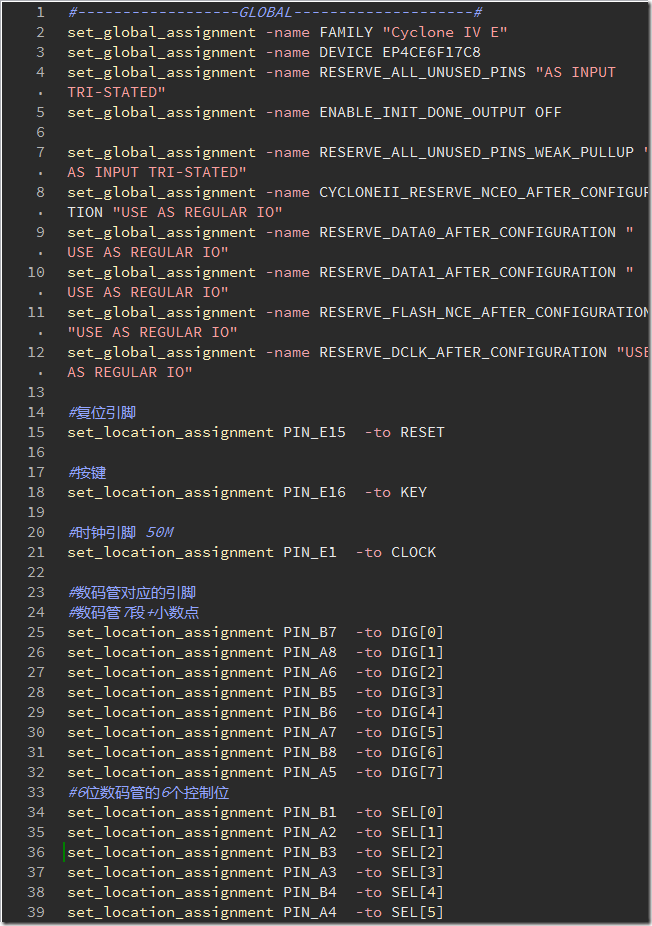

本次实验可用的 tcl 脚本文件如下:(其中 KEY 是修改后的名字)

编译,下载,然后看看板子上的效果,你成功了吗?(⊙o⊙)

这个项目有些复杂,一次不太可能成功,所以我们先写一个秒表,秒表的组成大概如下:

秒增加信号产生模块。

时间计数模块1,当增加信号为 1 时加 1,满 60 清零,并产生分增加信号。

时间计数模块2,当增加信号为 1 时加 1,满 60 清零,并产生小时增加信号。

时间计数模块3,当增加信号为 1 时加 1,满 60 清零。 (小 bug,如果本实验没能成功,后面的电子钟就没发做了)

秒计数、分计数、小时计数模块寄存器中的值转化为 BCD 数 24'h??-??-??。

最后使用数码管驱动模块来显示时间,此外秒表还需要一个复位按钮和一个暂停按钮。

了解完结构之后,下一步就是考虑如何编写代码了,我的代码如下:

注意:顶层模块中的 信号名称是大写的,用于适配 tcl 脚本文件

本次实验可用的 tcl 脚本文件如下:(其中 KEY 是修改后的名字)

编译,下载,然后看看板子上的效果,你成功了吗?(⊙o⊙)

相关文章推荐

- android中cardview的基本使用

- php实现微信公众号主动推送消息

- javascript判断输入是否为空

- oracle查看dbid

- 使用Java反射(Reflect)、自定义注解(Customer Annotation)生成简单SQL语句

- SQL还原数据库剔除占用

- PostgreSQL Partitions

- Linux和Windows生成系统时间命名的文件

- H.264数据流格式

- iphone个人热点找不到

- git:将某个commit或其中某个文件修改提取出来

- Android---绘图

- zend studio 9实用快捷键大全 分享ZEND STUDIO 9的常用快捷键,高亮显示相同变量。

- 存储过程中动态SQL

- 多线程实现变色龙

- json_decode()和json_encode()的使用方法

- java基础tips

- Android二维码扫描、生成

- Android二维码扫描、生成

- jabref【参考文献生成,抓去,推送,管理工具】简介