fpga状态机详解

2015-11-17 20:43

337 查看

什么是状态机:状态机通过不同的状态迁移来完成特定的逻辑操作

状态机的分类:Moore型状态机和Mealy型状态机

Moore型:状态机的变化只与当前的状态有关

Mealy型:状态机的变化不仅与当前的状态有关,还与输入有关

如何创建状态机:状态机的创建可以分为一段式,两段式和三段式

一段式:主要是讲所有的状态变化以及导致的输出变化都写在了一个always快中。

两段式:将一些复位信号,clk信号单独写在一个always快中,其他的状态变化,输出值得变化写在一个always快中。

三段式:将一些复位信号,clk信号单独写在一个always快中,其他的状态迁移变化写在一个always快中,对应状态的输出值得变化写在一个always快中。

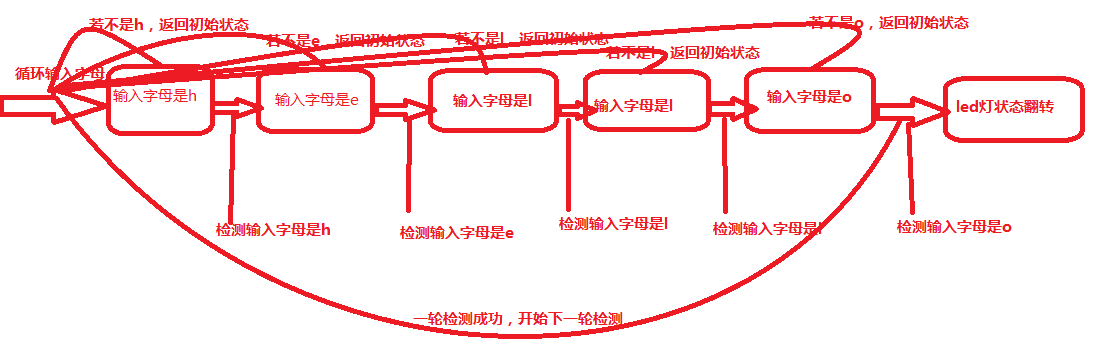

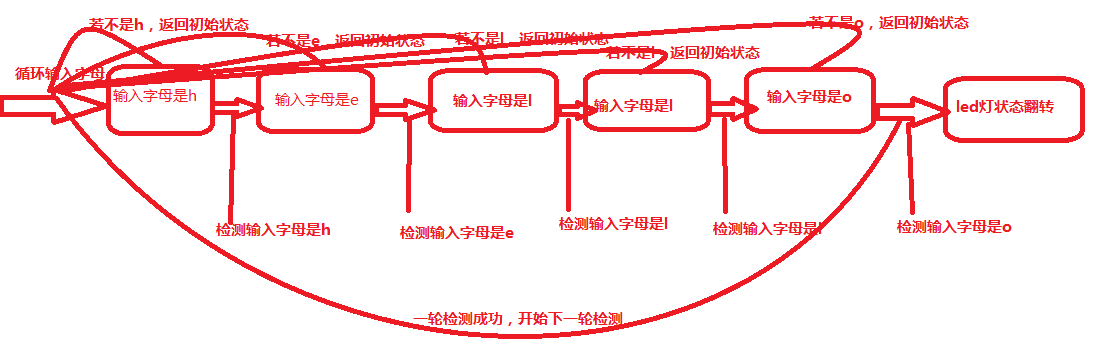

举个例子:从循环输入的字母中做连续检测,当连续检测到“hello”时,将led灯进行状态的翻转,继续进行下一次的检测。

一段式的编写方式:

两段式的编写方式:

三段式的编写方式:

注意

一般的状态机是使用Always语句和case语句组合来实现的

不可以根据Always快的个数来判断他是属于几段的状态机

一般情况下不建议使用一段式状态机,建议使用二和三段式状态机,二段式状态机使用时序逻辑处理状态变化,组合逻辑处理输入输出的变化,结构比较清晰,但容易产生毛刺

三段式从输入到输出会比一、两段式状态机延时一个时钟周期

状态机的分类:Moore型状态机和Mealy型状态机

Moore型:状态机的变化只与当前的状态有关

Mealy型:状态机的变化不仅与当前的状态有关,还与输入有关

如何创建状态机:状态机的创建可以分为一段式,两段式和三段式

一段式:主要是讲所有的状态变化以及导致的输出变化都写在了一个always快中。

两段式:将一些复位信号,clk信号单独写在一个always快中,其他的状态变化,输出值得变化写在一个always快中。

三段式:将一些复位信号,clk信号单独写在一个always快中,其他的状态迁移变化写在一个always快中,对应状态的输出值得变化写在一个always快中。

举个例子:从循环输入的字母中做连续检测,当连续检测到“hello”时,将led灯进行状态的翻转,继续进行下一次的检测。

一段式的编写方式:

module hello( input clk,//系统时钟信号 50mHz input rst_n,//系统复位信号,低电平有效 input [7:0] data,//连续输入的字母 output reg led//led灯 ); //设置需要改变的状态 parameter checkh = 5'b0000_1, checke = 5'b0001_0, checkla = 5'b0010_0, checklb = 5'b0100_0, checko = 5'b1000_0; reg [4:0]state; always @(posedge clk or negedge rst_n) if(!rst_n) begin led <= 1'b0; state <= checkh; end else begin case (state) checkh: if(data == "h") state <= checke; else state <= checkh; checke: if(data == "e") state <= checkla; else state <= checkh; checkla: if(data == "l") state <= checklb; else state <= checkh; checklb: if(data == "l") state <= checko; else state <= checkh; checko: if(data == "o") begin led <= ~led; state <= checkh; end else state <= checkh; default:state <= checkh; endcase end endmodule

两段式的编写方式:

module hello( input clk, input rst_n, input [7:0] data, output reg led ); parameter checkh = 5'b0000_1, checke = 5'b0001_0, checkla = 5'b0010_0, checklb = 5'b0100_0, checko = 5'b1000_0; reg [4:0] cstate; reg [4:0] nstate; always @(posedge clk or negedge rst_n) if(!rst_n) begin cstate <= checkh; end else cstate <= nstate; always @(cstate or data) case (cstate) checkh: if(data == "h") nstate <= checke; else nstate <= checkh; checke: if(data == "e") nstate <= checkla; else nstate <= checkh; checkla: if(data == "l") nstate <= checklb; else nstate <= checkh; checklb: if(data == "l") nstate <= checko; else nstate <= checkh; checko: if(data == "o") begin led <= ~led; nstate <= checkh; end else nstate <= checkh; default:nstate <= checkh; endcase endmodule

三段式的编写方式:

module hello( input clk, input rst_n, input [7:0] data, output reg led ); parameter checkh = 5'b0000_1, checke = 5'b0001_0, checkla = 5'b0010_0, checklb = 5'b0100_0, checko = 5'b1000_0; reg [4:0] cstate; reg [4:0] nstate; //复位信号,clk的处理(主要是对初始状态进行赋值操作) always @(posedge clk or negedge rst_n) if(!rst_n) begin cstate <= checkh; end else cstate <= nstate; //状态迁移的处理 always @(cstate or data) case (cstate) checkh: if(data == "h") nstate <= checke; else nstate <= checkh; checke: if(data == "e") nstate <= checkla; else nstate <= checkh; checkla: if(data == "l") nstate <= checklb; else nstate <= checkh; checklb: if(data == "l") nstate <= checko; else nstate <= checkh; checko: if(data == "o") begin nstate <= checkh; end else nstate <= checkh; default:nstate <= checkh; endcase //输出数据的处理 always @(posedge clk or negedge rst_n) if(!rst_n) begin led <= 1'b1; end else case (cstate) checko: if(data == "o") led <= ~led; default; endcase endmodule

注意

一般的状态机是使用Always语句和case语句组合来实现的

不可以根据Always快的个数来判断他是属于几段的状态机

一般情况下不建议使用一段式状态机,建议使用二和三段式状态机,二段式状态机使用时序逻辑处理状态变化,组合逻辑处理输入输出的变化,结构比较清晰,但容易产生毛刺

三段式从输入到输出会比一、两段式状态机延时一个时钟周期

相关文章推荐

- javascript与有限状态机详解

- 《FPGA嵌入式项目开发实战》

- 剖析 Qt 实现动画状态机实例

- 关于FPGA中的Logic Cells, Logic Slices, Configurable Logic Blocks and Gates

- DSP多网口开发板

- Utilities Zynq in a PL only configuration

- ARM+FPGA核心板

- DSP+ARM+FPGA核心板

- 去掉C/C++源程序中的注释

- 基于VHDL的按键扫描程序

- Xilinx FPFA中LUT4_L 元件的使用

- ISE 综合面积报告分析

- 深圳嵌入式培训 修练软硬件之功 高薪一路相伴

- FPGA点灯

- 深圳视晶无线技术有限公司 狗血经历

- Android StateMachine解析( 1 )

- 卫星导航同步时的环路更新时间架构

- 载波同步环路的带宽与信噪比相关问题

- 如何解决NO EPCS LAYOUT DATA --- LOOKING FOR SECTION [EPCS-XXXXXX]

- FPGA基于CORDIC算法的求平方实现