八位三态数据通路控制器的逻辑电路设计讲解

2015-10-18 10:40

274 查看

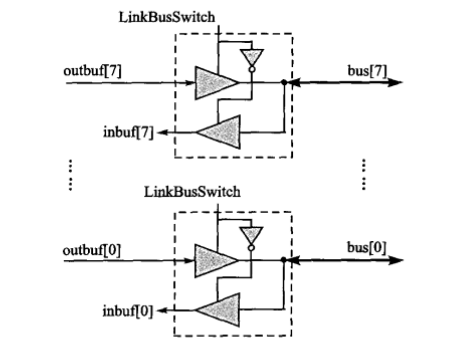

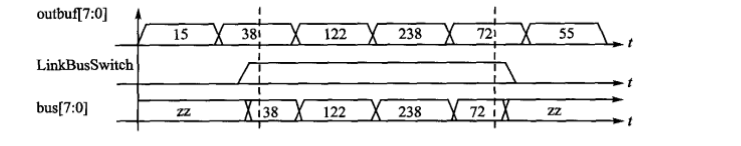

1、如图这是电路逻辑结构图及其时序逻辑图:

2、verilog程序:

`define ON 1'b1`define OFF 1'b0

wire LinkBusSwitch;

wire[7:0] outbuf;

wire[7:0] inbuf;

inout[7:0] bus;

assign bus=(LinkBusSwitch==`ON) ? outbuf : 8'bzz;

always@(posedge clk)

begin

//此处略去些许代码。。。。

if(!LinkBusSwitch)

inbuf <= bus;

end

//此处略去些许代码。。。。

endmodule

3、高阻是什么?

在这里当LinkBusSwitch是0 时,我们的outbuf 是高阻,也就是和bus断开了,高阻嘛?就是阻值很高,别的电流就过不来了。当outbuf是高阻值得时候,其就与bus断开了,那么我们的bus就可以被其他器件线路利用了。

****************************************************************************

made by qidaiYMM, your comment is appreciated.

email:151988261@qq.com

相关文章推荐

- UVA-1615 Highway (贪心,区间选点)

- 六盘山之行

- Objective-C Foundation框架实践——NSString(二)

- hadoop 0.20.2 搭建

- Redis、memcache

- 我的人生三大主航线

- IOS添加控件

- 云计算硬件交换设备参数配置考虑

- 零长度的数组-编译器的解释

- 修改Android中Layout布局文件字体的大小

- nodejs综合

- 传输层TCP和UDP的区别分析与应用场景【转载】

- Python beautifulsoup的安装与使用

- 微信企业号开发之中文编码 40006

- 简单记录下VC中常用的播放音频API用法

- 冒泡排序法

- 安装gVim

- 微信企业号开发之中文编码 40006

- Oracle数据泵的使用

- java中的线程(三)——控制线程的几种简单的方法和线程同步