PowerPC PPC460-S MMU(五 Storage Control Registers)

2015-08-19 09:48

309 查看

Overview

MMUCR

SWOA

U1TE

U2SWOAE

DULXE

IULXE

STS

STID

PIDProcess ID

当然,除了本文两个控制寄存器外,在MSR[IS,DS]也会定义相关的控制,以及MSR[PR]也控制

着访问模式。

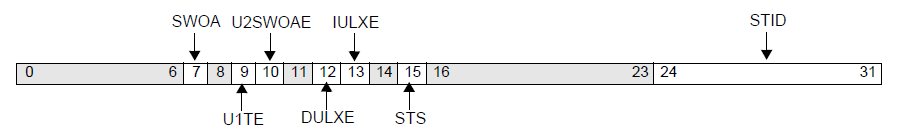

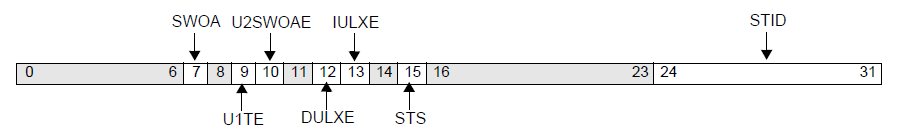

寄存器图示如下:

其中,有一点需要注意:

STID虽然是Search Translation ID(对于TLB搜索指令tlbsx定义的TID域值),但是调用TLB的

读取指令tlbre时,STID值会更新为当前读取的TLB Entry的TID值;同样地,当调用TLB的更新

指令tlbwe时,TLB Entry的TID值会更新为STID值(也即TLB Entry更新指令中TID并不会根据

GPR的值来更新,而是根据MMUCR中的STID值更新)

这个属性控制对于可Cache的缺页(数据丢失)是否要在Data Cache中重新分配Cache Line.

当U2SWOAE = 1时(“访问不需要重配”已使能),此项配置忽略。

此处的U1也就是上文(四)中介绍的用户自定义的Storage Attribute之一,此属性用来控制使能(1)

或禁能(0)瞬态存储Transient Storage.

使能或禁能不重配Cache Line;

这个控制属性用于使能或禁能在用户模式下执行dcbf指令是否引发缓存上锁中异常类型的数据存储中断;

由于dcbf指令会使在Data Cache中的相关Cache Line 冲刷掉(Flushed),而在用户模式下时调用

了这个指令,可能某个Application会移除一个已经上锁的Cache Line。使能这个属性后,对于PPC460S

内核,不管目标CacheLine是否上锁,上锁中异常都会发生,然后由数据存储中断处理程序来决定应用程

序是否可以解锁此CacheLine;

注意:如果此位未使能(0),或者在管理员模式下执行了dcbf指令,那么指令执行后会冲刷目标Cache

Line(无论是否已经上锁)。

控制属性原理同上(数据Cache的解锁异常使能),只是针对的指令为icbi指令(冲刷的是指令Cache)

属性控制用于TLB搜索指令tlbsx所搜寻的地址空间(数据空间或指令空间)

注意:

在TLB Entry的定义中TS位需要与MSR中的IS以及DS位保持一致。

(即指令空间的定义要与IS保持一致,数据空间要与DS保持一致)

而对于tlbsx指令来说,通过配置MMUCR(STS)来主动决定搜寻空间。

属性主要用来在TLB搜索指令tlbsx执行时,通过STID与TLB Entry定义中的TID域进行比较以

加快搜索。

注意:

对于指令取指、数据存储以及缓存管理中,TLB Entry中定义的TID主要与PID

寄存器来比较,但是对于搜索来说,就可以与MMUCR中的STID来比较。

8位的有效位作为虚拟地址的一部分,用来和TLB Entry定义中的TID域进行比较,进而确定当前的Entry

是否与对应的虚拟地址匹配(当然如果TID域定义为0了,则PID值就会忽略,不再参与比较,因为当前

定义的TLB Entry为全局共享的)

PID寄存器的操作指令也是基于GPR的mtspr指令。

MMUCR

SWOA

U1TE

U2SWOAE

DULXE

IULXE

STS

STID

PIDProcess ID

Overview

本文主要介绍PPC460s内存管理相关的控制寄存器MMUCR和PID。当然,除了本文两个控制寄存器外,在MSR[IS,DS]也会定义相关的控制,以及MSR[PR]也控制

着访问模式。

MMUCR

MMUCR的读写操作指令为基于GPR的 ‘mtspr’指令。寄存器图示如下:

其中,有一点需要注意:

STID虽然是Search Translation ID(对于TLB搜索指令tlbsx定义的TID域值),但是调用TLB的

读取指令tlbre时,STID值会更新为当前读取的TLB Entry的TID值;同样地,当调用TLB的更新

指令tlbwe时,TLB Entry的TID值会更新为STID值(也即TLB Entry更新指令中TID并不会根据

GPR的值来更新,而是根据MMUCR中的STID值更新)

SWOA

Store Without Allocate Control:这个属性控制对于可Cache的缺页(数据丢失)是否要在Data Cache中重新分配Cache Line.

当U2SWOAE = 1时(“访问不需要重配”已使能),此项配置忽略。

U1TE

U1 Transient Enable Control:此处的U1也就是上文(四)中介绍的用户自定义的Storage Attribute之一,此属性用来控制使能(1)

或禁能(0)瞬态存储Transient Storage.

U2SWOAE

U2 Store without allocate Enable:使能或禁能不重配Cache Line;

DULXE

Data Cache Unlock Exception Enable:这个控制属性用于使能或禁能在用户模式下执行dcbf指令是否引发缓存上锁中异常类型的数据存储中断;

由于dcbf指令会使在Data Cache中的相关Cache Line 冲刷掉(Flushed),而在用户模式下时调用

了这个指令,可能某个Application会移除一个已经上锁的Cache Line。使能这个属性后,对于PPC460S

内核,不管目标CacheLine是否上锁,上锁中异常都会发生,然后由数据存储中断处理程序来决定应用程

序是否可以解锁此CacheLine;

注意:如果此位未使能(0),或者在管理员模式下执行了dcbf指令,那么指令执行后会冲刷目标Cache

Line(无论是否已经上锁)。

IULXE

Instruction Cache Unlock Exception Enable:控制属性原理同上(数据Cache的解锁异常使能),只是针对的指令为icbi指令(冲刷的是指令Cache)

STS

Search Translation Space:属性控制用于TLB搜索指令tlbsx所搜寻的地址空间(数据空间或指令空间)

注意:

在TLB Entry的定义中TS位需要与MSR中的IS以及DS位保持一致。

(即指令空间的定义要与IS保持一致,数据空间要与DS保持一致)

而对于tlbsx指令来说,通过配置MMUCR(STS)来主动决定搜寻空间。

STID

Search Translation ID:属性主要用来在TLB搜索指令tlbsx执行时,通过STID与TLB Entry定义中的TID域进行比较以

加快搜索。

注意:

对于指令取指、数据存储以及缓存管理中,TLB Entry中定义的TID主要与PID

寄存器来比较,但是对于搜索来说,就可以与MMUCR中的STID来比较。

PID(Process ID)

32位的PID寄存器只有低8位有效。8位的有效位作为虚拟地址的一部分,用来和TLB Entry定义中的TID域进行比较,进而确定当前的Entry

是否与对应的虚拟地址匹配(当然如果TID域定义为0了,则PID值就会忽略,不再参与比较,因为当前

定义的TLB Entry为全局共享的)

PID寄存器的操作指令也是基于GPR的mtspr指令。

相关文章推荐

- Lua的内存管理浅析

- PowerShell获取当前进程PID的小技巧

- linux mysql 报错:MYSQL:The server quit without updating PID file

- iisapp.vbs iis pid了解对应的网站或应用池

- w3wp.exe占用cpu过高的解决方法第1/2页

- 怎样通过iisapp命令查找pid来解决IIS的cpu占用率过高问题

- 深入探讨PHP中的内存管理问题

- linux 内存管理机制详细解析

- 解析PHP中的内存管理,PHP动态分配和释放内存

- MySQL下PID文件丢失的相关错误的解决方法

- javascript内存管理详细解析

- JavaScript内存管理介绍

- Cocos2d-x的内存管理总结

- 模拟实现C语言中的内存管理

- javascript错误的认识不用关心内存管理

- Python深入学习之内存管理

- 简单说说STL的内存管理

- Android中的UID和PID意义,及查看方式

- InnoDB存储引擎的内存管理机制

- jemalloc优化MySQL、Nginx内存管理