时钟定时器课程设计multisim电路仿真

2014-12-01 00:47

281 查看

时钟定时器课程设计multisim电路仿真

都是泪....

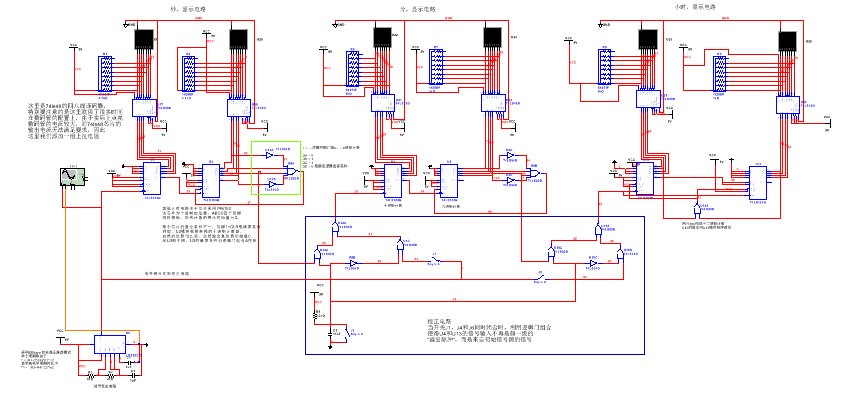

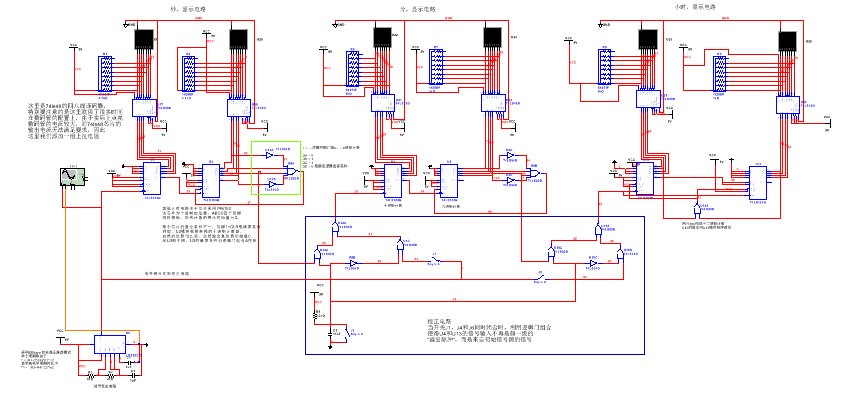

进入正题,先给出整个仿真电路,然后对各个模块进行逐一分析.

下载文件基于multisim12制作,因此低于该版本的multisim无法打开,请注意使用multisim12:

下载链接:

http://download.csdn.net/detail/u011368821/8211361

不需要积分即可下载

电路概览:

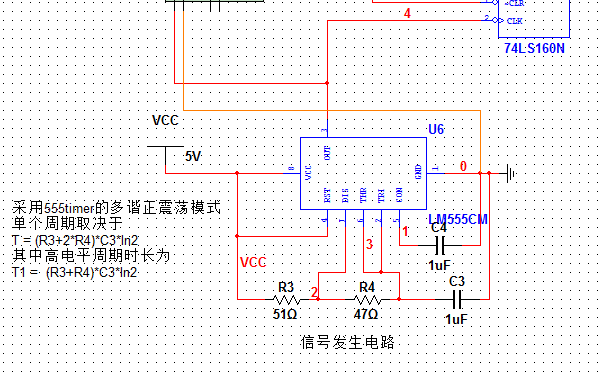

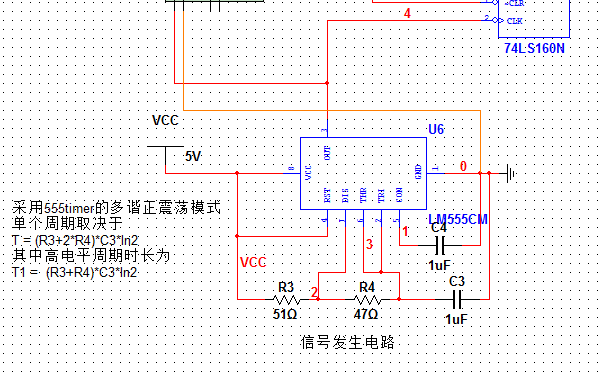

信号发生模块,采用555timer的多谐振荡模式

该模式下的特点在电路注释中有说明.

如果忘记555timer怎么用的,下面是复习link

http://blog.csdn.net/cinmyheart/article/details/33362853

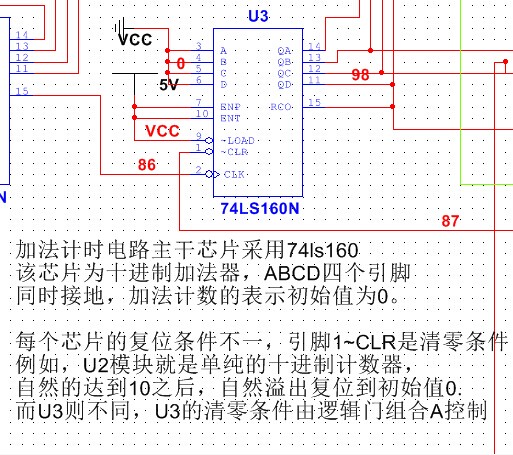

信号发生电路的产生信号提供给160十进制计数器

可以去这里看74ls160 74ls48z

http://blog.csdn.net/cinmyheart/article/details/26705425

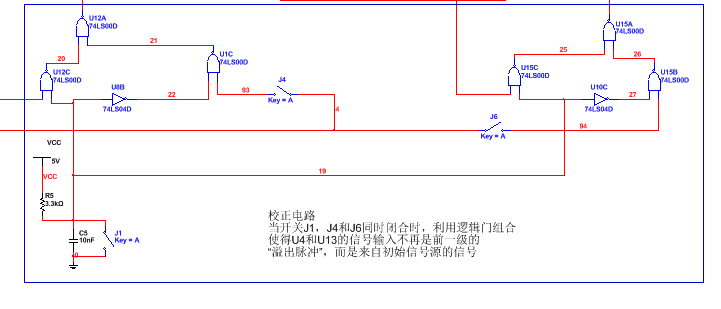

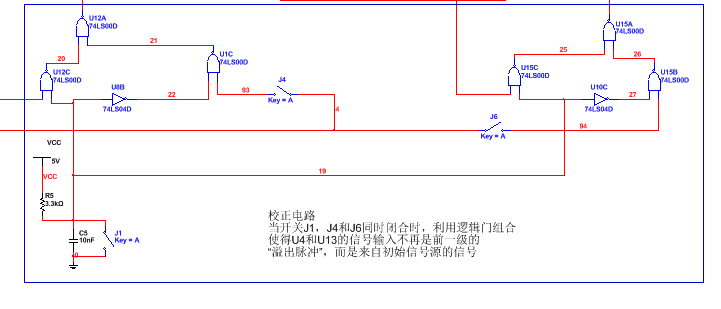

下面是校正电路,看电路注释就Ok啦,很简单的逻辑控制

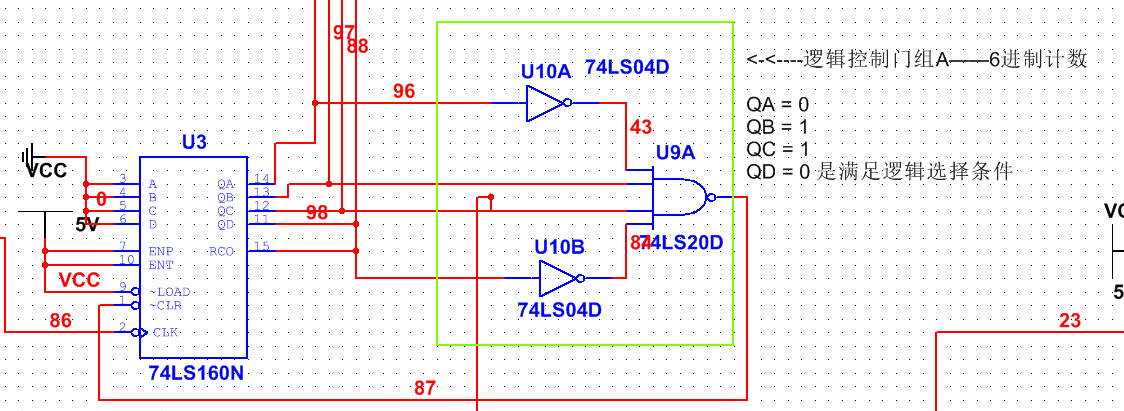

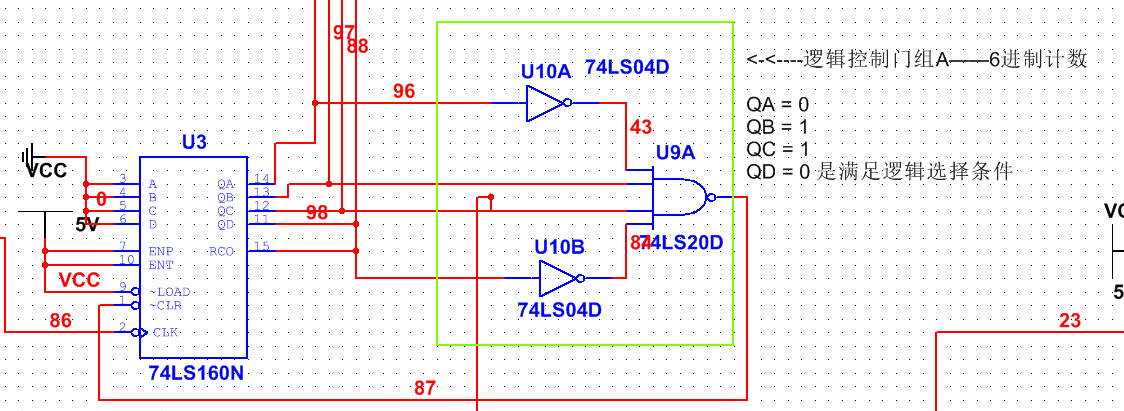

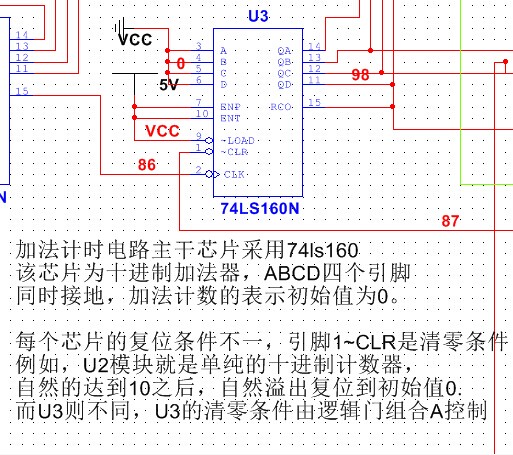

下面是采用清零法构建的6进制加法器,逻辑门组是实现的关键

都是泪....

进入正题,先给出整个仿真电路,然后对各个模块进行逐一分析.

下载文件基于multisim12制作,因此低于该版本的multisim无法打开,请注意使用multisim12:

下载链接:

http://download.csdn.net/detail/u011368821/8211361

不需要积分即可下载

电路概览:

信号发生模块,采用555timer的多谐振荡模式

该模式下的特点在电路注释中有说明.

如果忘记555timer怎么用的,下面是复习link

http://blog.csdn.net/cinmyheart/article/details/33362853

信号发生电路的产生信号提供给160十进制计数器

可以去这里看74ls160 74ls48z

http://blog.csdn.net/cinmyheart/article/details/26705425

下面是校正电路,看电路注释就Ok啦,很简单的逻辑控制

下面是采用清零法构建的6进制加法器,逻辑门组是实现的关键

相关文章推荐

- [原创]电路仿真设计multisim 14安装,破解,汉化教程

- 2015年全国大学生电子设计竞赛专题系列之综合测评-2015年Multisim仿真电路参考方案

- [原创]电路仿真设计multisim 14安装,破解,汉化教程

- 2015年全国大学生电子设计竞赛专题系列之综合测评-2013年Multisim仿真电路参考方案

- 2015年全国大学生电子设计竞赛专题系列之综合测评-2011年Multisim仿真电路参考方案

- 电路设计_13.56MHz RFID读写器天线的设计和仿真

- 数字电路期末课程设计总结(三)IIC总线调用

- 【搬家】FPGA学习手记(二) 简单功能仿真及Verilog基础电路设计

- 数字信号在不同时钟域间同步电路的设计

- 电子电路课程设计——8位数字抢答器设计论文

- 课程设计 电梯运行仿真

- 数字电路期末课程设计总结(一)

- 数字电路期末课程设计总结(二) ——超声波测距模块

- multisim V10.0 破解版 电路仿真软件

- 在windows XP下使用EWB50设计电路或者做仿真电路实验

- 课程设计:模拟时钟

- 利用定时器和数码管设计时钟

- 课程设计——数字通信计算机仿真:2PSK调制仿真

- 时钟使能电路的设计

- 通信系统课程设计电路调试之一《电平/幅度调整电路》