【笔记】DE2 硬件和处理器范例-2 External SRAM interface (DE2)(digital logic)(verilog hdl)

2011-03-31 14:43

603 查看

Introduction

本项目练习使用外部的61LV25616 SRAM,实现以下目标:用KEY0作为时钟输入,驱动一个4位的计数器,以产生一个地址码,然后在前面补充14个0扩展成18位的地址码。这个地址码作为存储器的地址在HEX4和绿色的LED上显示。 使用SWITCH[15:0]作为写入SRAM的数据。 使用KEY1作为写使能。注意写使能低电平有效,即按钮按下时。 在红色LED和HEX3-0上显示存储器总线(读或写)。 这个双向的总线可用以下语句配置读或写,注意在Altera的Cyclone II系列,只用FPGA的I/O引脚可作为三态设备。如果指定内部三态,将例化为多路选择器。

assign SRAM_DQ=(key[1]?16’hzzzz:SW[15:0]);

Design

IS61LV25616简介

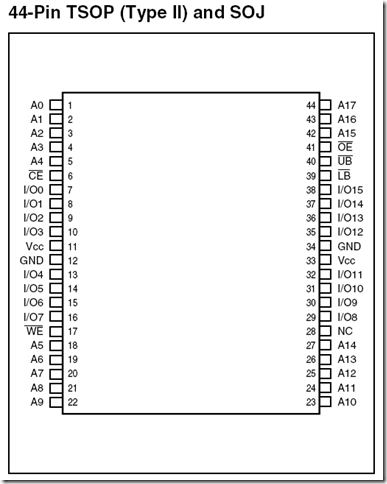

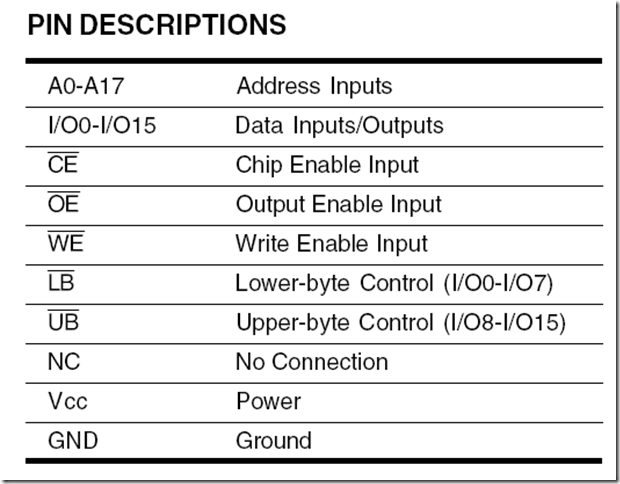

ISSI IS61LV25616是高速SRAM,容量为512KB。DE2上用的是TSOP封装的。引脚图和说明如下:

代码

1 //Top Module //project 2 External SRAM interface

2

3 module SRAM_IO(

4 input [1:0] KEY, //pushbutton [1:0]

5 input [15:0] SW, //toggle switch[15:0]

6 output [6:0] HEX0, //7-seg display

7 output [6:0] HEX1, //7-seg display

8 output [6:0] HEX2, //7-seg display

9 output [6:0] HEX3, //7-seg display

10 output [6:0] HEX4, //7-seg display

11 output [6:0] HEX5, //7-seg display

12 output [6:0] HEX6, //7-seg display

13 output [3:0] LEDG, //led green[3:0]

14 output [15:0] LEDR, //led red[15:0]

15 inout [15:0] SRAM_DQ, //SRAM data bus 16 bits

16 output [17:0] SRAM_ADDR, //SRAM address bus 18 bits

17 output SRAM_UB_N, //SRAM high-byte data mask

18 output SRAM_LB_N, //SRAM low-byte data mask

19 output SRAM_WE_N, //SRAM write enable

20 output SRAM_CE_N, //SRAM chip enable

21 output SRAM_OE_N //SRAM output enable

22 );

23

24 reg [3:0] shortCount;

25

26 assign HEX5=7'b011_1111; //-

27 assign HEX6=7'b011_1111; //-

28 assign HEX6=7'b011_1111; //-

29

30 //memeory address

31 //connect KEY0 switch to led to upcount and display

32 always @(negedge KEY[0])

33 begin

34 shortCount<=shortCount+1;

35 end

36 assign LEDG[3:0]=shortCount;

37 //display the hex value of the short counter

38 //this is also the memory address

39 HexDigit Digit4(HEX4,shortCount);

40

41 //SRAM Interface

42 assign SRAM_ADDR={14'h0,shortCount}; //SRAM Address bus 18 bits

43 assign SRAM_UB_N=0; //hi byte select enabled

44 assign SRAM_LB_N=0; //lo byte select enabled

45 assign SRAM_CE_N=0; //chip is enabled

46 assign SRAM_WE_N=KEY[1]; //write when KEY1 is pressed

47 assign SRAM_OE_N=0; //output enable is overidden by WE

48 //if KEY1 is not pressed, then float bus, so that SRAM can drive it (read)

49 //if KEY1 is pressed, drive it with data from SW[15:0] to be stored in SRAM (write)

50 assign SRAM_DQ=(KEY[1]?16'hzzzz:SW[15:0]);

51 //show memory on the LEDs and 7-seg display

52 assign LEDR[15:0]=SRAM_DQ;

53 HexDigit Digit0(HEX0,SRAM_DQ[3:0]);

54 HexDigit Digit1(HEX1,SRAM_DQ[7:4]);

55 HexDigit Digit2(HEX2,SRAM_DQ[11:8]);

56 HexDigit Digit3(HEX3,SRAM_DQ[15:12]);

57

58 endmodule1 //Decode one hex digit for LED 7-seg display 2 3 module HexDigit(segs,num 4 //input [3:0] num, 5 //output reg [6:0] segs 6 ); 7 input [3:0] num; 8 output [6:0] segs; 9 reg [6:0] segs; 10 11 always @(num) 12 begin 13 case(num) 14 4'h0: segs = 7'b1000000; 15 4'h1: segs = 7'b1111001; 16 4'h2: segs = 7'b0100100; 17 4'h3: segs = 7'b0110000; 18 4'h4: segs = 7'b0011001; 19 4'h5: segs = 7'b0010010; 20 4'h6: segs = 7'b0000010; 21 4'h7: segs = 7'b1111000; 22 4'h8: segs = 7'b0000000; 23 4'h9: segs = 7'b0010000; 24 4'ha: segs = 7'b0001000; 25 4'hb: segs = 7'b0000011; 26 4'hc: segs = 7'b1000110; 27 4'hd: segs = 7'b0100001; 28 4'he: segs = 7'b0000110; 29 4'hf: segs = 7'b0001110; 30 default segs = 7'b1111111; 31 endcase 32 end 33 34 endmodule

Results and Analysis

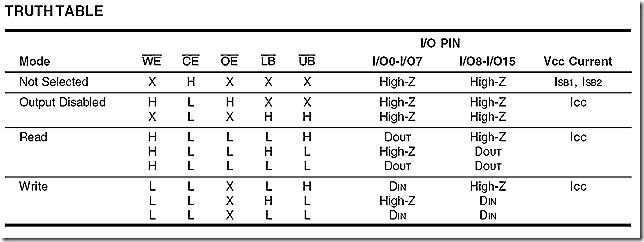

经下载测试,按KEY0来产生一个时钟脉冲,驱动4位的计数器,计数输出显示在HEX4和绿色的LED上。当没按下KEY1时,HEX3-0的显示是浮动的,这时SRAM执行的读操作,按下KEY1,HEX3-0显示当前SW[15:0]的值,当然同样的值也显示在红色的LED上,这时为写SRAM。由上面的真值表可知通过KEY1控制WE的高低,进而控制读写。都由assign SRAM_WE_N=KEY[1];

assign SRAM_DQ = (KEY[1]? 16'hzzzz : SW[15:0]);

实现。

Conclusion

因为本例采用按KEY0产生时钟脉冲的方法来验证SRAM的读写操作。大大简化了时序控制的问题。IS61LV25616共7种端口,16位的双向的数据总线SRAM_DQ;18位的地址总线SRAM_ADDR;高/低8位标记SRAM_UB_N和SRAM_LB_N;读写使能SRAM_WE_N;片选使能SRAM_CE_N;输出使能SRAM_OE_N;标识符里的_N表示低电平有效。本例比较投机的地方就是关于4位计数器生成的地址码,总共16个地址码,便于验证,可每按一次KEY0,设置一次SW[15:0]作为输入数据,再按一次KEY1记录当前数据。连续记录16个数据后,可通过按KEY0观察HEX3-0的输出。Reference

1> 61LV25616_SRAM data sheet2> ECE 576 Cornell University

3> Terasic’s DE2 user manual and code example

相关文章推荐

- ALTERA DE2 之 verilog HDL 学习笔记04 -altera DE2 上 SRAM的读写

- 【笔记】关于整数分频的思考(Verilog HDL)(Digital Logic)

- 【笔记】Verilog HDL 关键词【Verilog HDL】

- ALTERA DE2 之 verilog HDL 学习笔记05-FPGA UART RS232

- Verilog HDL那些事_建模篇笔记(实验三:按键消抖)

- Verilog HDL那些事_建模篇笔记(实验七:数码管电路驱动)

- Verilog HDL学习笔记1

- 【原创】如何使用DE2的1602LCD --之一(quartus)(verilog)(digital logic)

- Verilog HDL 学习笔记1-data type

- 操作系统课堂笔记(2)操作系统的硬件环境之中央处理器

- ALTERA DE2 之 verilog HDL 学习笔记03 FPGA的PWM输出

- Verilog 初学笔记--顺序操作 和 并行操作的一点思考(参考黑金教程:Verilog HDL那些事 建模篇)

- Quartus II 与ModelSim的学习笔记(三)——Verilog HDL基础语法

- 自己动手写处理器之第二阶段(2)——Verilog HDL简介

- (原创)DE2范例中Reset_Delay.v模块的作用探讨(Verilog)(DE2)

- 【原创】DE2 实验练习解答—lab4 counters【verilog】【digital logic】

- ALTERA DE2 之 verilog HDL 学习笔记02 - 数码管

- Verilog HDL那些事_建模篇笔记(实验八:键盘解码)

- Verilog HDL 学习笔记3-Latch

- (笔记)Quartus II 与 DE2 入门指导(Digital Logic)(DE2)