并行硬件技术概览:多处理器、超线程、双核、多核与FPGA

2010-12-03 20:29

369 查看

并行硬件正在成为计算机处理技术中广为应用的一部分。本文将为您讲解当今市场所提供的常见并行硬件架构之间的差别,包括多处理器、超线程、双核、多核和FPGA等。

超线程

双核与多核处理器

FPGA

LabVIEW如何对并行硬件进行编程

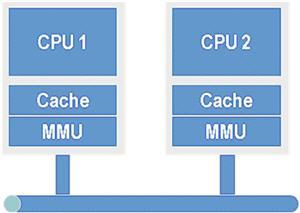

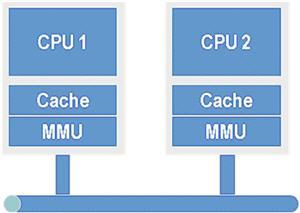

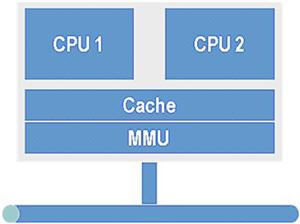

图1。多处理器系统具有远程互联结构的独立高速缓存与MMU内存管理单元。

多处理器系统的复杂度低于多核系统,因为它们本质是互连在一起的单芯片CPU。多处理器系统的不足在于其高昂的价格,因为它们需要多个芯片,这比单芯片解决方案要昂贵得多。

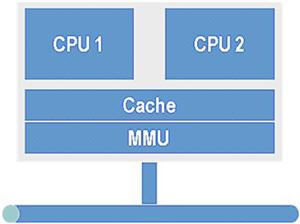

图2。多核处理器共享具有短程互联结构的高速缓存和MMU内存管理单元。

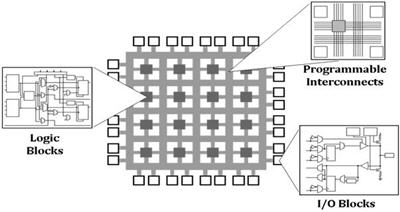

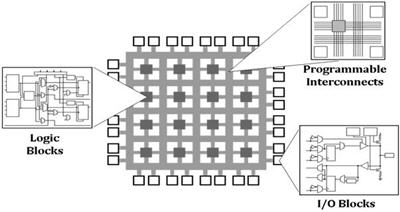

图3。 FPGA,逻辑单元、可编程互联、I/O模块

FPGA是由三个基本组件构成的可编程芯片。首先,在逻辑模块中,数据被计算并处理以得到分析结果。其次,通过将信号从一个逻辑单元路由至下一个单元的可编程互联,实现逻辑组块的互相联通。第三,I/O组块与芯片的管脚相连,以提供与外围电路的双向通信。

由于FPGA以并行的方式运行,所以它支持用户创建任意多的任务专用核,所有这些任务专用核以类似于并行电路的方式运行于FPGA芯片中。FPGA逻辑门的并行特质支持非常高的数据吞吐量,更是远胜于与其相对应的微处理器。

目录

多处理器(Multiprocessor)超线程

双核与多核处理器

FPGA

LabVIEW如何对并行硬件进行编程

多处理器(Multiprocessor)

多处理器(Multiprocessor)系统由不同芯片上的多个处理器组成。多处理器系统因IT服务器的应用在上世纪九十年代得以普及。在当时,它们是可以插入机架服务器的处理器主板。现在,多处理器系统可以构建在同一块电路板上,处理器之间通过一个高速通信接口连接。

图1。多处理器系统具有远程互联结构的独立高速缓存与MMU内存管理单元。

多处理器系统的复杂度低于多核系统,因为它们本质是互连在一起的单芯片CPU。多处理器系统的不足在于其高昂的价格,因为它们需要多个芯片,这比单芯片解决方案要昂贵得多。

超线程

超线程是由Intel公司引入的一项技术,其主要目的在于改善对多线程代码的支持。奔腾4处理器就是一例实现超线程技术的CPU。双核与多核处理器

双核处理器是指单个芯片上有两个CPU,而多核处理器则是指在单个芯片上包含任意多个(如2、4或8)CPU的处理器。多核处理器的挑战在于软件开发部分。系统性能提升的多少直接与通过多线程编程源代码的并行程度有关。

图2。多核处理器共享具有短程互联结构的高速缓存和MMU内存管理单元。

FPGA

FPGA(现场可编程门阵列)是一种由逻辑门组成的硅片,被视为具有极佳并行处理能力的硬件设备,非常适合高性能计算与海量数据处理,如数字信号处理(DSP)应用。FPGA的运行时钟低于微处理器,但功耗较高。

图3。 FPGA,逻辑单元、可编程互联、I/O模块

FPGA是由三个基本组件构成的可编程芯片。首先,在逻辑模块中,数据被计算并处理以得到分析结果。其次,通过将信号从一个逻辑单元路由至下一个单元的可编程互联,实现逻辑组块的互相联通。第三,I/O组块与芯片的管脚相连,以提供与外围电路的双向通信。

由于FPGA以并行的方式运行,所以它支持用户创建任意多的任务专用核,所有这些任务专用核以类似于并行电路的方式运行于FPGA芯片中。FPGA逻辑门的并行特质支持非常高的数据吞吐量,更是远胜于与其相对应的微处理器。

相关文章推荐

- 如何查看有几个处理器,是否多核?是否超线程?

- 超线程 多核 多处理器区别

- 转:Linux网络IO并行化技术概览

- 超线程 多核 多处理器区别

- 双头(多头)显示技术,多点触摸技术和双核,三核,四核(多核)CPU结合将极大促进多人共享一台电脑的应用

- 双核的时代的到来恐怕你不得不了解的技术------并行

- 为什么说FPGA是硬件并行的?

- 如何查看有几个处理器,是否多核?是否超线程?

- Linux网络IO并行化技术概览

- 一起谈.NET技术,.NET 4 并行(多核)编程系列之一入门介绍

- 超线程、多核、多处理器

- 一起谈.NET技术,.NET 4 并行(多核)编程系列之二 从Task开始

- 一起谈.NET技术,.NET并行(多核)编程系列之七 共享数据问题和解决概述

- ABAP开发工具及技术概览

- Unity渲染教程(十九):图形处理器的实例化技术

- Unix/Linux下C/C++开发技术概览

- .NET 4 并行(多核)编程系列之三 从Task的取消

- 【技术类】ArcGIS影像技术之镶嵌数据集概览

- 硬件系统设计:该用FPGA来做呢还是用单片机?

- vivado----fpga硬件调试 (五) ----找不到ila核问题及解决