【翻译】在Verilog设计中使用参数化模块库(Quartus II)(Verilog)

2010-05-17 17:28

393 查看

本文介绍如何在Quartus II里使用Altera的模块库。

参数化模块库

使用LPM的扩展电路(Arguemented Circuit)

扩展设计的结果

实际设计中经常包含通用的电路块,比如:加法器、减法器、乘法器、译码器、计数器和移位寄存器。Altera以模块库的

形式提供这些电路块,可在Verilog设计中例化。编译器可以识别模块库里用Verilog代码指定的标准功能,这样就会自动推断这个模块。但是,很多模块库提供太复杂的功能而不能被自动识别。这些模块必须被用户在设计里明确的例化。

Quartus II包含一个参数化的模块库(LPM)。这些模块采用通用结构,并且需要修该指定的参数值来实现指定的应用。

完成本文,读者将学会:

参数化的模块库(LPMs)

在电路里配置一个LPM

在设计电路里例化一个LPM

本文范例的细节由Quartus II 9.1截取,其他版本类似。

an-1an-2…a0和B=bn-1bn-2…b0,主要的输出是Z=zn-1zn-2…z0。另一个输入是控制信号AddSub,当AddSub

=0时Z=A+B;当AddSub=1时,Z=A-B.第2个输入控制信号Sel被用来选择运算模式的操作。当Sel=0时,Z=A+-B;

当Sel=1时,B被从当前Z的值加到或减去。如果加法或减法操作的结果溢出,一个输出信号Overflow被激活。

为了较容易处理异步输入信号,在时钟上升沿它们被加载到触发器。因此,输入A和B将被加载到寄存器Areg和Breg,

而Sel和AddSub将被加载到触发器SelR和AddSubR。加/减器电路的结果放在寄存器Zreg。

代码

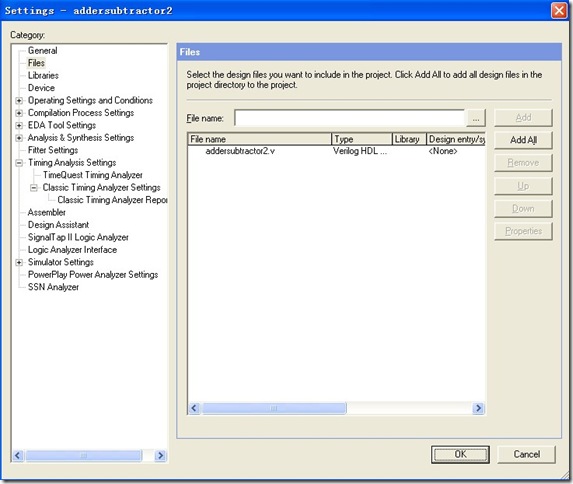

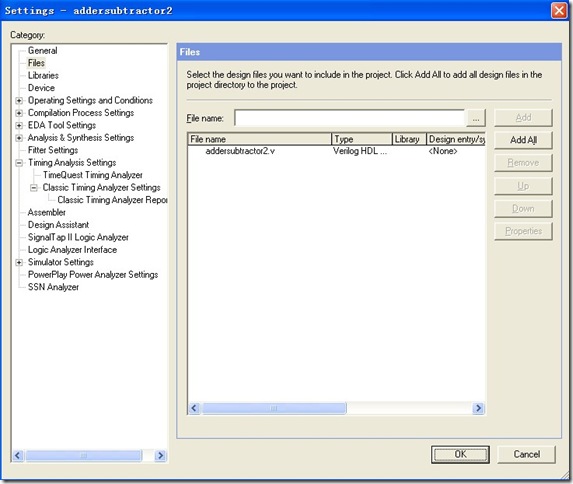

添加megaddsub.v到工程。选择Porject > Add/Remove Files in Project(图13)。文件addersubtractor2.v已经存在,添加megaddsub.v,单击Ok。

图 13

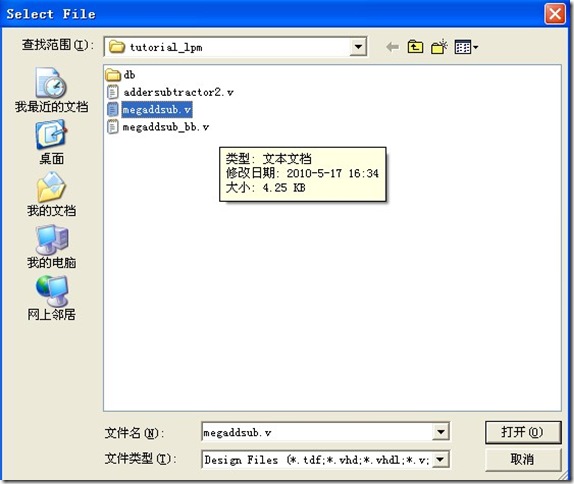

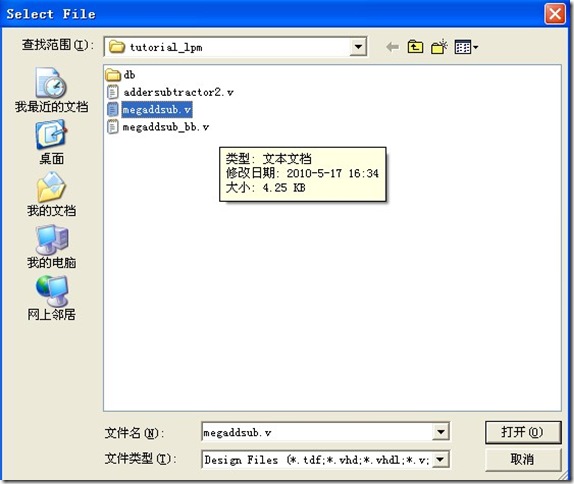

图 14

计中使用LPM,优势比较明显。当有合适的LPM时,建议使用。

图 15

Contents:

范例电路参数化模块库

使用LPM的扩展电路(Arguemented Circuit)

扩展设计的结果

实际设计中经常包含通用的电路块,比如:加法器、减法器、乘法器、译码器、计数器和移位寄存器。Altera以模块库的

形式提供这些电路块,可在Verilog设计中例化。编译器可以识别模块库里用Verilog代码指定的标准功能,这样就会自动推断这个模块。但是,很多模块库提供太复杂的功能而不能被自动识别。这些模块必须被用户在设计里明确的例化。

Quartus II包含一个参数化的模块库(LPM)。这些模块采用通用结构,并且需要修该指定的参数值来实现指定的应用。

完成本文,读者将学会:

参数化的模块库(LPMs)

在电路里配置一个LPM

在设计电路里例化一个LPM

本文范例的细节由Quartus II 9.1截取,其他版本类似。

1. 范例电路

作为范例,我们使用图1所示的加/减器电路。它可以加、减,并以2的补码表示运算n-bit的数。2个主要的输入是数A=an-1an-2…a0和B=bn-1bn-2…b0,主要的输出是Z=zn-1zn-2…z0。另一个输入是控制信号AddSub,当AddSub

=0时Z=A+B;当AddSub=1时,Z=A-B.第2个输入控制信号Sel被用来选择运算模式的操作。当Sel=0时,Z=A+-B;

当Sel=1时,B被从当前Z的值加到或减去。如果加法或减法操作的结果溢出,一个输出信号Overflow被激活。

为了较容易处理异步输入信号,在时钟上升沿它们被加载到触发器。因此,输入A和B将被加载到寄存器Areg和Breg,

而Sel和AddSub将被加载到触发器SelR和AddSubR。加/减器电路的结果放在寄存器Zreg。

代码

//Top-level module module addersubtractor2(A,B,Clock,Reset,Sel,AddSub,Z,Overflow); parameter n=16; input [n-1:0]A,B; input Clock,Reset,Sel,AddSub; output [n-1:0]Z; output Overflow; reg SelR,AddSubR,Overflow; reg [n-1:0]Areg,Breg,Zreg; wire [n-1:0]G,M,Z; wire over_flow; //Define combinational logic circuit mux2to1 multiplexer(Areg,Z,SelR,G); defparam multiplexer.k=n; megaddsub nbit_adder(~AddSubR,G,Breg,M,over_flow); assign Z=Zreg; //Define flip-flop and register always @(posedge Reset or posedge Clock) if(Reset==1) begin Areg<=0; Breg<=0; Zreg<=0; SelR<=0; AddSubR<=0; Overflow<=0; end else begin Areg<=A; Breg<=B; Zreg<=M; SelR<=Sel; AddSubR<=AddSub; Overflow<=over_flow; end endmodule //k-bit 2-to-1 multiplexer module mux2to1(V,W,Selm,F); parameter k=8; input [k-1:0]V,W; input Selm; output [k-1:0]F; reg [k-1:0]F; always @(V or W or Selm) if(Selm==0) F=V; else F=W; endmodule

添加megaddsub.v到工程。选择Porject > Add/Remove Files in Project(图13)。文件addersubtractor2.v已经存在,添加megaddsub.v,单击Ok。

图 13

图 14

4 结果

编译设计,查看总结,图15.注意修改后的电路使用52个le。因为本例比较简单,使用LPM的优势并不明显。在更复杂的设计中使用LPM,优势比较明显。当有合适的LPM时,建议使用。

图 15

Seealso

Using Library Modules in Verilog Designs相关文章推荐

- [文档].艾米电子 - 使用Verilog设计的Quartus II入门指南

- Quartus II 中参数化模块库(LPM)的使用

- (转)如何使用SignalTap II觀察reg與wire值? (SOC) (Verilog) (Quartus II) (SignalTap II)

- 使用sqlite3(数据库知识)的接口函数完成一个用户注册功能模块设计 要封装成函数,在独立的main中调用测试

- 使用sqlite3的接口函数完成一个用户登录验证功能模块设计 要封装成独立函数,在独立的main中调用测试;

- 如何高效使用和管理Bitmap--图片缓存管理模块的设计与实现

- 我脑残实验室Verilog学习笔记——在Xilinx ISE中运用符号设计顶层模块的方法

- 转[翻译]案例学习:仅使用Redis+PHP设计实现一个简单的Twitter

- 翻译:在我们使用的NET FRAMEWORK类库中发现设计模式(3)

- 高性能可扩展mysql(用户模块设计,分区表使用)

- Android SDK开发指南(翻译)系列三:Tools(一)--使用AIDL, 设计一个远程接口

- 参数化模块设计技术

- 如何使用SignalTap II觀察reg與wire值? (SOC) (Verilog) (Quartus II) (SignalTap II)

- 【翻译】使用Ext JS设计响应式应用程序

- [文档].艾米电子 - 使用Verilog设计的ModelSim入门指南

- USING INDUCTION TO DESIGN 使用归纳法设计算法【全文翻译】

- 在iOS4中使用代码块-代码块设计(二)(翻译)

- verilog语言RS232串口发送模块设计——采集ps2键盘数据在串口调试工具显示

- mojoportal学习——文章翻译之不同的模块使用不同的风格

- 使用Flask设计带认证token的RESTful API接口[翻译]