【实验】简单实时300点采样逻辑

2009-08-29 20:33

435 查看

工程文件: /Files/lwpo2008/SampleLogicRealTime.rar

1module SampleLogicRealTime(

2 input rst_n,

3 input iclk,

4 input trig,

5 output oclk

6 );

7

8parameter IDLE = 2'b01,

9 SAMPLE = 2'b10;

10

11parameter LENGTH = 9'd300;

12

13reg [1:0] current_state, //state

14 next_state;

15

16reg r_data_in0, //detect the risingedge reg

17 r_data_in1,

18 o_rising_edge;

19

20reg [8:0] count; //count for delay

21reg count_rst_n;

22

23// sequential circuit

24always@(posedge iclk, negedge rst_n) begin

25 if (!rst_n) begin

26 current_state <= IDLE;

27 end

28 else begin

29 current_state <= next_state;

30 end

31end

32// combinational circuit for state logic

33always@(current_state,count,o_rising_edge) begin

34 next_state = IDLE;

35

36 case (current_state)

37 IDLE : next_state = o_rising_edge ? SAMPLE : IDLE;

38 SAMPLE : next_state = (count >= LENGTH) ? IDLE : SAMPLE;

39 endcase

40end

41

42assign oclk = (count_rst_n ==1'b0)? 1'b0 : iclk;

43// combinational circuit for output logic

44always@(current_state,iclk) begin

45

46 case (current_state)

47 IDLE : begin

48 count_rst_n <= 1'b0;

49 end

50 SAMPLE : begin

51 count_rst_n <= 1'b1;

52 end

53 endcase

54end

55

56//detect the rising edge

57always@(posedge iclk) begin

58 r_data_in0 <= r_data_in1;

59 r_data_in1 <= trig;

60end

61always@(r_data_in0,r_data_in1) begin

62 o_rising_edge = ~r_data_in0 & r_data_in1; //o_rising_edge output

63end

64

65//counter

66always@(posedge iclk) begin

67 if(~count_rst_n)

68 count <= 9'b0_0000_0000;

69 else

70 count <= count + 1'b1;

71end

72

73endmodule

74

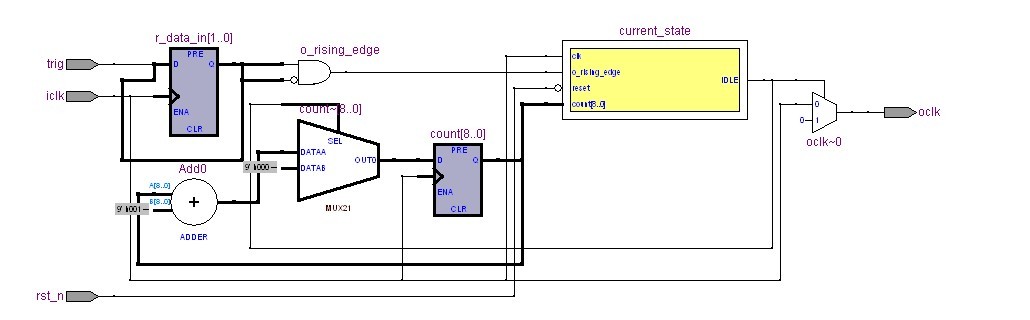

RTL图:

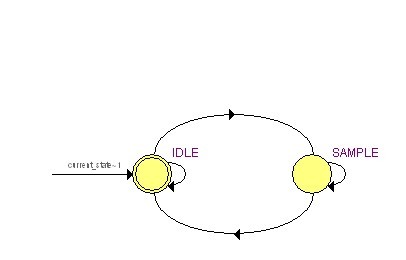

状态转换图:

1module SampleLogicRealTime(

2 input rst_n,

3 input iclk,

4 input trig,

5 output oclk

6 );

7

8parameter IDLE = 2'b01,

9 SAMPLE = 2'b10;

10

11parameter LENGTH = 9'd300;

12

13reg [1:0] current_state, //state

14 next_state;

15

16reg r_data_in0, //detect the risingedge reg

17 r_data_in1,

18 o_rising_edge;

19

20reg [8:0] count; //count for delay

21reg count_rst_n;

22

23// sequential circuit

24always@(posedge iclk, negedge rst_n) begin

25 if (!rst_n) begin

26 current_state <= IDLE;

27 end

28 else begin

29 current_state <= next_state;

30 end

31end

32// combinational circuit for state logic

33always@(current_state,count,o_rising_edge) begin

34 next_state = IDLE;

35

36 case (current_state)

37 IDLE : next_state = o_rising_edge ? SAMPLE : IDLE;

38 SAMPLE : next_state = (count >= LENGTH) ? IDLE : SAMPLE;

39 endcase

40end

41

42assign oclk = (count_rst_n ==1'b0)? 1'b0 : iclk;

43// combinational circuit for output logic

44always@(current_state,iclk) begin

45

46 case (current_state)

47 IDLE : begin

48 count_rst_n <= 1'b0;

49 end

50 SAMPLE : begin

51 count_rst_n <= 1'b1;

52 end

53 endcase

54end

55

56//detect the rising edge

57always@(posedge iclk) begin

58 r_data_in0 <= r_data_in1;

59 r_data_in1 <= trig;

60end

61always@(r_data_in0,r_data_in1) begin

62 o_rising_edge = ~r_data_in0 & r_data_in1; //o_rising_edge output

63end

64

65//counter

66always@(posedge iclk) begin

67 if(~count_rst_n)

68 count <= 9'b0_0000_0000;

69 else

70 count <= count + 1'b1;

71end

72

73endmodule

74

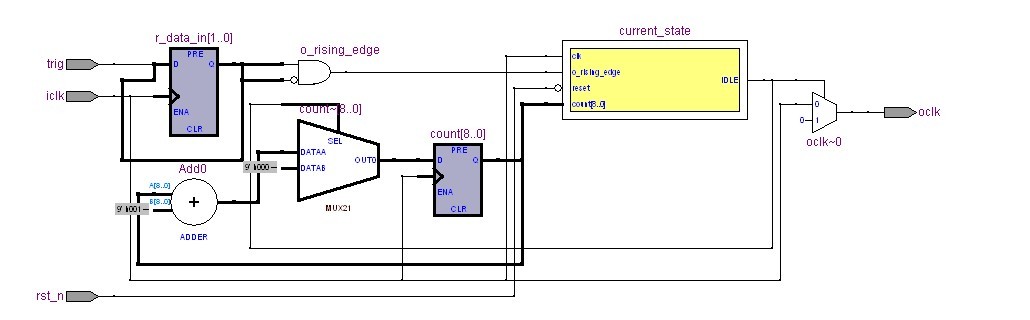

RTL图:

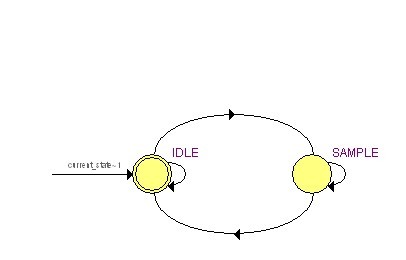

状态转换图:

相关文章推荐

- 一个简单的ADC采样实验。

- 简单实验

- SQL server 2000和SQL Server 2005的各个逻辑步骤的简单描述

- 实验一,简单的C++程序

- 简单记录,采样频率更改。

- MapReduce实验:HBase安装以及简单操作

- java多线程简单实验

- 理解JAVA程序逻辑及面向对象编程思想简单总结(2)

- 实验1 简单的C++程序(P276)

- 【iOS开展-50】使用它来创建一个新的类的实现代码包,因此,不自觉地练习简单MVC实验,附带动画

- 虚拟环境下搭建hadoop之三——启动hadoop并简单实验

- 20145315 20145304《信息安全系统设计基础》实验三 实时系统的移植

- 关于Cisco一个简单实验拓扑配置搭建与配置

- keepalived 的简单应用――管理VIP的飘动---待实验

- Android简单实现实时监听网络状态

- asp.net mvc 实现简单的实时消息推送

- 模拟简单进程调度实验

- 物理地址和逻辑地址区别(简单理解)

- 自制浮动静态路由实验(简单)

- 20145305 《信息安全系统设计基础》实验三 实时系统的移植